基于FPGA的HDMI_CEC设计与实现

孙 玲,刘文杰,施 佺,蒋 斌,2

(1.南通大学 江苏省专用集成电路设计重点实验室,江苏 南通226007;2.苏州国芯科技有限公司,江苏 苏州215011)

随着技术的更新和高清晰度视频设备(High Definition Television,HDTV)市场需求的提升,高清晰度多媒体接口(High-Definition Multimedia Interface,HDMI)已被广泛用于各类消费电子设备中[1-6]。与此同时,消费电子控制(Consumer Electronic Control,CEC)作为一种面向HDMI的自动控制总线被应用于HDMI接口系统中,该技术由欧洲的SCART接口改进发展而来,目前呈现出应用范围不断扩大的趋势。不同的厂商赋予CEC技术不同的名字,例如松下电器(Panasonic)的VIERALINK,三星电子(Samsung)的ANYNET+,LG电子的SIMPLINK等,国内的厦华电子[7]也有类似设计。

CEC总线是一种符合音视频传输标准的串行双向控制总线[8-9]。它由一根控制总线连接网络内多个支持CEC功能的音视频设备,远程控制设备的音视频功能,同时也支持CEC设备内部的通信而无需用户的直接参与,因此,能够实现用一个遥控器来控制多个HDMI连接的视听设备,从而减少系统内的遥控器数量。它所能实现的功能有一键播放(One Touch Play)、系统待机(System Standby)、一键录像(One Touch Record)等[10]。本文研究了一种CEC总线的设计方案,并采用可综合的Verilog HDL语言实现了该功能电路的逻辑综合与仿真验证。

1 CEC通信协议简介

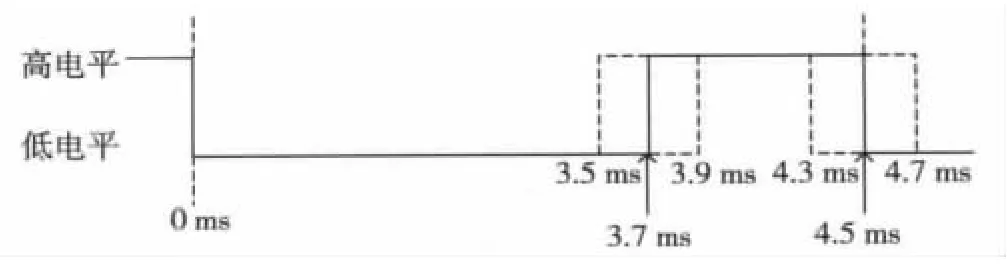

CEC系统在发送信息时由一个发送端和一个或数个接收端组成。发送端负责发送消息,而接收端将接收所有数据并作出相应的应答。发送消息时首先发送一个起始位,接着是一个或数个数据块。起始位时长为4.5 ms,且低电平的宽度为3.7 ms,并允许在一定区间内浮动,时序图如图1所示[10]。

图1 起始位时序图

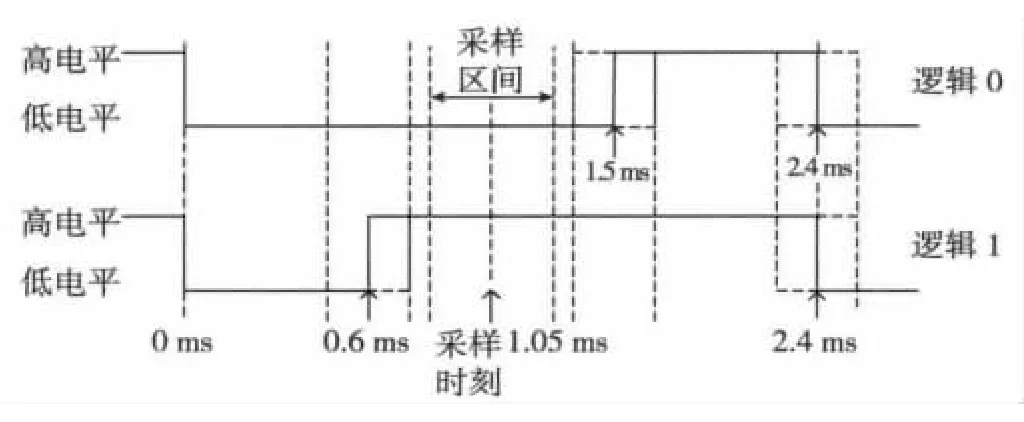

数据位分为逻辑“0”和逻辑“1”两种,时长均为2.4 ms。逻辑“0”的低电平宽度为1.5 ms,逻辑“1”的低电平宽度为0.6 ms,如图2所示。其中1.05 ms时刻为采样区的采样时刻。

引导块和数据块均含有10 bit信息且结构相同,如图3所示。当表示引导块时,高4位(7~4)表示发送端逻辑地址,随后4位(3~0)为接收端逻辑地址;表示数据块时,高8位(7~0)数据为操作码或操作数。EOM为逻辑“0”时,则表示消息发送未完成;若为逻辑“1”则表示消息发送结束。ACK位为应答位,当发送的目的地址为非广播地址时,发送端总是将此位置为逻辑“1”,接收端成功接收到消息之后,则将该位改置为逻辑“0”,其他设备不做应答;若发送的目的地址为广播地址,该位被置为逻辑“0”时表示有一个或数个接收端拒绝接收消息,反之则同意接收。

图2 数据位逻辑“1”和逻辑“0”的时序图

图3 引导块与数据块结构示意图

CEC协议通过重发机制、错误检测机制和帧有效机制3种传输机制以保证数据的有效传输。发送端发送数据后,如果未能得到接收端传来的正确的应答信号时启动重发机制,且重发次数不超过5次;接收端接收到有效起始位后启动错误检测机制,若接收端接收到的数据信号的长度未落在协议规定的信号时间长度内,则反馈给发送端1.4~1.6倍的普通数据比特时间长度的低电平;帧有效机制是指接收端接收到的操作数与所要求的操作数的长度不相符时将丢弃该帧。

当系统中存在多个模块同时传输信息时,将在发送引导块的发送端逻辑地址时间区间内对总线的获取实施仲裁机制,以确定哪个设备获得总线的占用权。仲裁机制判断标准为:若发送的是高电平而总线上是低电平,则该模块失去了仲裁,反之,则获得总线的占用权。此外,发送数据时还需要遵循信号空闲原则,同一设备再发送帧需等待大于等于7个普通数据时间长度,新设备发送帧需等待大于等于5个普通数据时间长度,发送失败重发帧需等待大于等于3个时间长度。

2 CEC设计与实现

2.1 CEC顶层设计

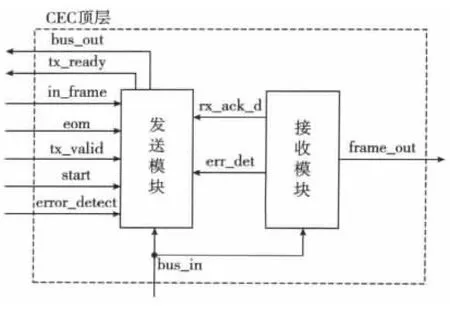

CEC模块总体设计如下图4所示。图中,发送模块接收需要发送的数据并经bus_out端口发送出去;接收模块将接收到的数据还原输出,并将信号rx_ack_d和err_det传到发送模块使其发送应答信号。信号tx_ready和tx_valid为CEC模块与传送数据的数据存储模块之间的握手信号,其中tx_ready为CEC发送准备信号,tx_valid表示数据存储模块的有效信号,当两个信号同时有效时,数据由in_frame端输入。eom为发送帧中需要的EOM位数据信息;start表示帧起始位信号;err_detect表示接收端接收到错误信号的反馈信号;frame_out表示作为接收端时输出接收到的信号;bus_out与bus_in为同一根双向串行总线。

图4 CEC模块总体设计示意图

CEC工作时可能处在的状态有3种,即等待状态、发送状态和接收状态。其中,等待状态表示该模块等待本地发送请求或接收数据的过程。发送状态和接收状态工作流程分别如下所述。

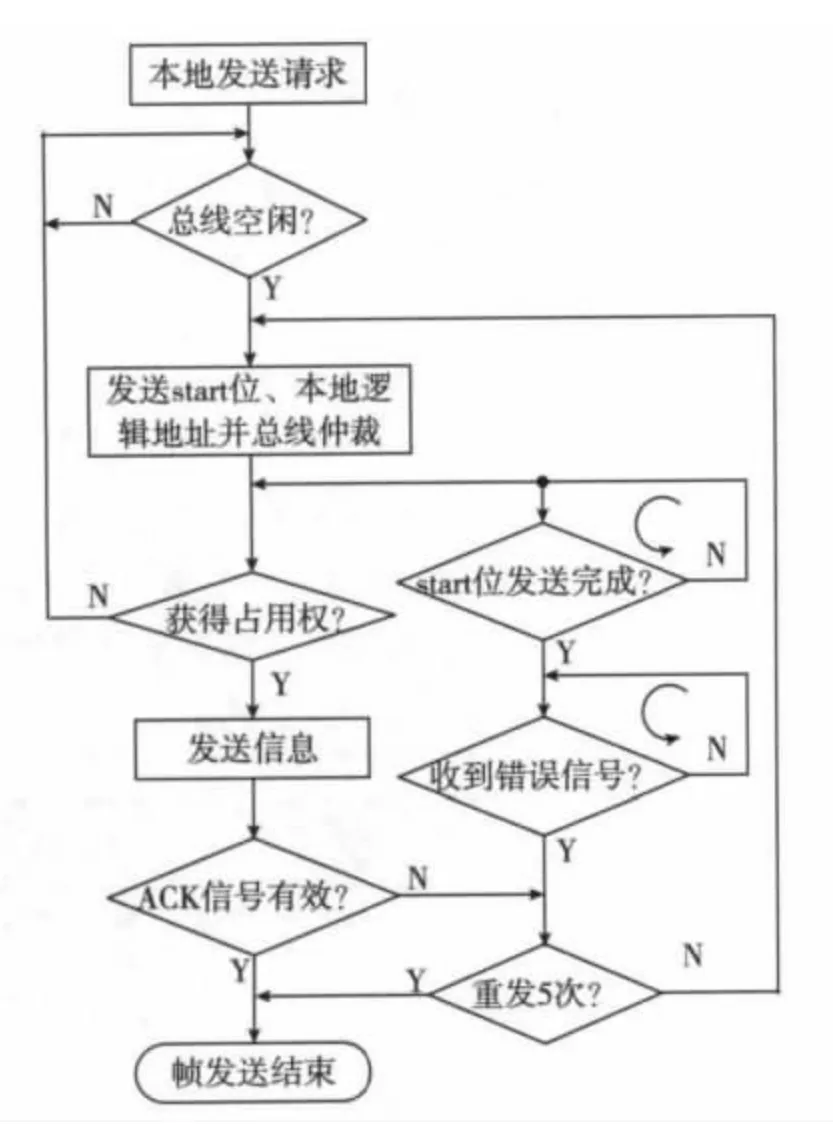

图5所示为CEC在发送状态下发送一个数据块的流程图。首先由本地设备发出发送请求,若总线空闲时间满足要求则表示总线处于空闲状态,发送模块接收来自本地的信息并开始发送,否则继续等待直到总线空闲。当总线空闲时向总线发送信息并启动总线仲裁功能,同时启动是否收到错误信号检测模块。一方面,start位未发送完成持续等待,当其发送完成后错误信号检测模块检测到错误信号时,返回发送端重新发送,并且重发次数不能大于5次,若大于5次则本次发送请求失败。另一方面,总线仲裁模块检测是否获得总线占用权,若本地没有获得总线占用权则返回到总线空闲判断状态等待再发送;若获得总线占用权则发送信息。当发送到引导块或数据块的ACK位时判断该位是否有效,若有效,则本次发送请求成功,帧发送结束;反之则将启动重发功能。此时的重发次数与之前是否收到错误信号检测的重新次数之和不能大于5次,同样,若大于5次则本次发送请求失败。

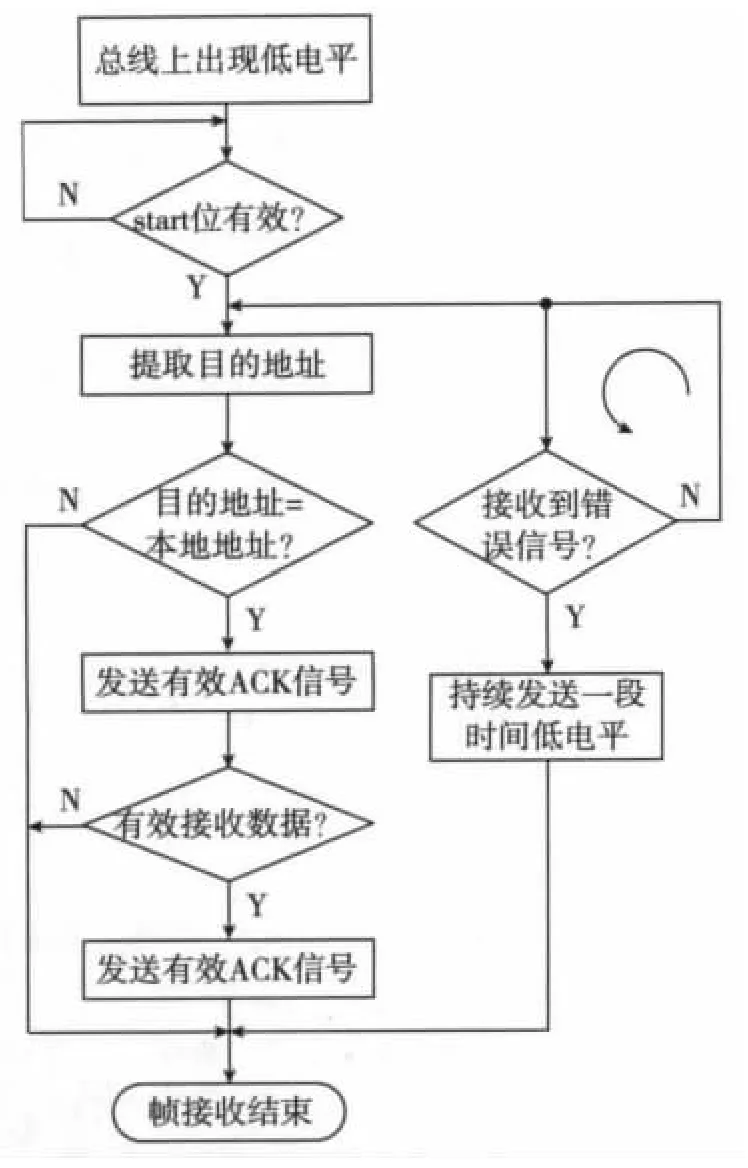

图6所示为CEC在接收状态下接收数据块的流程图。首先,接收端持续监测总线上电平变化,当总线上出现低电平时立即检测start位的信息是否有效,若无效则继续监测。当接收到有效的start位信息后,一方面,是否接收到错误信号检测模块不间断检测总线上信号是否正确,一旦检测到错误信号则持续发送一段时间低电平信号以告知发送端停止发送,然后结束本帧接收。另一方面,当接收到一有效的start位后,在安全采样区间内采样还原目的地址信息并与本地逻辑地址比较。若两个地址不相同则结束本次接收;若两个地址相同,则继续接收并在相应时刻发送有效ACK信号直到本帧接收结束。

图5 发送状态发送流程图

图6 接收状态接收流程图

2.2 发送模块设计

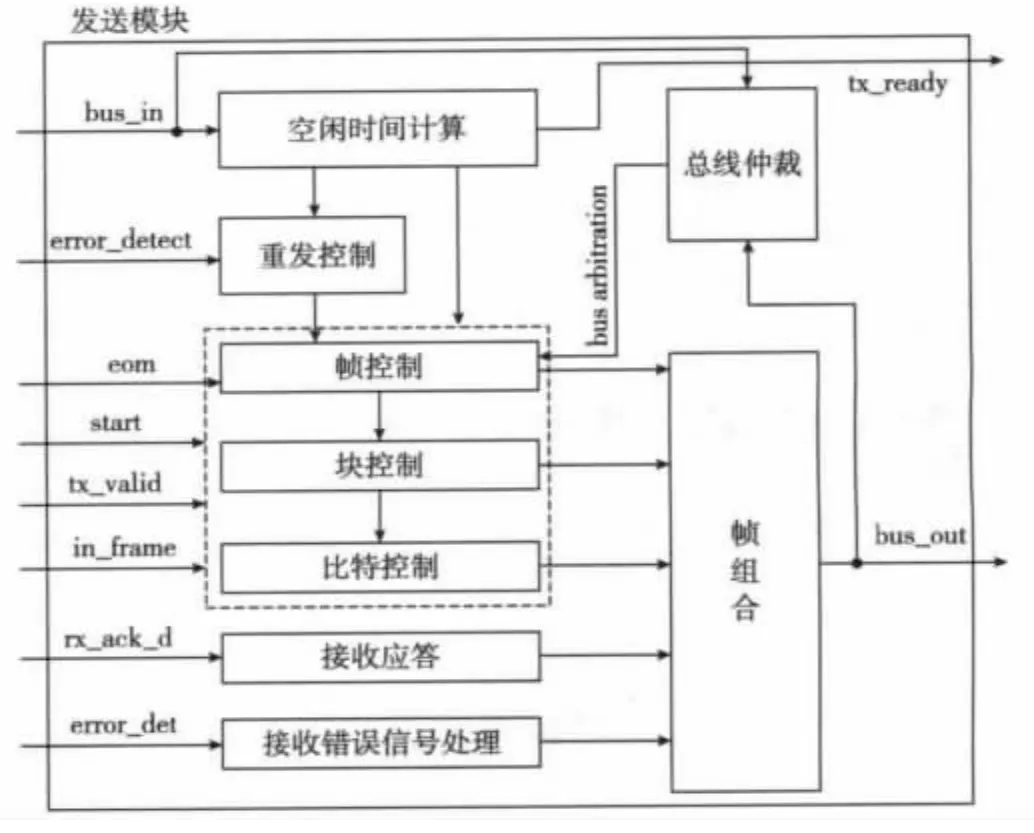

为实现图5所示的发送流程,图7给出了发送模块的设计图。整个协议中需要发送输出的部分将全部由该模块完成,其中包括:总线仲裁功能、发送帧数据功能、无应答时的重发功能、空闲时间计数功能、发送应答信号和接收到错误信号的反馈功能等。图中的帧控制、块控制、比特控制分别表示对发送端的数据在不同时间段的发送有效性控制。

图7发送模块设计图

2.3 接收端设计

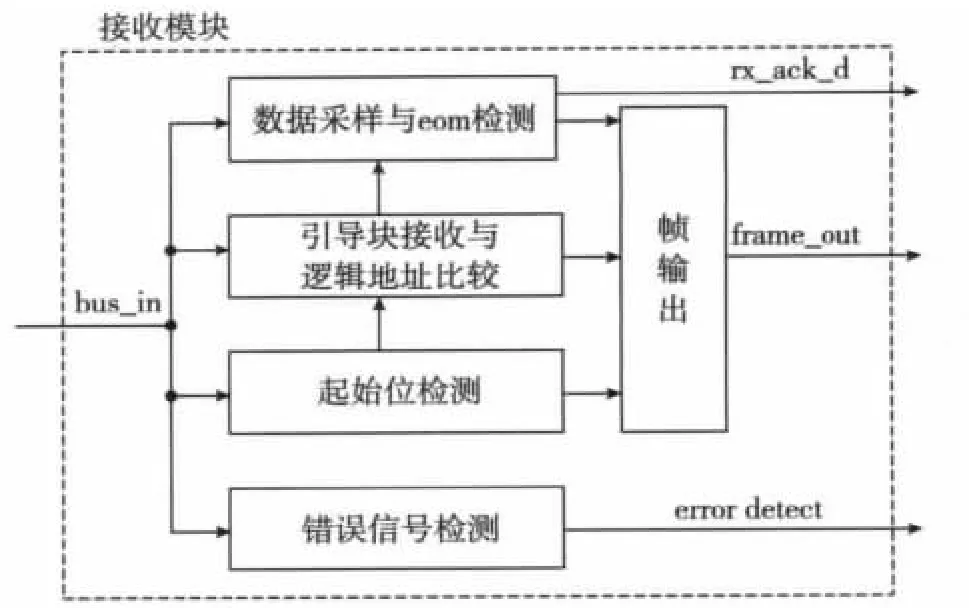

图8 给出了实现图6所示的接收流程的接收端模块设计图。该模块完成的功能有起始信号检测功能、错误信号检测功能、逻辑地址比较功能和总线数据采样功能等。

图8接收模块设计图

2.4 仿真测试平台设计

图9 给出的为CEC总线仿真搭建的测试平台设计图。其中link信号为激励发送端与CEC顶层之间的发送与接收控制信号,保证二者一个处于发送状态时另一个必须处于接收状态;bus_inout表示双向总线;sys_clk、sys_rst分别表示系统时钟和系统复位信号。

图9 仿真测试平台示意图

3 设计电路综合仿真及结果分析

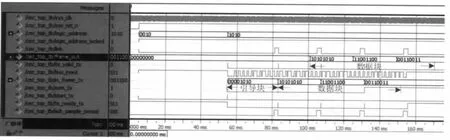

根据上述提出的CEC总线协议设计方案,应用可综合的Verilog语言,在QuartusII平台下实现了电路综合,并在Modelsim6.5g软件平台下完成了电路的仿真。在图9所示仿真测试平台的基础上发送端发送和接收端接收联调仿真波形如图10所示。图中,系统时钟频率设置为12.5 MHz,接收端还原出来的数据与发送端发送的数据一致,发送端第一个输入的数据为引导块,未输出。控制信号ack_sample_period为高电平时表示接收端发送应答信号时间区间,在该区间内采样得到的为接收端的应答信号。

图10 发送端发送及接收端接收联调仿真波形(截图)

当选用Altera公司的Cyclone IV系列器件EP4CE115F29C7综合时,CEC模块资源占用情况下表1所示,其中,CEC设计总计中的逻辑资源占用结果为发送模块与接收模块一起综合的结果,由于发送模块与接收模块二者之间存在一部分的逻辑复用,因此较发送端与接收端资源占用总和少。

表1 CEC模块资源占用情况

4 总结

本文对CEC各功能模块进行了设计并在相关的软件平台下实现仿真验证,从仿真验证结果看,该设计实现功能完备,能够满足设计和产品要求,因此可作为IP核应用于多媒体网络数据传输领域。

[1]廖梦云,赵利.HDMI接口在嵌入式视频监控系统中的应用[J].微计算机信息,2009(23):45-47.

[2]丁铁夫,杨磊,杨旭,等.基于HDMI的实时视频/音频传输系统设计[J].微计算机信息,2009(25):180-182.

[3]苏钟人.平板电视的功能扩展[J].电视技术,2007,31(4):4-7.

[4]王颖.HDMI抢占高清市场先机[J].中国电子商情,2008(3):48-50.

[5]Willas Array公司.HDTV带出HDMI-CEC的微妙变化[J].电子产品世界,2008(8):116-117.

[6]黄庆敏,罗键.HDMI接口标准及应用设计[J].电视技术,2007,31(2):32-34.

[7]谢特辉.HDMI-CEC简介及其应用[J].电视技术,2010,34(10):42-46.

[8]张涌,黄世震.HDMI CEC的设计与实现[J].中国集成电路,2010(12):64-67.

[9]Quantum data white paper[EB/OL].[2012-11-20].http://www.quantumdata.com/pdf/CEC_White_Paper.pdf.

[10]Silicon Image,Inc.HDMI Specification Version 1.3[EB/OL].[2012-11-20].http://download.csdn.net/detail/plain_liu/365154.