烧结温度对厚膜电阻的影响研究

张 显,朱耀寰,王海丰

(西安电子科技大学技术物理学院,西安710071)

从上世纪六十年代开始,厚膜混合集成电路与半导体集成电路相互补充、相互渗透成为集成电路的一个重要组成部分,广泛应用于电控设备系统中。厚膜混合集成电路简称厚膜电路或厚膜混合电路,即通过丝网印刷和烧结等工艺在基片上制作互连导线、电阻、电感等满足一定功能要求的电路单元。由于体积小、功率大、性能可靠、设计灵活、成本低和性价比高等优点在混合电路产业中占80%的市场份额[1]。

钌基厚膜电阻具有精度高、稳定性好、耐高温、工艺重复性好等特点[2]。影响厚膜电阻的因素有很多,其中烧结工艺起着重要作用[3],它主要分:烧结温度、保温时间、升温速率以及气氛控制。本文着重讨论烧结温度对厚膜电阻器阻值和HTCR的影响,并分析了厚膜电阻的微观结构及其性能。

1 实验方法

本次实验采用西安宏星浆料有限公司生产的R-2200系列电阻浆料(功能相的主要成分是RuO2、Bi2Ru2O7和 Pb2Ru2O6)和 Ag-Pt导体浆料,实验基片采用96%氧化铝基片。使用丝网印刷机通过手动印刷的方式在基片上印制方阻两边长的比例为1∶1.25的电阻。丝网印刷采用不锈钢丝网,数目为325目。先用该设备在基片上印制导体,经烘干烧结后,再印制电阻,印好后在室温放置15 min,以便浆料充分流平,置于125℃的烘箱中保温12 min用箱式电阻炉按不同的烧结工艺烧结。

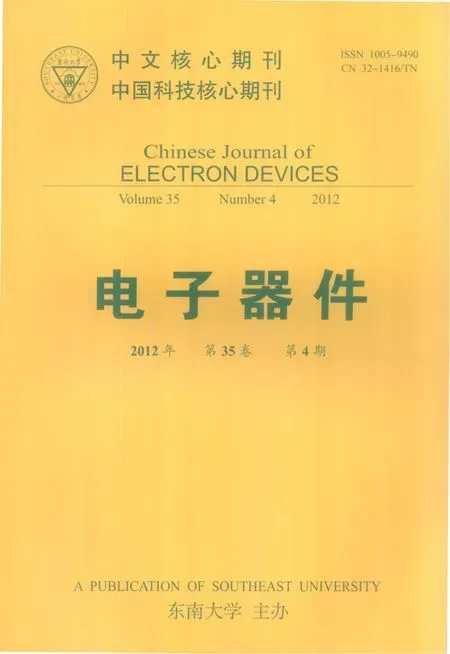

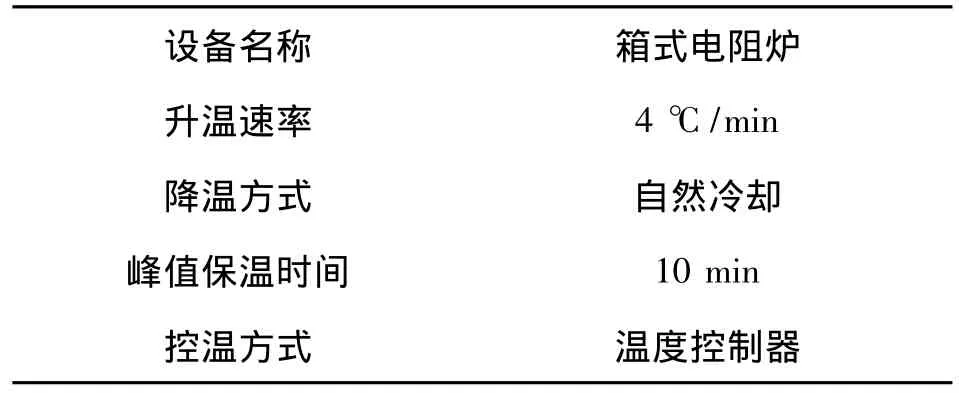

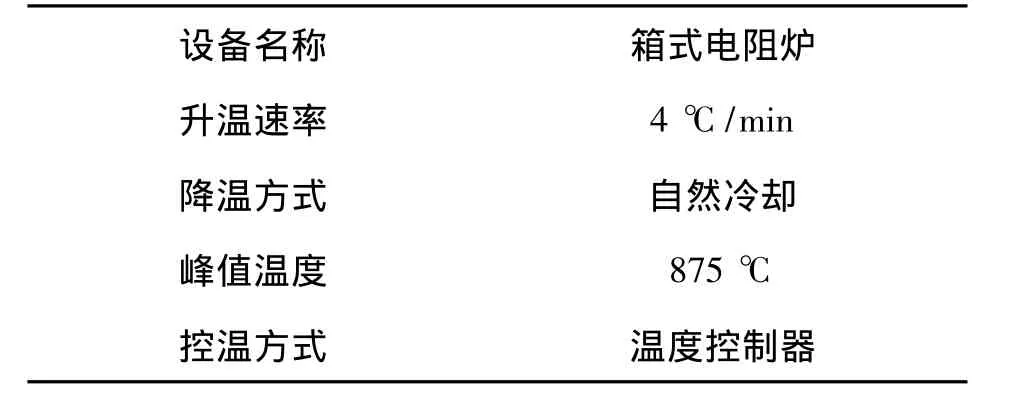

实验采用比较分析的方法,先按照工艺I(根据生产商提供的烧结曲线改编)在750℃、800℃、825℃、850℃、875℃、900℃和950℃的不同峰值温度下烧结,然后进行重烧实验,确定最佳烧结温度。然后在最佳烧结温度下,将保温时间分别设为8 min、9 min、10 min、11 min和12 min 烧结(工艺Ⅱ),这样就可以确定保温时间。在确定该浆料的最佳烧结峰值温度和保温时间后,就可以确定升温速率,升温速率分别设为4 ℃/min、5 ℃ /min、7 ℃ /min、9 ℃/min(工艺Ⅲ)。

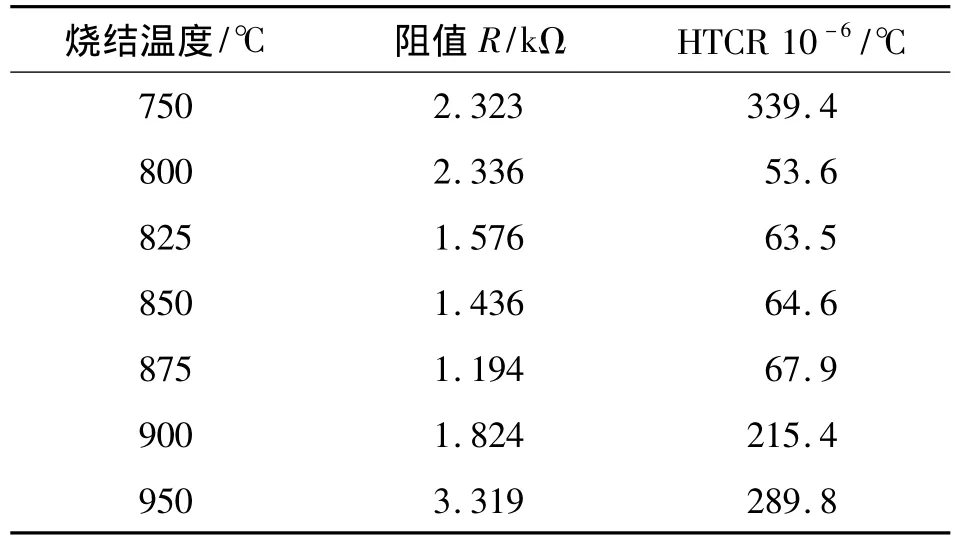

表1 烧结工艺I的主要技术参数

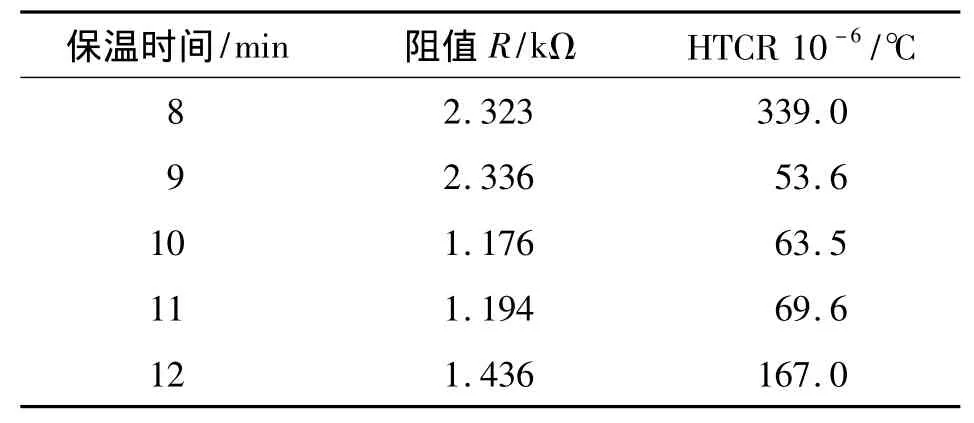

表2 烧结工艺Ⅱ的主要技术参数

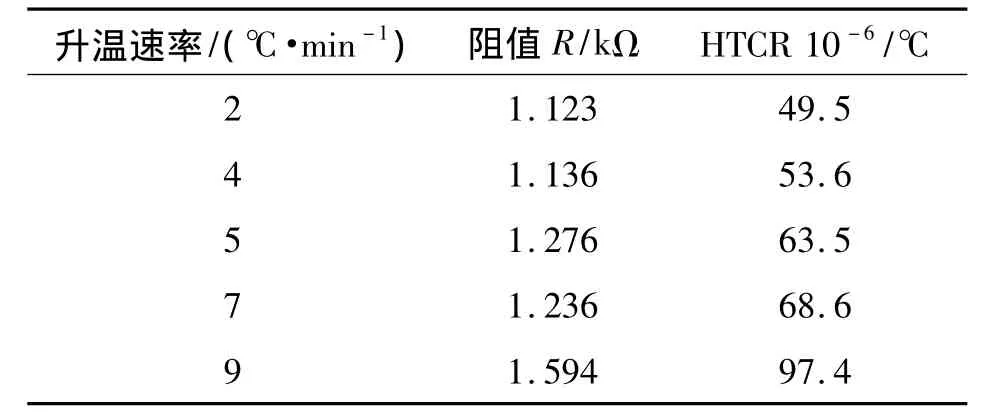

表3 烧结工艺Ⅲ的主要技术参数

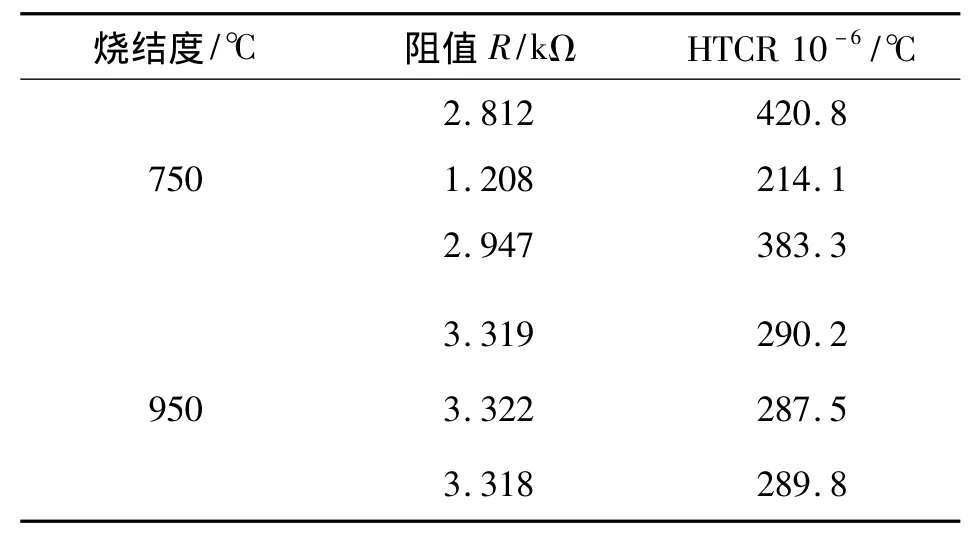

烧结后,用PTC测试仪测试样品的高温电阻温度系数(HTCR)。对样品用SEM观察之前,要将样品用46%的氢氟酸侵蚀1 min,以去除表面的玻璃相,使导电颗粒露出,用去离子水冲净,置于125℃的烘箱中,烘干10 min。然后对性能较好的样品进行重烧实验,从而确定适合该电阻浆料的烧结曲线。为了减小实验的误差,采用一次烧结3个样品,测试平均值的方法,在下面的到的数据都是3个样品的平均值。

2 实验结果与讨论

2.1 烧结工艺对厚膜电阻电性能的影响

我们知道烧结影响厚膜电阻的性能主要体现在烧结峰值温度、保温时间和升温速率,表4、表5、表6分别是不同工艺下对电阻阻值和HTCR数值。

表4 工艺I在不同烧结峰值温度下的阻值和HTCR

表5 工艺Ⅱ在不同保温时间电阻的阻值和HTCR

表6 工艺Ⅲ在不同的升温速率的阻值和HTCR

表7 在750℃和950℃下烧结样品的性能

通过表7,我们可以看出电阻在烧结温度过低或是烧结温度过高时,阻值和HTCR都较大,通过实验发现在低温时电阻阻值的差异较明显,HTCR不稳定,在高温时电阻的阻值较大,但是阻值变化很小,HTCR也较稳定。由此可以看出,在烧结温度较低时电阻处于欠烧状态,在温度过高时明显处于过烧状态。

从表4、表5、表6中我们可以得到以下结论:

(1)在800℃ ~900℃范围内,电阻的阻值先是随着烧结温度的升高而下降,在875℃时有最小值而后随着烧结温度的升高而增大。HTCR则是随着烧结温度的升高而升高,表现出正温度特性,该结论可以通过隧道势垒模型解释。

(2)电阻的阻值和HTCR都是先随着保温时间的延长而降低,而后则增大,这可能是由于保温时间过短,功能相中的烧绿石并没有完全分解成RuO2,保温时间过长效果和提高烧结峰值温度一样。

(3)升温速率与气孔的排除有关,当升温速率过快时,厚膜内的气孔排除不完全,在厚膜的表面形成的缺陷较多,在宏观的反映就是电阻的阻值增大,HTCR增大。降低升温速率,各相的反应时间延长,气孔有效排出,这样可以有效地减少在表面的气孔,从而改善厚膜电阻的性能。

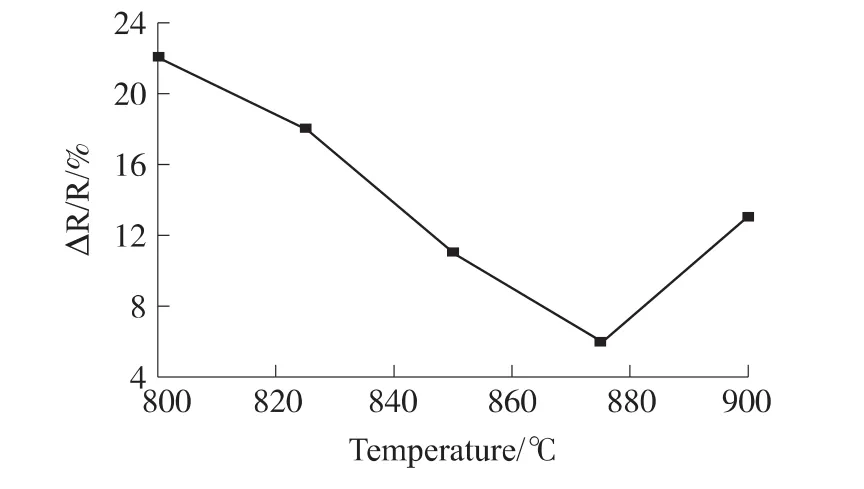

重烧时,有些导电网络会被软化的玻璃相隔断,有的则重新连接上,致使电阻值发生变化[4]。烧结峰值温度的确定不能只考虑需要的电阻值和TCR值,而必须以稳定性好坏来判别,最简便的方法是测定各烧结温度下的电阻变化率[5-6]。图1是在烧结工艺I下电阻的重烧变化率。

图1 工艺I下电阻的重烧变化率

由图1可见,在工艺I下电阻的重烧变化率均为正值。在875℃时重烧变化率最小,最稳定只有6%,从外观上看875℃烧成的电阻表面平滑,有光泽。所以适合该浆料的烧结温度应该是875℃。

2.2 隧道势垒模型分析

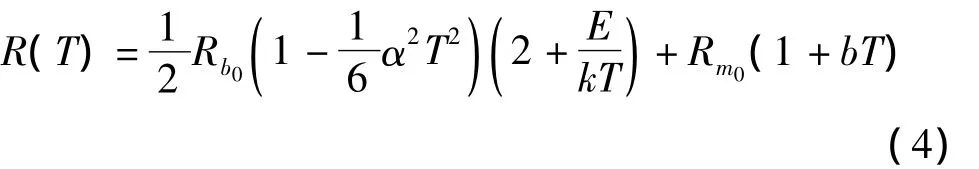

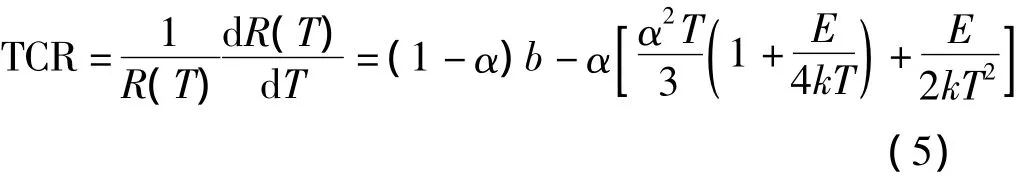

Pike和Serger等人提出的隧道势垒模型[7]可以很好的解释电阻和温度的关系,厚膜电阻的阻值可以表示为:

式中:a与绝缘势垒高度有关,E-激活能,k-波尔兹曼常数,T-绝对温度,b是钌的温度系数,Rb0是势垒投射因数,Rm0是在绝对零度下测量的金属相的电阻值。

sin(aT)/aT相描述了隧道贯穿本身的温度系数[8]。由于a的值较小大约 10-4K-1,所以 sin(aT)可以用aT代替。在式(1)中的指数相用来计算该系统中的带电钌粒子的平衡数。根据Gary和Johnso的研究[9],钌的活化能大概是2 meV。式(1)中最右侧的那项描述了金属钌颗粒的电阻温度特性。b的值是500×10-6/℃

通过式(1)我们可以很清楚的看出,当烧结温度升高时,势垒电阻下降,但是导电相中钌的金属电阻升高,并不能确定总的电阻如何变化。这就要知道在厚膜电阻浆料中RuO2的含量如何,因为当其含量高于某一点时,金属导电占主要作用,当其含量低于某点时,隧道势垒导电占主要作用。

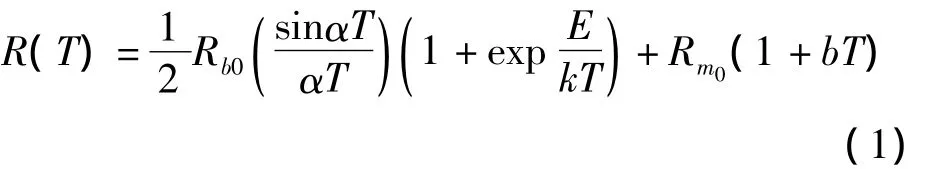

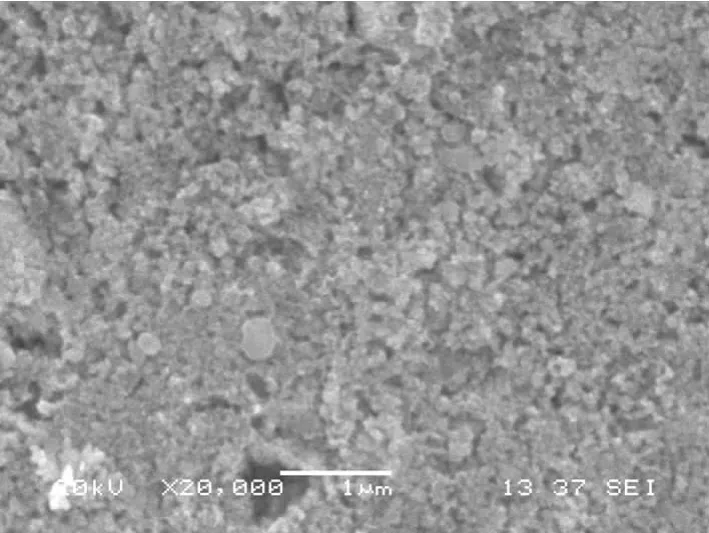

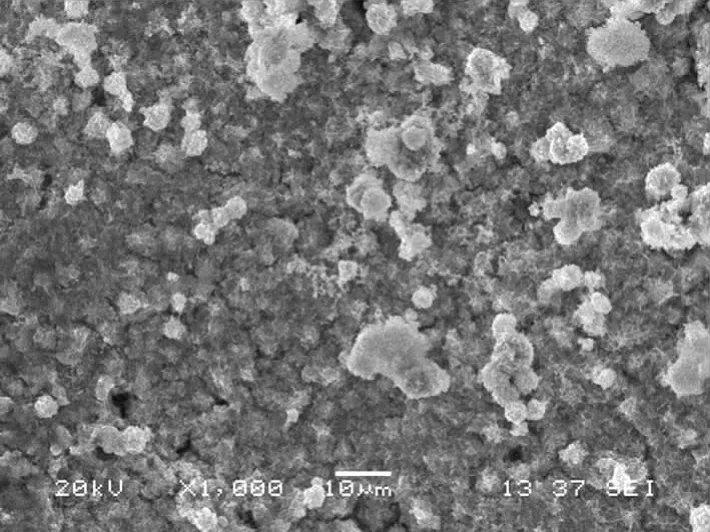

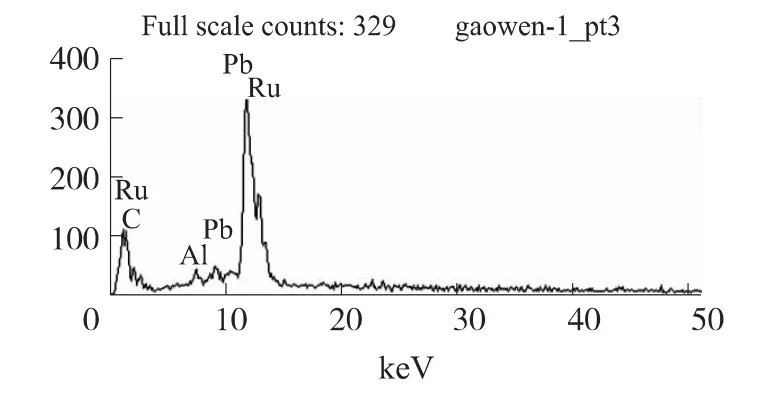

我们通过SEM和EDS分析可以清楚的知道在R-2200系列电阻浆料中,电子的传导主要是由隧道势垒传导的。这就可以很好的解释了为什么温度在800℃~900℃之间,电阻阻值随着温度的升高而降低的问题。当烧成温度小于750℃时,导电相中的颗粒散乱分布,没有形成导电链,更没有连接成网,这也是电阻较大,不稳定的原因,如图2所示在烧结温度高于950℃时,RuO2晶粒异常长大,导电网络断裂,势垒高度上升,从而电阻阻值剧增,如图3所示;而在正常温度下烧结的厚膜电阻的表面形态如图4所示,导电相中的 Pb2Ru2O6分解成RuO2和PbO2,RuO2颗粒相互连接,形成导电链,导电链互相交叉形成导电网,而PbO2则均与的分布在其周围,起到改善电阻温度系数的作用。

图2 在低温(750℃)下烧成的厚膜电阻的表面形态,导电链在图中观察不到

图3 在高温(950℃)下烧成的厚膜电阻的表面形态

从图3可以看出:RuO2异常长大,导电网络断裂。

在875℃烧结的厚膜电阻的微观形态如图4所示,用EDS能量分析观察图中的白色颗粒,发现其中含有大量的Ru和Pb,而且其中Ru和Pb的比值大约是1,这对于功能相的主要成分是 Ru2O和Pb2Ru2O6的浆料来说似乎有点不正常,但是考虑到浆料中的玻璃成分主要是硼酸铅铝玻璃,其软乎温度只有600℃,而在875℃时它早已分解出PbO2,这就解释了为什么Pb的含量高于Ru的含量。对图中白色颗粒的EDS图像如图5所示。

图4 正常温度(875℃)下烧成的厚膜电阻的表面形态,导电链已经形成。

图5 厚膜电阻浆料经875℃烧结后导电相的分析,RuO2和PbO2的比例大约是1

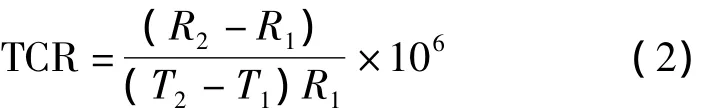

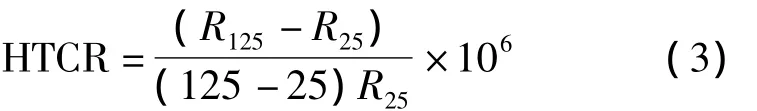

对厚膜电阻器来说,TCR是其一个非常重要的参数,生产上常用式(2)来测试电阻的TCR。

式中的R2是在温度为T2时的电阻值,R1是在温度为T1时的电阻值。所以HTCR可以表示为:

在绝对温度只有几百度时,E/Kt≪1,αT≪1,因此式(1)可以展开,并取其一级近似得到:

由R(T)对T微分可以得到:

式中α=Rb/(Rb+Rm),其取决于势垒的单元电阻系数。根据M-I-M模型的边界条件T=289 K时,TCR=0,所以式(5)可以算出电阻的激活能,这里要用到一些前人的数据[8],将a=5×10-4K-1,b=5 ×10-4K-1,α =0.7,T=298 K 代入式(5),计算得到E=2889 μeV,当T=398 K 时,HTCR=52 ×10-6/℃。有文献[10]指出基片对TCR也有影响该计算中没有考虑基片的因素,但与实验结果非常的相近。

2.3 液相烧结模型分析

液相烧结致密化的过程传统上可以划分为三个阶段即重排阶段、溶解-沉淀阶段和气相排除阶段一般来说随着烧结的进行,致密化速率显著减小,在烧结后期还可能会出现反致密化。

厚膜电阻的烧结过程就是液相烧结过程,其大致过程如下:

烧结初期,经过烘干后的厚膜电阻器中,有机粘结剂仍然会有残留,随着温度的升高,有机黏结剂会慢慢的挥发。该过程中导电相和玻璃相会渐渐分散,但是基本上还是相互独立,电阻体的结构疏松即使其中的导电相和玻璃相重新排列,但是致密化程度较低,不具有导电能力[11]。当温度高于600℃时,玻璃相开始软化,有一部分开始浸润导电颗粒随着温度的升高,扩散加快,并且渗透到导电颗粒之间形成毛细管,毛细管以表面张力的形式拉近导电颗粒,使他们相互靠拢、粘结形成链状和网状结构最后形成具有一定结构和性能的较平滑和致密的厚膜层。在此过程中会有一部分玻璃相融化后浸润基片,使膜层牢牢的附着与基片上。

当烧结温度为750℃时,方阻较大,虽然图2中的颗粒分布比较均匀,但是烧结温度过低,玻璃相软化时间不长,对于导电相的浸润不充分,毛细管力较小,不能让导电颗粒连接成网,这就造成许多导电颗粒接触不够紧密,烧结膜层的结构疏松,宏观上表现出较大的电阻值,膜层中孔洞多[12],膜层结构不稳定。当烧结温度适中时,玻璃得到很好的流延扩散玻璃在电阻体中分散均匀。由于温度上升,毛细管力增大,能很好的拉近导电颗粒,电阻的结构致密连接成链,并交织成到电网,所以接触电阻小,整体阻值降低。从图4中我们可以很清楚的看出玻璃相均匀的分布在导电网络周围,形成的厚膜均匀稳定当烧结温度提高到950℃时,由于温度过高,为典型的过烧状态,此时导电相颗粒进行重排,晶粒长大的速度加快,造成晶粒大小悬殊,在表面能的推动下大晶粒界面向曲率半径小的晶粒中心推进,造成大晶粒进一步长大,小晶粒消失,这就使得原有的导电网络断裂,势垒急剧升高,膜层结构不均匀,宏观上的表现就是阻值增大。

在液相烧结中,保温时间和升温速率同样影响烧结的进程。保温时间不够,玻璃相的浸润不充分,毛细管力拉近的固相颗粒不够致密,膜层会出现疏松,电阻增大。保温时间过长的话,RuO2的晶粒会继续长大,形成的导电网络会出现断裂,势垒升高,电阻增加。升温速率主要影响气孔的排出,如果升温速率过快的话,烧结中前期不能完全的除去浆料中的有机粘结剂的挥发成分。烧结后期,晶粒的生长速率过快,气孔排出减少,在膜层内形成较多的封闭气孔,存在的缺陷较多,电阻的性能较差。升温速率过慢对电阻微观结构和性能的影响不明显。

3 结论

(1)烧结温度对厚膜电阻器的影响可以通过隧道势垒模型和液相烧结模型来解释。在800℃~900℃范围内,电阻的阻值先是随着烧结温度的升高而下降,在875℃时有最小值,而后随着烧结温度的升高而增大。HTCR则是随着烧结温度的升高而升高,表现出正温度特性。

(2)电阻的阻值和HTCR都是先随着保温时间的延长而降低,而后则增大。

(3)升温速率与气孔的排除有关,当升温速率过快时,电阻的阻值增大,HTCR增大。降低升温速率,可以各相的反应时间延长,使气孔有效排出,从而改善厚膜电阻的性能。

(4)电阻的重烧实验表明,在875℃时该厚膜电阻的重烧性能最佳。

(5)对于R-2200系列浆料来说最合适的烧结工艺是:烧结温度为875℃,保温时间10 min,升温速率控制在4 min/℃。

[1]姜潇,韩勇虎,王志忠.厚膜IC制造工艺、特点及其应用[J].电子节能,1998,4:42-43.

[2]丁鹏,马以武,李民强.钌基厚膜电阻传导模型初探[J].电子器件,2003,26(4):376-378.

[3]Walker A T,Silverman L A,Hang K W,et al.Anew Hybrid Resis tor System for TCR Control and Process Insensitivity[A].ISHM 93 Proceedings[C]//1993:695.

[4]丁鹏,马以武.钌基厚膜电阻导电机理的国内外研究状况[J].电子器件,2003,9:264-268.

[5]王吉刚,董述恂.RuO2基厚膜电阻电脉冲调阻工艺研究[J].电子元件与材料,2003,22(1):42-45.

[6]Tong S,Falleta C E.Proc.ISHM.Minneapois,MN[J].1987:8.

[7]Pike G E,Sewer C H.Electical Properties and Conduction Mecha nisims of Ru-Based Thick-Film(Cermet)Resistors[J].J Appl.Phys.1977,48(12):5152-5169.

[8]Sartain C C.Reply to Comments by Paul R.van Loan on Semiconduc tors Produced by Doped Oxide-Glasses with Ir,Pd,Rh of Ru[J].J Non-Cryst Solids,1971(6):173-175.

[9]Gary M Crosbie,Johnson F,Trela W.Processing Factor Dependence of Resistivity Parameters of Ruthenate-Based Thick film Resitors with Low temperature Coefficients[J].Journal of Applied Physics 1998,84(5):2914-2916.

[10]王思信,侯正则.RuO2厚膜电阻体的阻值与TCR的关系[J].贵金属,1997,18(2):8.

[11]唐珍兰,胡君遂,堵永国.厚膜PTC热敏电阻烧结峰值温度研究[J].新技术新工艺,2006(1):113-115.

[12]马以武,宋箭,常慧敏,等.烧结工艺对钌基厚膜应变电阻性能的影响[R].功能材料,1998,10:650-651.