RFID系统的串扰分析及消除*

郭桂林,李文钧

(杭州电子科技大学电子信息学院CAD研究所,杭州310018)

射频识别技术(Radio Frequency Identification,RFID)是从20世纪80年代起走向成熟的一项自动识别技术[1]。它利用射频方式进行非接触式双向通信交换数据以达到识别目的。基于RFID标签对物体的唯一标识特性,引发了人们对基于RFID技术的应用研究热潮[2],特别是微电子技术中大规模集成电路的发展和高速电路的出现,RFID系统的各方面性能指数增加和成本进一步降低,逐渐的被运用在交通,现代物流,智能家居等各个领域[3]。

随着RFID系统中信号的频率的变高、边沿变陡、电路板的尺寸变小、布线的密度变大,EMC和SI成为电子工程师不可避免的问题。串扰是指有害信号从一个网络转移到另一个网络,它是信号完整性(SI)中的一个重要问题,在数字设计中普遍存在,有可能出现在芯片、PCB板、连接器、芯片封装和连接器电缆等器件上[4]。如果串扰超过一定的限度就会引起电路的误触发,导致系统无法正常工作。因此了解串扰问题产生的机理并掌握解决串扰的设计方法,采取相应的措施使串扰减小到合理的范围。将串扰原理深入地融入到产品开发尤其是高速PCB设计当中,最终为产品设计提供优化的解决方案,已经成了产品成功的关键一环。

1 串扰的基本原理及分类

串扰是信号在传输线上传播时,由于电磁耦合而在相邻的传输线上产生不期望的电压或电流噪声干扰,信号线的边缘场效应是导致串扰产生的根本原因[5]。信号在通过一导体时会在相邻的导体上引起两类不同的噪声信号:容性噪声信号与感性噪声信号,也就是说串扰有容性串扰和感性串扰两种,一般情况下感性串扰要比容性串扰大得多。如图1所示产生串扰的一方被称为入侵者(Aggressor),而另一个收到串扰的被称为受害者(Victim)。

图1 串扰中的Aggressor与Victim

图2表示串扰的形成过程,当两根平行线平行放在一起,其中一根线中一端有信号源Vs及内阻ZOG,另一端负载阻抗ZLG,回路通过地构成闭环;另一导线中仅有阻抗ZOR和ZLR。当驱动信号(1)通过发射线时,由于发射线和接收线间的寄生电容,会在接收线上产生分别向两端走向的干扰信号(3);同时,驱动信号通过发射线时会在其周围产生一个变化的磁场,这个磁场与接收线相交,并在接收线中感应出一个与驱动信号相反走向的干扰电流(2)。干扰电流(2)和(3)就是驱动信号从发射线耦合到接收线上的串扰信号。

图2 串扰的形成过程

1.1 容性串扰

容性串扰就是信号线间的容性耦合,当信号线在一定长度上靠得较近时发生。如图3所示的两根信号线,分别称为噪声源和噪声接收线。由于线间的寄生电容,噪声源的噪声就会通过电流注入的形式耦合到噪声接收线上。这个电流将通过阻抗为Z0的传输线向两边传输,直到它消耗在源内阻ZS和负载ZL上;产生的电压尖峰值是由Z0决定的,当电流脉冲通过ZS和ZL时,产生的电压与其阻抗成正比,如果阻抗不匹配,将产生反射。在没有端接的情况下,在ZL产生的电压尖峰将非常大,所以,在负载端端接可以大大减小下一个器件输入端的电压噪声。

1.2 感性串扰

干扰线上的di/dt经过互感在受扰线上产生一个电压,从而激励了感性耦合电流,即受扰线上感应的噪声电压将受到一个阻抗,并激励相应的电流,而且此电流与干扰线上的电流方向是相反的[6]。所以当此电流在受扰线上分为向前、向后传播的两部分时,前向传播的电流是从返回路径到信号路径,而后向传播的电流则是从信号路径到返回路径,如图4所示。

图4 感性串扰的传播路径

2 RFID系统串扰仿真及分析

图5是RFID系统中Reader的PCB一部分,Bus信号的时钟频率276 MHz,Victim网络为网络的正中间的传输线,Aggressor网络为相邻的网络,仿真模拟。

图5 RFLD系统中Read的PCB

2.1 线间距的串扰仿真

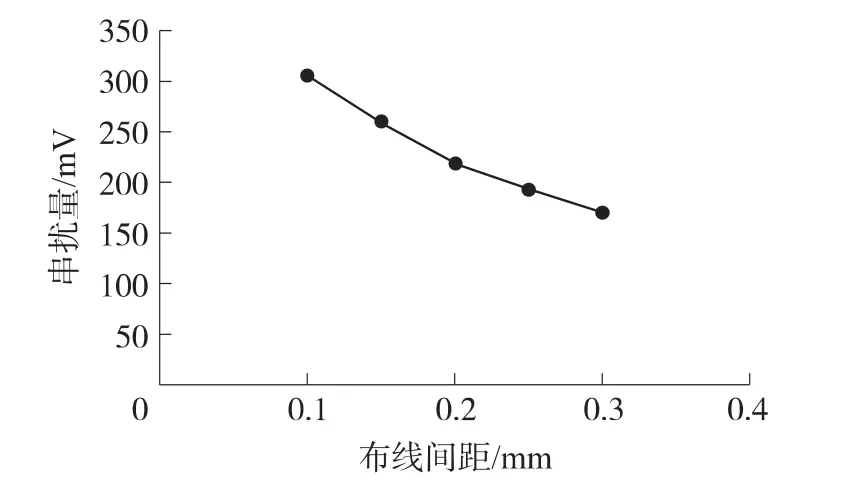

线间距从0.1 mm~0.3 mm以0.05 mm为间隔,做线路长度的Sweep分析的结果(图6)。可以看出串扰大小跟布线间距成反相关的关系,线间距越大,串扰量越小。

图6 不同线间距串扰仿真

2.2 网络端接串扰仿真

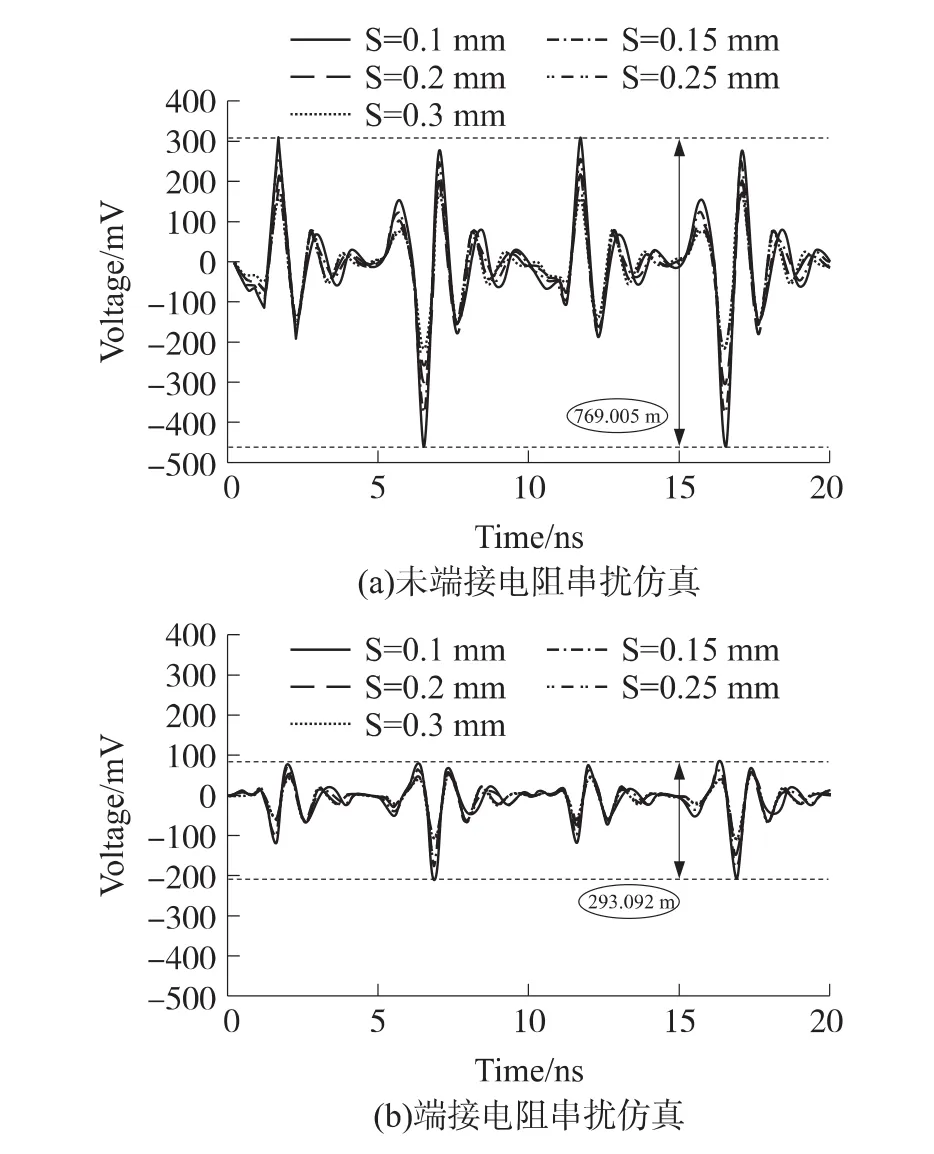

如图7上一幅图是网络未端接时的串扰量,从中可以看出串扰量峰值可以高达300 mV,对于在低压工作电路,有可能出现误动作。而下图端接电阻以后,串扰的峰值最大为100 mV,说明网络端接能大大减小串扰量。

图7 端接与未端接电阻对串扰的影响

2.3 奇模式和偶模式串扰仿真

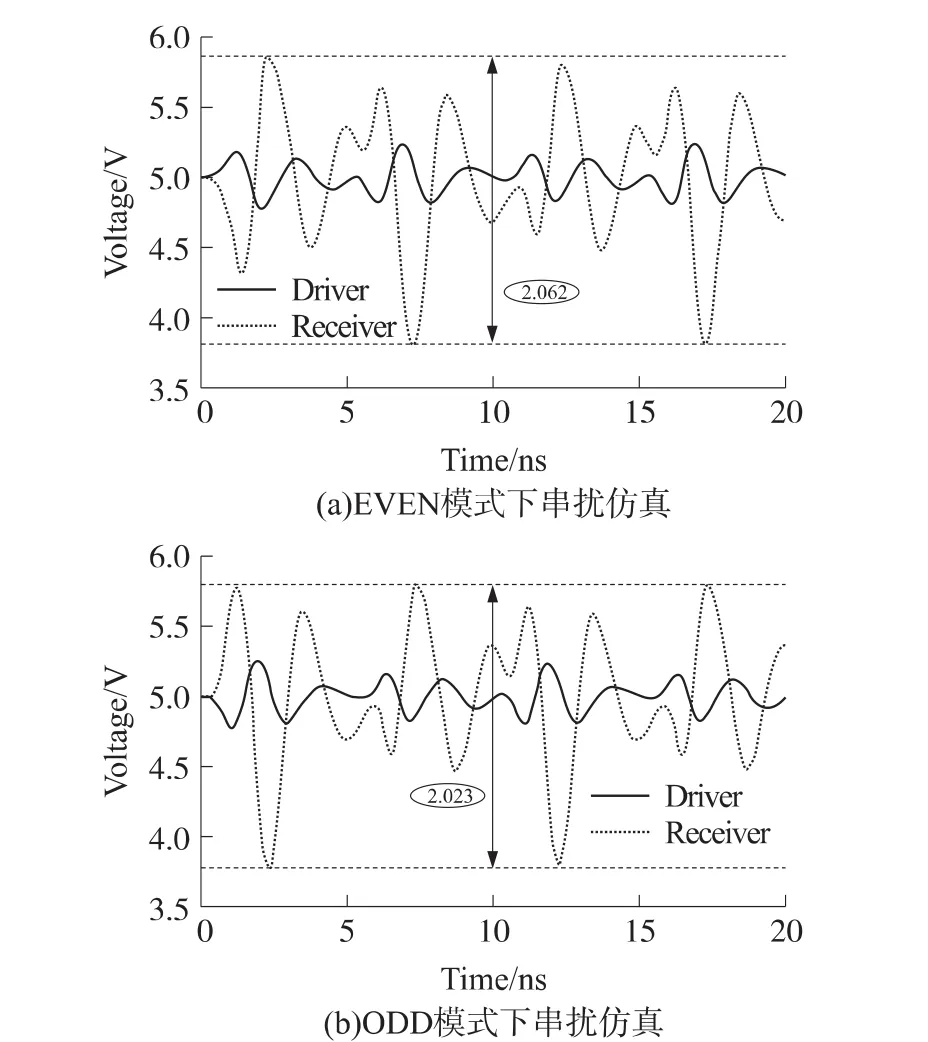

图8所示上图是(EVEN)奇模式的仿真图,下图偶模式(ODD)。从中可以看出Receiver远边大约有振幅2 V左右的串扰,而ODD方式大约也有振幅2 V左右串扰,但脉动系数远小于EVEN方式。

图8 EVEN/ODD模式下串扰仿真

3 降低RFID系统串扰的方法

影响RFID系统串扰的因素不仅仅是以上仿真的几个方面,但却是能在实际应用电路中最主要考虑的因素,所以没有一一列举所有的影响因素的仿真结果,总结归纳降低串扰的方式如下:

(1)在布线规则允许的情况下,将两条传输线之间的距离增到最大或增加网络端接来减小串扰;

(2)在设计目标阻抗时,应该尽量使导体靠近地平面,使得传输线可以紧密地与地平面进行耦合,这样可以减小对邻近参考线的耦合及干扰;

(3)信号采用差分(ODD)布线技术,如系统时钟信号;

(4)同层的走线正交布线,可以抑制传输线的耦合;

(5)最小信号间平行走线的长度,尽量是一些比较短的平行线段,避免长的平行线段;

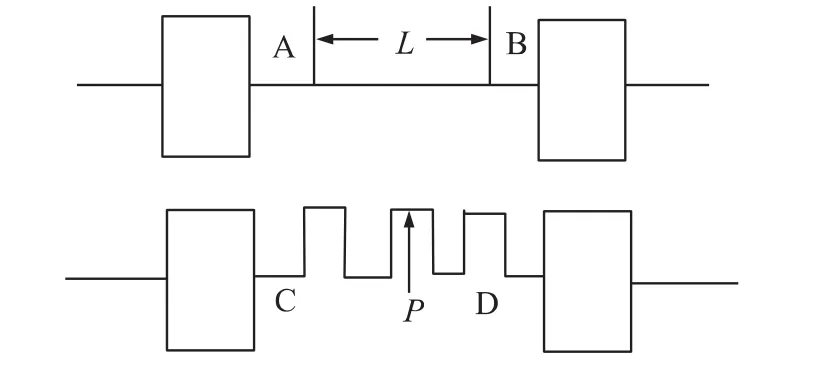

(6)加大线间距,减小线平行长度,必要时可以图9所示的jog方式走线,减小容性串扰[7];

(7)妥善布局,防止布线时出现拥挤;

(8)尽量用上升沿较慢的器件,但是在使用此方法时要非常小心,否则容易产生负面影响[8]。

图9 jog走线方式

4 结论

本文结合实际的RFID项目,利用Allgro PCB SI仿真电路的串扰信号,提出了如何更好的避免串扰的发生,提高了系统的稳定性和健壮性。同时,在其它的高速电路设计中也有一定的借鉴性。信号完整性问题的引发因素有很多方面,串扰是其中的一个主要的因素,减小串扰就成为信号完整性研究的主要方面。理想说来,降低串扰的方法有很多,但是在高密度和高速电路中,要根据实际的情况来折中各种方法,如果只是为了把串扰减小而不顾实际情况,这样的做法是没有意义的。

[1]游战清,李苏剑,郑利强,等.无线射频识别技术(RFID)理论与应用[M].北京:电子工业出版社,2004:23-27.

[2]国科办厅字[1998]82号文件.中国射频识别RFID技术政策白皮书[R].北京:中华人民共和国科学技术部等15部委,2006年6月9日.

[3]宋起柱.RFID技术及电磁兼容研究[J].中国无线电,2005(12):57-60.

[4]Eric Bogatin.信号完整性分析[M].李玉山,李丽平,译.北京:电子工业出版社,2006:101-105.

[5]尹建.PCB的电磁兼容性研究[D]:[硕士学位论文].成都:电子科技大学无线电物理系,2006.

[6]张肃文,陆兆熊.高频电子线路[M].北京:高等教育出版社,1993:123-147.

[7]Stephen H Hall,Garrett W Hall,James A McCall.伍微高速数字系统设计[M].2006:47-55.

[8]后盾.信号完整性分析及其在高速数字电路设计中的应用[D]:[硕士学位论文].杭州:浙江大学通信与信息学院,2004.