基于调频连续波雷达目标信号处理器研究*

黄燕群,黄 勇 ,蔡睿洁,赵进军

(中国兵器工业第203研究所,西安 7 10065)

0 引言

调频连续波雷达[1]在近距离动目标航迹跟踪、地面智能武器系统探测等方面具有很大的优势。

调频连续波雷达由前端探测器和目标信号处理器组成。前端探测器完成微波发射与目标反射波接收;目标信号处理器是控制雷达工作方式和动目标解算的重要部件。目标信号处理器的作用:一是提供连续波调制信号;二是解算运动目标的跟踪轨迹参数,同时把参数发送至系统决策控制单元。随着雷达探测精度的提高,对目标处理器的要求也不断的提高,导致要处理的数据量增大,算法更加复杂。因此对目标信号处理器的运算速度、实时性、工作稳定性的要求越来越高。

文中采用高性能定点DSP[2]芯片,搭配FPGA芯片作为处理器的核心芯片,管理雷达启动、信号采集、数据搬运、解算目标参数的工作时序,以流水线方式处理数据流。DSP芯片完成算法解算、EDMA数据搬运;FPGA管理AD/DA数据转换、天线扫描控制核,内置FIFO数据缓冲池,协同DSP完成地面动目标跟踪解算。

1 调频连续波雷达工作基本原理

首先了解调频连续波雷达工作原理:调频式连续波雷达的发射机天线和接收天线是独立分开的,发射机根据调制信号产生连续高频等幅波,其频率在时间上按照调制波的规律变化。

由于动目标的距离、运动改变了反射波的频率,与发射波比较目标反射波有了变化,目标回波和发射机直接耦合过来的信号加到接收机的混频器内,在混频器端输出了差频电压,此时差频电压的频率与目标距离有关,差频电压经过放大、滤波处理得到目标信号处理器要处理的中频信号。

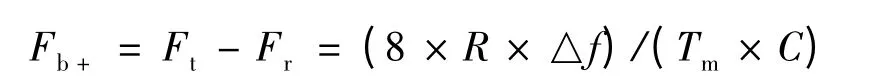

图1中三角波形实线Ft为发射波,三角波形虚线Fr为目标的反射波,△f为频偏,Tm为调制信号周期,S为目标中频信号,Fb-(Fb+)为Ft与Fr的差频,距离R,光速C与差频关系如下式:

根据多普勒效应可以求出运动目标的径向速度:

而目标的角度则采用两个通道的中频信号进行和差法求得。

图1 调频雷达工作原理

2 目标信号处理器总体设计

目标信号处理器电路涉及模拟弱信号、高速数字信号;同时按指标要求,且需兼顾处理器的功耗、实时性、冗余度、电磁兼容等性能指标,因此在设计原理图之前,对硬件电路进行全局规划是必须的,图2是目标信号处理器的功能模块图。

图2 目标信号处理器的功能模块图

工作原理:系统上电,电压稳定后进入自检,完成后处于就绪状态,即低功耗模式;当处理器接收到“启动”指令后,逻辑控制模块产生天线扫描控制信号,同时启动调制波信号模块、AD采集模块;当一组天线数据采集完成后,搬运到数据信号处理模块[3]里的缓冲池,目标解算;最后将动目标参数通过通讯模块发送至系统决策。

目标信号处理器是软件算法和硬件电路的结合,而硬件电路则是前提,对其要求也比较高。

2.1 硬件电路设计

文中用DSP、FPGA芯片分别作为数字信号处理模块和逻辑控制模块的核心器件。两者搭配使用既可以发挥DSP的运算速度快,结构成熟稳定,易调试,高效运算复杂数学模型的优点;又发挥了FPGA接口控制灵活,并行运算,定置资源丰富的特点。两者的结合极大的提高了处理器的整体处理能力。

以下对各功能模块做简要的描述。

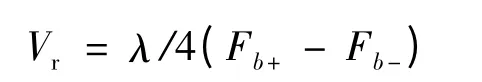

1)AD采集模块。采用2个AD9224ARS芯片作为AD转换芯片,使用差分输入方式工作(如图3所示)。

图3 AD采集电路

图4 DA接口电路

在AD芯片前端同时需要增加隔直流、LC虑波、单端转差放大等措施,来提高信噪比,降低信号在传输过程的共模干扰噪声;而AD的采样时钟及量化后的数据则由FPGA控制和保存。

2)调制波信号模块。调制波信号由DA芯片生产模拟信号,经后端的电压处理电路而生成。FPGA控制AD5445YRU芯片的波形数据输入以及时钟、读/写等信号;AD5445YRU芯片输出端设置电压加法器、有源多级滤波器等处理电路,将电压信号的幅值调整到相应的范围,电路如图4所示。

3)逻辑控制模块。逻辑控制模块选用型号为EP3C55[4]的 FPGA芯片为主控制芯片,完成以下功能:

ⓐ内置32位数据总线接口与DSP连接;

ⓑ控制AD/DA转换、FIFO满中断、天线扫描等控制信号;

ⓒ定制FIFO数据缓冲结构。

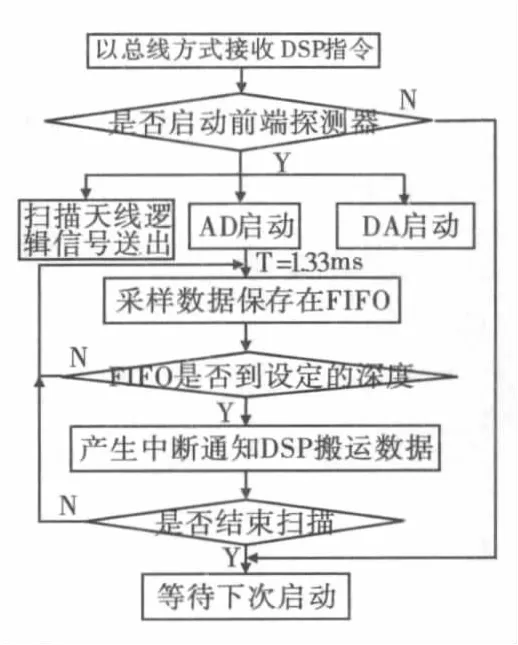

采用32位数据总线接口,一次DSP读操作完成两个通道数据的读取,增加吞吐量;内置FIFO形成乒乓结构起数据缓冲的作用,以至不会打断流水线作业,FPGA单周期工作流程如图5所示。

FPGA接到启动指令后,开始发送扫描天线,控制DA/AD转换,当FIFO的数据量到设定值时产生中断,通知DSP搬运数据,搬完后进入下一次启动等待。

4)数字信号处理模块。数字信号处理模块是雷达数据处理[4]的关键部件。文中采用TI公司的DSP芯片TMS320C6455[5],属于最新定点处理器,相比较以往6000系列具有更多的优点:最高频率1.2GHz;内部的RAM空间2MByte;支持DDR2的外部接口总线。

为让高主频的DSP发挥出最大的处理能力,需要减少CPU存取数据的时间和减少被低速外设打断的次数。

为此,首先DSP上电启动Bootloader之后,把程序代码拷贝到RAM内部里面,减少读取程序的时间;其次,DSP以EDMA方式搬运采样数据,搬运数据和CPU处理算法可以并行处理;另外,L2内存区内置两个数据缓冲池流水线方式处理数据;最后是把低速外设交给FPGA管理。

考虑软件算法以后的升级,TMS320C6455芯片有专门的 DDR2[6]接口管脚,外接两片 MT47H64M16 DDR2芯片构成32位DDR2内存,此时雷达数据的缓冲可以设置在DDR2里面,让L2 RAM只用作程序代码空间,从而提高运行速度。

通讯模块里由DSP的McBSP通道设置成SPI方式;外部接MAX3100芯片把SPI转换成UART方式。数字信号处理模块完成动目标轨迹解算后,以串口方式把动目标的参数发送给控制系统实施攻击。

5)电源管理模块。电源管理是高速信号处理板的重要部分,电源的电磁兼容性、纹波大小直接系统影响目标信号处理器的各种性能指标,目标信号处理器的电磁兼容有以下特征:

ⓐDSP芯片与外部DDR2总线的运行主频比较高,易形成电磁干扰;

图5 FPGA单周期工作流程

ⓑ算法对叠加在模拟信号上的噪声比较敏感,易受干扰;

AD、DA芯片内部数字地和模拟地是连通的,工作时钟信号容易干扰AD前端(DA后端)的模拟信号。当时钟信号通过耦合方式混叠在模拟信号时,由于叠加干扰噪声将出现混频现象,引起解算后出现“野点”,导致目标航迹跟踪失败。

因此,需从以下几方面考虑抑制电磁干扰:

ⓐ数字/模拟电源和地分开走线,选择恰当的共地点;

ⓑ模拟电源利用DC/DC电源芯片与线性电源两级串联结合供电,既起到降低功耗,又降低电源噪声的效果;

ⓒAD、DA芯片数字地、模拟地分别用磁珠连接,设置地壕沟防止数字信号电流经过模拟地回流;

ⓓ设计上电时序控制电路,控制端口电压、核电压、锁相环电压上电时序,避免因上电时序错误造成的启动失败;其次控制系统的上电就绪时间;最后是防止上电瞬间电流过大(电源芯片以电荷泵方式工作和FPGA程序没有加载程序导致用的电流较大),拉低系统电压,导致其它部件多次复位。

图6 流水线工作原理简图

2.2 流水线处理数据

为了实现流水线方式,需要在DSP的L2级RAM(2Mbyte)设置2个数据缓冲区,保存上、下组天线扫描的数据,容量根据

采样数据的大小而定;同时在FPGA设置个乒乓结构FIFO数据缓冲池,如图6所示。

流水线工作方式:

1)首先DSP启动初始0组“开始指令”采集一组数据放置1#池;

2)接着DSP发送第1组“开始指令”,之后DSP处理1#数据,采集工作同时进行;

3)第1组数据存放在2#池;

4)接着DSP发送2组“开始指令”,之后DSP处理2#数据;

5)第2组数据存放在1#池;

6)重复2)步骤。

直到接收到控制系统“结束扫描”指令,跳出循环。

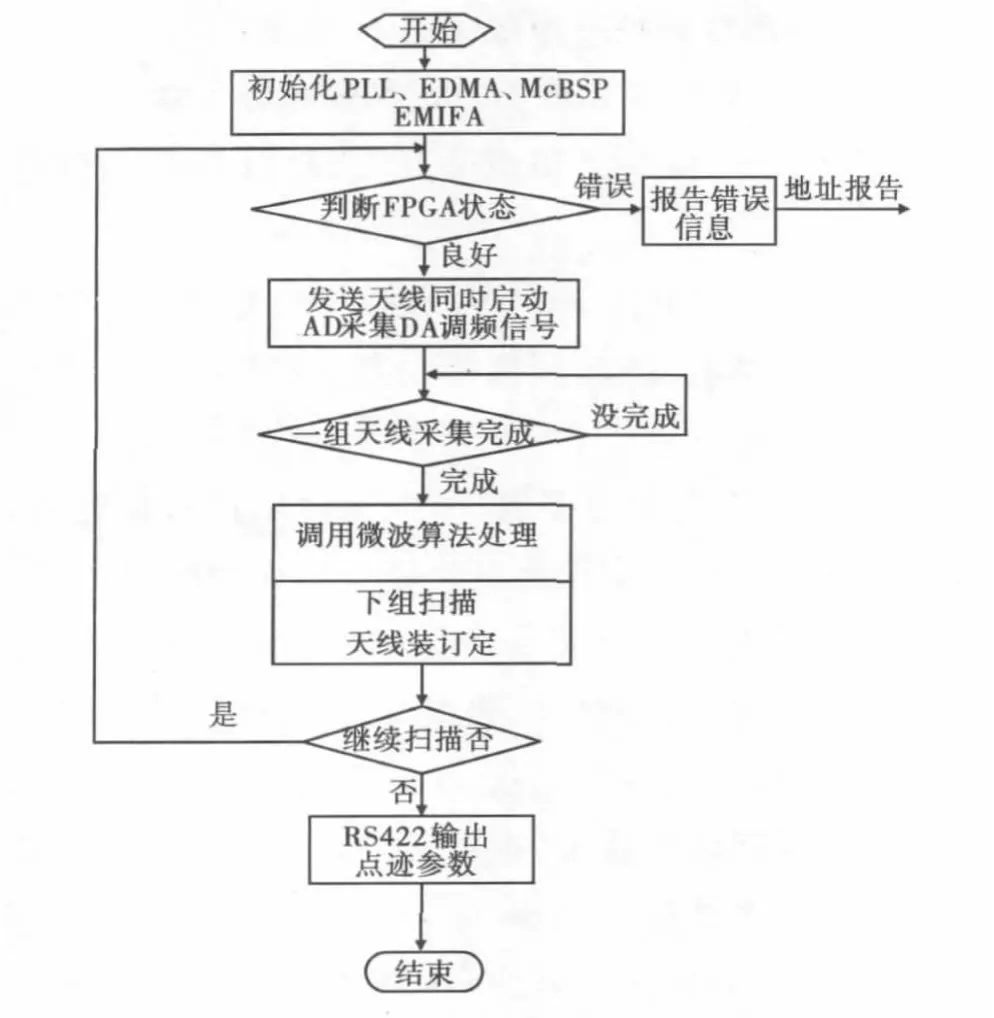

目标信号处理器的软件流程如图7所示,动目标跟踪算法做成函数形式供主程序调用。跟踪算法主要涉及数字虑波、FFT快速傅里叶变换、卡尔曼航迹预估算法;其中利用周期内FFT变换和多个三角波周期平均的方法解算出动目标的点迹参数,再以此点迹为数据进行卡尔曼航迹预估,求解跟踪轨迹。

图7 DSP内部流程图

3 试验结果

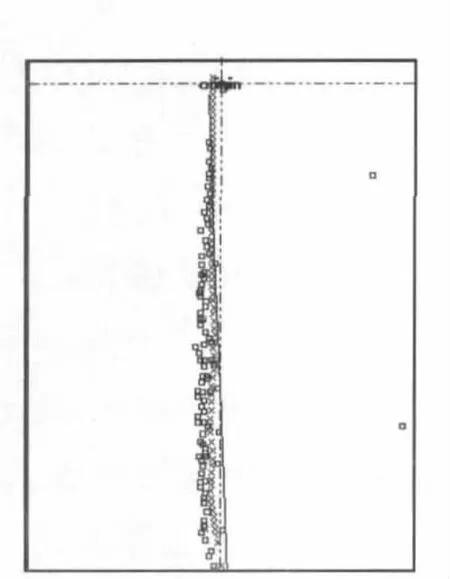

试验环境情况:在动目标(汽车)上安装 GPS定位系统,雷达探测器放在公路的旁边,目标在400mm处,以30km/s速度向探测器方向行使,雷达进行单周16个天线组扫描,目标信号处理器把解算出来点迹、跟踪参数、GPS定位数据同时输出到记录装置,结果如图 8所示。

图8 动目标点击、航迹及GPS图

在图8中左边‘□’表示动目标的点迹;中间‘×’表示动目标的跟踪轨迹;右边直线表示GPS探测到目标运动轨迹。

图8中看出“野点”很少,零散的“野点”分布不影响跟踪轨迹拟合,效果比较理想。

但存在不足之处:一是在目标距离较远时,点迹分布比较散;二是跟踪轨迹与GPS测量的真实轨迹之间存在固定角度误差。分析其原因:1)距离较远时采样信号幅值减弱,信噪比下降;2)测角用到和差法计算,两通道的不平衡性造成小角度系统误差。这部分工作进一步完善硬件电路和软件算法数据补偿后,将会取得良好的效果。

4 结论

文中目标信号处理器的设计方案具有实时性强、结构合理、工作稳定、方便硬件升级等优点;试验表明:动目标轨迹探测试验显著,在工程上能够进一步推广,满足地面近距离动目标探测系统。

[1]丁鹭飞,耿富录.雷达原理[M].3版.西安:西安电子科技大学出版社,2005.

[2]于风芹.TMS320C6000 DSP结构原理与硬件设计[M].北京:北京航空航天大学出版社,2008.

[3]黑蕾,程刚.基于某测高雷达的数字信号处理器研究[J].弹箭与制导学报,2009,29(3):269 -272.

[4]何友,修建娟,张晶炜,等 雷达数据处理及应用[M].北京:电子工业出版社,2006.

[5]MS320C6455 Fixed-Point Digital Signal Processor[M].TI公司.

[6]TMS320C645x DSP DR2 Memory Controller Use’s Guide[M].TI公司.