大型三维真彩色喷墨控制系统

刘景泰 石涛 王鸿鹏 陈新伟 林森

(南开大学机器人与信息自动化研究所,天津 300071)

0 引言

近年来,由于市场的推动,二维平面喷绘得到了长足的发展,喷绘技术也随之提高,主要集中在提高喷绘速度和提高喷墨头每英寸所打印的点数(dots per inch,DPI)上。三维喷绘技术在发展上没有标志性的成果出现,主要的技术瓶颈在于三维喷绘机械结构复杂,喷墨头向多喷嘴、大体积方向发展也不利于三维喷绘技术的发展[1]。

南开大学机器人与信息自动化研究所从2007年3月起着手利用国产RH6通用工业机器人进行三维真彩色喷绘系统原型机理的研究,积累了一定的前期经验[2-3]。根据三维喷绘的作业需求,系统要控制青、品 红、黄、黑 (cyan、magenta、yellow、black,CMYK)四色喷头在三维模型表面高速、准确地喷上每个点位对应的颜色。现有的喷墨打印机虽然技术成熟,但是它是一个封闭的技术,只能用于平面打印,无法进行三维喷绘。项目组前期基于RH6工业机器人的样机,其底层喷墨控制采用ARM处理器完成,通过定时器中断控制GPIO来模拟喷墨时序。由于定时器资源有限,且受中断响应频率限制,该方法存在喷墨频率低、时序边沿无法严格对齐、容易造成误喷、灵活性不够等缺点。

为了解决以上问题,本文采用高度灵活的FPGA作为主控模块,利用FPGA丰富的逻辑资源对喷墨过程进行硬件加速[4-5],同时发挥FPGA并行处理能力,通过IP核复用来控制多路喷头[6-7]。真彩色喷墨控制系统是三维喷绘机器人的重要组成部分之一,是三维喷绘中的核心技术。因此,研究真彩色喷墨控制系统具有重要的意义。

1 系统总体结构设计

三维真彩色喷墨控制系统作为三维喷绘机器人的一个子系统,与七轴运动控制子系统、负压供墨子系统一起协调完成三维模型的喷绘作业过程。它的主要功能是在三维喷绘机器人运动过程中,根据影像数据产生相应的CMYK四路喷头控制信号,控制四个喷头在每个点位喷出相应的颜色数据。

三维真彩色喷墨控制系统由上位机、PMAC运动控制卡、FPGA主控单元、喷墨控制接口板和喷头组成,其体系结构如图1所示。

图1 喷墨控制系统体系结构Fig.1 Architecture of the inkjet control system

图1中,位置触发信号是在喷头运动过程中产生的,对应着机器人电机上码盘的真实位置信息,位置触发的精度为单位墨滴的直径。这样就保证了喷头在运动过程中的每一个位置都能喷上该点对应的真实影像数据。由图1可知,上位机通过以太网与FPGA主控单元进行交互,给FPGA发送喷墨影像数据和任务级的控制命令。PMAC运动控制卡产生位置触发信号,作为中断源接入FPGA。FPGA主控单元采用Xilinx的Virtex-II Pro系列 FPGA,以内嵌的PowerPC405硬核处理器为中心,通过移植Xilkernel嵌入式操作系统和LwIP网络协议,搭建了一个多任务实时处理平台,使系统具有灵活的任务调度功能。FPGA主控单元对待喷影像数据进行解析,并在上位机的命令控制下,按照位置触发信号的节拍,产生四路喷头时序控制信号,经喷墨控制接口板转换成喷头正常工作电平,从而驱动CMYK四色喷头执行喷墨动作。

2 硬件系统设计

2.1 FPGA硬件平台搭建

随着自动化技术的发展,FPGA已经不局限于逻辑处理功能,而是兼具控制和数字信号处理功能。目前很多FPGA芯片都内置了硬IP核,如32位硬核处理器、存储器、数字时钟管理器(digital clock manager,DCM)、锁相环(phase-locked loop,PLL)、DSP 单元等[8]。这使得FPGA能更方便地应用于嵌入式系统控制。

本系统采用Xilinx公司的Virtex-II Pro FPGA作为主控单元,它内置了32位的PowerPC405硬核处理器,最高频率达到300 MHz;采用CoreConnect总线结构,有处理器内部总线(process local bus,PLB)和片上外围总线(on-chip peripheral bus,OPB)两种形式,PLB 总线频率高达100 MHz,用来连接双倍速率(double data rate,DDR)内存控制器等高速设备,OPB总线用来连接UART等相对低速率的外围设备[9]。

根据三维真彩色喷墨控制系统的需求,在FPGA中以PowerPC405处理器为核心,添加喷墨控制需要用到的各种外围IP核,搭建如图2所示的硬件平台。

图2 FPGA中硬件平台结构图Fig.2 Structure of the hardware platform in FPGA

图2中,硬件平台主要包括10/100 Mbit/s以太网、DDR内存控制器、SystemACE_CF控制器、中断控制器、GPIO控制器和Opb_xj64 IP核。其中,10/100 Mbit/s以太网用来传输高速影像数据,并与PC进行命令交互。系统配备了256 MB的DDR,用于存储影像数据,DDR内存控制器提供DDR读写访问接口,喷头每次喷墨时从DDR中相应地址取数,DDR高效的读写性能保证了喷墨数据装载的实时性。SystemACE_CF是CF卡控制器,系统采用了1个2 GB的CF卡。CF卡有两个用途:一是FPGA配置文件存储在CF卡中,上电之后自动对FPGA重配置;二是在CF卡上建立一个小型文件系统,可以方便地存取文件。中断控制器接收PMAC运动控制卡发出的位置触发信号,产生中断信号,交给PowerPC405进行处理。GPIO控制器实现对板载LED灯等通用I/O口的控制。Opb_xj64是自主设计的喷头时序控制IP核,它是专门用来控制喷头喷墨的标准化模块,1个Opb_xj64 IP核控制1个喷头。系统对该模块进行了复用,采用4个Opb_xj64 IP核实现对CMYK四色喷头的控制。

2.2 喷头时序控制IP核设计

在三维真彩色喷绘系统中,由于三维模型的限制,同一时刻进行喷绘的若干点的高度数据不一致会导致喷嘴到该点的距离也不一致。一般地,体积越大的喷墨头,在进行三维喷绘过程中,喷墨头距离被喷模型的平均距离越大,喷墨效果越差。因此,在喷墨头选型中,我们希望能够使用体积相对较小的喷墨头。Xaar公司早期推出的xj64喷墨头拥有64个喷嘴,是目前市面上可见的体积较小的压电式喷墨头,分辨率为185像素/英寸(1英寸=25.4 mm),适合三维喷绘,所以本系统选择xj64型喷头。

xj64喷头工作时钟为1 MHz,具有特定的串行送数时序,在SCK信号的同步下,将64 bit数据串行移位写入内部寄存器,然后等待Nfire信号,如果Nfire变低,则喷头执行一次喷墨动作,喷出64 bit数据。本文设计了一个满足喷头控制信号时序逻辑的IP核Opb_xj64,使用VHDL编写,采用同步时序设计方法,避免了由于竞争冒险引起的毛刺现象,且各功能模块具有统一的复位信号,消除了系统启动时的不确定状态[10]。Opb_xj64采用模块化的设计,主要包括两大功能模块的设计:OPB_IPIF接口模块(OPB总线接口)和xj64时序逻辑模块(喷绘时序逻辑)。Opb_xj64结构如图3所示。

图3 Opb_xj64结构图Fig.3 Structure of Opb_xj64

图3中,OPB_IPIF接口模块实现OPB总线读写寄存器和访问FIFO接口等操作。喷头执行一次喷墨动作的64 bit数据通过OPB总线发送给Opb_xj64,然后,xj64时序逻辑模块将该64 bit数据转换为符合喷头时序规范的串行数据流,从而驱动喷头执行一次喷墨动作。同时,xj64时序逻辑模块对喷头反馈信号进行检测,如果喷头温度过高,则停止喷墨,并向上反馈error信号。喷绘时序控制信号由状态机产生,状态转换图如图4所示,包括“空闲”、“开始”、“装载低32位数据”、“装载高32位数据”、“等待 Ready信号”、“设置Nfire信号”、“停止”这7个状态。

图4 状态转换图Fig.4 State transition diagram

2.3 喷墨控制接口板设计

本系统设计了一个喷墨控制接口板,用来连接喷头和FPGA控制板。FPGA产生的喷墨时序控制信号经过排线连接到喷墨控制接口板,接口板提供了4路喷头接口,通过4根柔性扁平电缆(flexible flat cable,FFC)连接到喷头。

喷墨控制接口板主要包括电源控制模块和电平转换模块两个模块。电源控制模块用于提供喷头所需的3种输入电源:35 V直流电源VPPH(高电流)、35 V直流电源VPPL(低电流、低噪声)和5 V逻辑电源VDD。同时对它们的上电和掉电时序进行控制,避免出现由于上电或掉电时序错误造成的喷头电路烧毁现象。系统使用继电器对上电和掉电顺序进行控制:5 V电源上电稳定后才加载35 V电源;35 V电源完全掉电稳定后5 V电源才掉电。由于FPGA主控模块中Opb_xj64 IP核产生的喷墨时序信号都是3.3 V的LVTTL信号,而驱动喷头的控制信号和喷头反馈回来的nFault信号都是5 V的CMOS信号,所以还需进行电平转换。电平转换模块采用SN74LVC4245芯片完成LVTTL电平与CMOS电平之间的转换。

3 软件系统设计

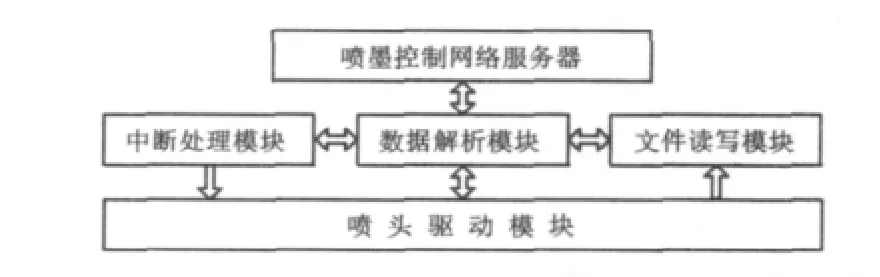

综合考虑系统的复杂程度和实时性要求,选择Xilkernel操作系统,它具有嵌入式内核完整的功能,支持POSIX开放结构,而且占用CPU资源较少,运行速度快,是中小型设计的理想操作系统。Xilkernel本身不带有文件系统处理与TCP/IP协议栈,但它与LwIP具有良好的接口,加上CF卡中的FAT文件系统,可以形成比较复杂的嵌入式系统,满足三维喷绘底层软件的控制需求。按照自顶向下的设计方法,将喷墨控制底层软件分为喷墨控制网络服务器、中断处理模块、数据解析模块、文件读写模块、喷头驱动模块5个组成部分,软件架构如图5所示。系统采用多线程来处理各个不同的任务,提高了软件处理能力。

图5 喷墨控制底层软件架构图Fig.5 Framework of bottom layer software of inkjet control

喷墨控制网络服务器在FPGA中搭建TCP服务器,提供完整的Socket访问接口。服务器负责与上位机交互,接收上位机的连接请求,并接收来自上层三维喷绘一体化软件的任务级喷墨命令和高速影像数据,同时,将确认信号和系统运行状态反馈给上位机。

中断处理模块中的PMAC运动控制卡会根据真实位置信息,在每个喷墨点位产生1个位置触发信号。该信号作为中断源接入到中断控制器,中断处理模块从DDR缓存中读取该点位的影像数据,并发送给喷头驱动模块,从而完成该位置的喷墨过程。

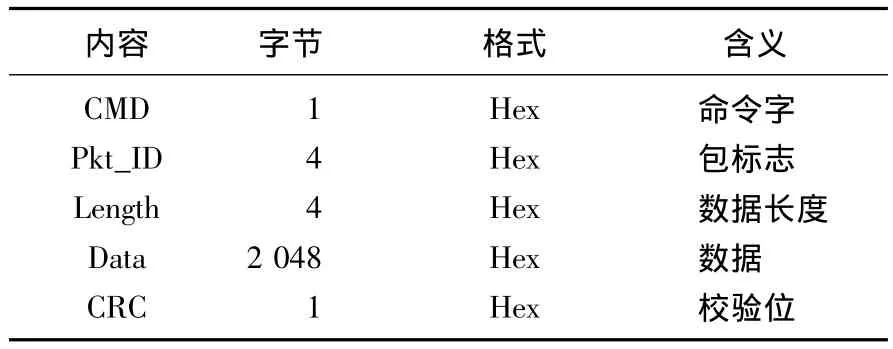

针对上位机与喷墨控制网络服务器之间的网络通信,制定了特定的数据包协议,定义了开始喷墨、停止喷墨、清除缓存、数据传输、喷头初始化等十几种命令。数据解析模块负责对接收到的数据包进行拆包解析,提取影像数据存入DDR缓存中或者执行喷头初始化等命令。数据包分为命令数据包和确认数据包两种。其中,命令数据包由上位机发送给FPGA主控单元,确认数据包由FPGA主控单元发送给上位机。数据包格式分别如表1和表2所示,每个命令数据包都对应着1个确认数据包。

表1 命令数据包格式Tab.1 Format of the command data packet

表2 确认数据包格式Tab.2 Format of the acknowledgment data packet

文件读写模块提供辅助功能,负责读取存储在CF卡文件系统中的离线文件,同时将系统工作过程中的相关状态,以日志文件的形式写入CF卡文件系统,方便对系统运行状况进行监督和调试。

喷头驱动模块是IP核Opb_xj64的驱动程序,是联系喷头硬件和控制软件的桥梁,它为软件提供访问接口。驱动模块提供喷头复位(xj64_mReset)、判断喷头是否忙(xj64_isBusy)、喷头装载数据(xj64_loadData)和一次喷墨(once3dPrint64bit)等操作。

4 仿真与试验

4.1 喷墨控制时序仿真

在ModelSim软件中对喷墨时序控制IP核进行仿真。将64 bit测试数据64’hFFFF0000FF0F0F0F发送给喷头,每一个比特位对应喷头的一个喷嘴。从仿真结果可以看到,串行数据流逻辑与喷头数据表一致,串行时钟达到1 MHz,数据与时钟边沿对齐,满足建立时间、保持时间等约束条件。

4.2 三维喷绘试验

根据前面所述软硬件设计方法进行硬件综合、应用程序编译和FPGA配置比特流生成,并下载到FPGA芯片中。最后,将本文设计的大型三维真彩色喷墨控制系统应用于三维喷绘机器人,在雕刻好的三维模型上进行喷绘试验。从喷绘试验结果可以看出,本系统喷绘出的三维真彩色模型可以很好地与实际地形匹配,且色彩还原度较高。

5 结束语

本文设计的大型三维真彩色喷墨控制系统,软硬件都可重配置,具有高度灵活性和可扩展性。同时,本文设计了喷墨时序控制IP核,通过IP核的复用,可以支持CMYK四路喷头,甚至更多;喷墨时序逻辑采用FPGA硬件实现,保证了高速喷墨过程的准确性和实时性。试验证明,本系统能够很好地满足三维真彩色喷绘作业的需求,在一定程度上促进了三维喷绘行业的发展。

[1]Sun Lei,Chen Xinwei,Liu Jingtai,et al.3D terrain model approach by an industrial robot[C]//Proceedings of the 7th World Congress on Intelligent Control and Automation(WCICA),2008:320 -326.

[2]陈新伟.三维喷绘机器人喷墨机理研究[D].天津:南开大学,2009.

[3]Niu Xuejuan,Liu Jingtai,Sun Lei,et al.Robot 3D sculpturing based on extracted NURBS[C]//IEEE International Conference on Robotics and Biomimetics(ROBIO),2007.

[4]Monmasson E,Cirstea M N.FPGA design methodology for industrial control systems—a review[J].IEEE Transactions on Industrial Electronics,2007,54(4):1 -19.

[5]林键,黄轶伦.面向喷墨打印机的高速数据处理系统[J].计算机工程,2010,36(23):1 -3.

[6]Sridharan K,Priya T K.The design of a hardware accelerator for real-time complete visibility graph construction and efficient FPGA implementation[J].IEEE Transactions on Industrial Electronics,2005,52(4):1185 -1187.

[7]Li Tzuuhseng S,Chang Shihjie,Chen Yixiang.Implementation of human-like driving skills by autonomous fuzzy behavior control on an FPGA-based car-like mobile robot[J].IEEE Transactions on Industrial Electronics,2003,50(5):867 -880.

[8]薛小刚,葛毅敏.Xilinx ISE 9.x FPGA/CPLD 设计指南[M].北京:人民邮电出版社,2007.

[9]杨强浩.基于EDK的FPGA嵌入式系统开发[M].北京:机械工业出版社,2008.

[10]He Yi,Li Changbin,Lang Zheyan,et al.Research on implementation of fuzzy logic control arithmetic based on FPGA[C]//Proceedings of the 8th World Congress on Intelligent Control and Automation(WCICA),2010:4608 -4613.