低压差分信号接口的优化设计

宁合伟 甄国涌 任勇峰

(中北大学电子测试技术国家重点实验室,山西 太原 030051)

0 引言

低压差分信号(low-voltage differencial signal,LVDS)是一种小振幅差分信号技术,它使用幅值非常低的信号(约350 mV)通过一对差分PCB走线或平衡电缆传输数据。LVDS信号的幅值很小,因此信号的转换更快,能以高达数百兆比特每秒的速度传输串行数据[1];其特有的低振幅和恒流源模式驱动只产生极低的噪声,消耗非常小的功率。此外,由于LVDS以差分方式传输数据,对共模噪声有更好的抑制能力[2]。因此,LVDS接口在高速大容量数据传输方面越来越受到人们的重视。

由于LVDS的低幅值特性,其信号本身只能满足短距离(不超过几米)传输条件下数据高速传输的要求[3]。当传输距离较远时,LVDS接口就会很容易失锁。本文结合具体工程,分别从接口的电路和逻辑两方面对该问题进行分析,并给出优化的设计方法。

1 工程背景

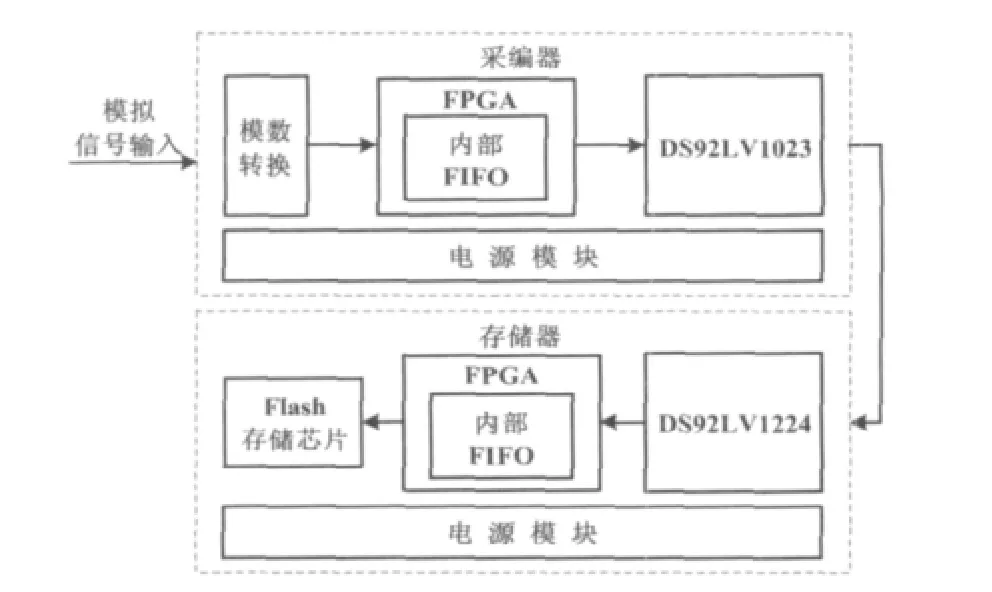

在某数据采集装置中,使用LVDS接口作为数据通信接口,原理如图1所示。

图1 数据采集装置原理图Fig.1 Principle of the data acquisition device

在该数据采集装置中,采编器接收外界的模拟信号,通过高速模数转换器转换为数字信号,数字信号通过LVDS接口下发到存储器进行存储。采编器到存储器的连接线采用同轴电缆,长度为5 m。当传输速度提高到62 MB/s时,LVDS接口就会很容易失锁。

2 接口电路优化设计

2.1 接口电路分析

在该接口中,LVDS串行器DS92LV1023和解串器DS92LV1224直接相连。该芯片组是美国国家半导体公司推出的10位总线型低压差分信号芯片组。DS92LV1023的发送速度最高可达660 Mbit/s,信号幅值很低,只有 290 mVp-p,信号的传输距离有限[4]:若经同轴电缆(SYV-50-3-3系列,内部导体直径0.9 mm,衰减系数≤4.0 dB/m)传输,其理论传输距离只有10 m左右[5]。

当传输距离较短时,LVDS接口的可靠性很好(当传输距离小于1 m时,芯片组没有出现过失锁的情况),且差分信号的眼图良好,经过大量的测试没有出现失锁或者丢数的现象。而当传输距离较远或者同轴电缆的特性不是很好时,经电缆传输后的信号将会衰减或错位,此时芯片组很容易出现失锁的情况。经测量,当同轴电缆的长度达到3.3 m时,芯片组开始出现失锁。

2.2 接口电路优化设计

为了克服上述问题,使信号传输得更远而芯片组不失锁,可以在接收端增加自适应电缆均衡器,对衰减后的信号进行恢复和增强。考虑到存储器的电路板很小,使用CLC006等大封装的器件是不可能的。综合考虑器件的封装、功耗和速度,选择DS15EA101作为该接口的电缆均衡器。

电缆均衡器的性能取决于发送器或电缆终端信号的幅值,对于特征阻抗为50 Ω的同轴电缆,最佳发射幅值为 800 mVp-p[6],而 DS92LV1023 的发送幅值为290 mVp-p。因此,需要在发送端增加差分驱动器,以调节输出信号的幅值。

与DS15EA101对应的差分驱动器为DS15BA101,它是一种高速差分驱动器,其输出幅值可调。当使用同轴电缆作为传输介质时,驱动器输出选择单端模式,此时输出电压控制电阻Rvo选择高精度487 Ω。这样可将电缆延长至100 m以上,但具体的传输距离仍受串行传输速率和电缆特性的影响[7-8]。增加差分驱动器和电缆均衡器后的电路如图2所示。

图2 驱动器和均衡器使用原理图Fig.2 Principle of the driver and equalizer

当同轴电缆的长度增加到15 m后,对电缆后端信号进行测量,结果显示经电缆传输后信号眼图的质量很差,有些部位的眼图即将关闭。经过均衡器的恢复和增强,眼图再次打开,经验证芯片组不会失锁。

高速信号传输的阻抗匹配是很重要的,图2所示原理图中的电阻R1、R2为阻抗匹配电阻,要求使用高精度电阻。当使用特征阻抗为50 Ω的同轴电缆作为传输介质时,其阻值分别为50 Ω和25 Ω。经过优化后的接口电路在长距离传输中很少出现失锁的情况。

3 通信协议分析及逻辑的优化设计

3.1 LVDS接口通信协议

在该数据采集装置中,如果输入的模拟信号在一段时间内保持不变,尽管对接口的电路进行了优化设计,但LVDS接口偶尔也会失锁。下面从接口逻辑的角度分析该问题。

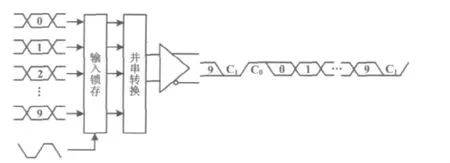

LVDS接口通信为同步串行通信,采用起始位和结束位的形式来传输串行的数据流。LVDS的通信协议如图4所示,其中C0为起始位,C1为结束位[9]。

图3 LVDS通信协议示意图Fig.3 Schematic of LVDS communication protocol

发送端将数据和时钟信号一起发送到锁存单元,并串转换单元将两个时钟位(一高一低)内嵌在串行的数据流中,组成串行数据起始位和结束位,产生周期性的上升沿。当发送数据时,接收器自动搜索内嵌时钟的上升沿。由于数据位的值是变化的,而时钟位是不变的,因此接收器可以从串行数据流中检测到时钟的上升沿,从而同步。如果发送端重复发送相同的某种数据,接收器可能将数据位的上升沿错误地判断为时钟位的上升沿,造成接收器假锁,从而导致失锁[10]。

模数转换芯片的的输出为8位,而串行器的输出为10位,高两位通过硬件将其拉为高电平。当有数据要发送时,控制芯片发出时钟信号,芯片组进行同步(消耗至少512个时钟周期进行同步),当同步信号变低后,控制芯片将数据和时钟同步输出;当没有数据发送时,控制芯片停止发送时钟信号,LVDS芯片组失锁。再次发送数据之前芯片组要重新进行同步。

当输入的模拟信号不变或者变化缓慢时,转换后的数字信号在一段时间内将保持不变。分析LVDS通信协议可知,芯片组同步的机理在于时钟检测电路检测到串行数据流中的时钟位即周期性的上升沿。当发送相同的数据,如发送二进制数11000011时,时钟检测电路会将第二位到第一位的上升沿误认为时钟的上升沿。此时将会有多个上升沿,芯片组将不同步,时钟检测电路继续查找下一帧数据中的时钟上升沿,直到芯片组同步。因此,当输入的模拟信号在一定时间内保持不变或者变化缓慢时,芯片组失锁是有可能的。

3.2 逻辑优化设计

由以上分析可知,要解决LVDS芯片组失锁的问题,除硬件的正确可靠外还需要逻辑的配合。为了避免由于发送的数据相同而出现的失锁现象,可以考虑每次发送的数据都不一样。在发送完一帧数据后,紧接着发送该帧的反码,依次下去,这样可以保证相同帧的长度最大为2,从而避免失锁现象的出现。但是这样将降低有效数据的发送速度,如果要进行相同速度的发送,则主频要提高一倍。

上述方法在发送速度不高的时候是可以考虑的。当系统对传输速度要求很高时,将主频提高一倍的成本是很高的,此时需要考虑其他方法。考虑到发送的数据多为8位数据(按字节传输),而LVDS芯片组的位数为10位,其高两位为空位,因此可以将其作为标志位。当有数据(称之为有效数)发送时,标志位设为01;当没有数据发送时,发送递增数(无效数),同时将标志位设为10。这样可以保证LVDS芯片组一直处于同步状态,减少芯片组的同步建立时间。同时,标志位的变化使得10位的数据整体也是变化的,这样时钟检测电路能够将变化的数据位和不变的时钟位区分开,从而避免失锁现象的发生。

在该数据采集装置中,对输入模拟信号保持不变时的情况进行了测试,每次测试的数据容量为4 GB,共测试50次,没有出现失锁的情况,证明该方法可以有效避免由于数据位的原因而造成的芯片组失锁。

4 结束语

本文介绍了一种LVDS接口的优化设计,分别从硬件和逻辑两方面进行了分析和优化。优化后的电路在传输距离为15 m时,传输速度可以达到62 MB/s,且性能稳定可靠。

大量测试表明,优化设计后的接口很少出现失锁或丢数的现象。目前该接口已投入使用,具有很高的应用价值,值得推广。

[1]杨坤明.现代高速串行通信接口技术与应用[M].北京:电子工业出版社,2010:4-14.

[2]杨翠虹,文丰,姚宗.基于LVDS的高速数据传输系统的设计[J].通信技术,2010(9):59-60.

[3]戴萧嫣,王立恒,李圣昆,等.基于LVDS的长线传输模块设计[J].通信技术,2009(11):4-5.

[4]祝依龙,范红旗,张军.一种基于LVDS的高速串行数据传输系统设计[J].电子设计应用,2007(1):94-96.

[5]皮代军,张海勇,叶显阳,等.基于FPGA的高速实时数据采集系统设计[J].现代电子技术,2009,32(6):12-14.

[6]杜旭,于洋,黄建.基于FPGA的高速串行传输接口的设计与实现[J].计算机工程与应用,2007,43(12):94-96.

[7]张时华,任勇峰,李圣昆,等.基于FPGA和LVDS技术的光缆传输技术[J].电子设计工程,2009(3):69-70.

[8]王冰,靳学明.LVDS技术及其在多信道、高速数据传输中的应用[J].现代电子,2001(2):42-43.

[9]彭鼎之.基于LVDS高速串行数据传输的接收系统研究和设计[D].成都:电子科技大学,2011.

[10]张宇翔,王明利,吕运朋,等.高速数字存储示波器前端电路设计[J].自动化仪表,2010,31(4):66.