基于归一化LMS算法的自适应滤波器设计

张银行,杨辉媛,宋志国

(吉首大学物理与机电工程学院,湖南吉首 416000)

基于归一化LMS算法的自适应滤波器设计

张银行,杨辉媛,宋志国

(吉首大学物理与机电工程学院,湖南吉首 416000)

归一化LMS(NLMS)算法是一种变步长的LMS算法,比LMS算法具有更快的收敛速度.采用Altera公司的仿真软件DSP Builder和QUARTUSII7.2,进行归一化LMS算法的自适应滤波器的现场可编程门阵列(FPGA)设计.

NLMS算法;DSP Builder;自适应滤波器;FPGA

自适应滤波器是一种能够自动调整本身参数的特殊维纳滤波器,在设计时不需要预先知道关于输入信号和噪声的统计特性,它能够在工作的过程中逐步“了解”或估计[1]出所需的统计特性,并以此为依据自动调整自身的参数,以达到最佳滤波效果.

图1 自适应滤波器原理框图

自适应滤波器由参数可调的数字滤波器(或称为自适应处理器)和自适应算法两部分组成.自适应滤波器的一般形式如图1所示,图1中输入信号x k()加权到数字滤波器产生输出信号y k(),自适应算法调节滤波器权系数使输出y k()和滤波器期望的响应d k()之间的误差信号e k()为最小.自适应滤波器的系数受误差信号e k()的控制,根据e k()的值和自适应算法自动调整.一旦输入信号的统计规律发生了变化,滤波器能够自动跟踪输入信号的变化,自动调整滤波器的权系数,从而实现自适应过程,最终达到滤波效果[2-3].

1 NLMS算法

NLMS的迭代公式为

其中:x k()为输入信号;y k()为输出信号;d k()为期望信号;w k()为滤波器的系数;e k()为输出误差;μ为控制失调的固定收敛因子,取值范围0<μ<2;N为滤波器的阶数;γ参数是为避免xTk()x k k()过小导致步长值太小而设置的,取值范围0<γ<1.规一化LMS算法比LMS算法的计算量稍有增加,规一化LMS算法的收敛速度比LMS算法更快[4-5],因为它在使瞬时输出误差最小化时,采用了可变收敛因子[6].

2 系统建模与仿真

DSP Builder是Alltera公司推出的一个面向DSP开发的系统级工具,作为MATALB的一个Simulink工具箱(ToolBox)出现的.DSP Builder作为Simulink中的一个工具箱,使得用FPGA设计DSP系统完全可以通过Simulink的图形化界面进行,只要简单地进行DSP Builder工具箱中的模块调用即可.2.1系统建模设计

NLMS算法自适应滤波器主要由延迟器、加法器、减法器、乘法器、系数更新等模块组成.图2是7阶NLMS算法自适应滤波器的系统方框图,期望信号由sine wave1模块提供,输入信号由sine wave2和Random Bitstream叠加在一起的信号组成.系统所需的模块都是直接调用DSP builder中的模块,其中系数更新模块是一个封装的子系统,内部结构见图3.如果需要提高收敛速度,则可增加滤波器的阶数,可增加延迟模块和子系统模块.阶数的增加必定消耗更多的硬件资源,笔者给出NLMS算法的自适应滤波器的FPGA实现方法,滤波器的阶数,步长控制参数μ必须依据所应用的实际情况确定.

图2 NLMS算法自适应滤波器的系统方框图

图3 NLMS算法子系统内部框图

2.2 子系统内部模块

子系统内部模块主要由乘法器、除法器、加法器、延迟单元、总线类型转换等模块组成,主要完成滤波器的权值的更新,即和wi(k)xi(k)运算.

2.3 波形仿真

Matlab的Simulink环境具有强大的图形化仿真验证功能,用DSP Builder模块设计好一个新的模型后,可以直接在Simulink中进行算法级、系统级仿真验证.本设计的Simulink仿真如图4所示,输出信号含有毛刺,这说明输出信号与期望信号还有一定的稳态误差.可以通过增加滤波器的阶数或修改步长控制参数μ,以达到更好的效果.

运行signal complier可将通过Simulink的模块文件(.mdl)转换成硬件描述语言VHDL文件,运行Testbench(测试平台)可将sine wave1、sine wave2+noise、clock转换成针对HDL仿真器ModelSim的测试文件.ModelSim是使用最广泛的基于单内核的Verilog/VHDL混合仿真器,可方便地将信号波形显示为类似模拟信号的格式,特别适合显示复杂信号的波形.

由图4可知输出信号sine out逐渐趋于稳定,且逼近于期望信号sine wave1因此设计结果满足要求,能够实现自适应过程.图4 Simulink仿真图和图5 ModelSim功能仿真图基本一致,说明模块文件(.mdl)和VHDL文件一致.

图4 Simulink仿真

图5 ModelSim功能仿真图

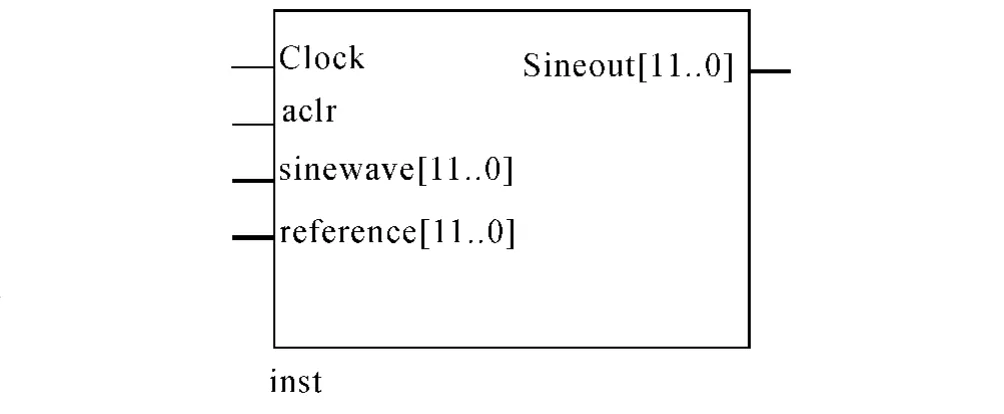

图6 NLMS算法自适应滤波器顶层模块图

RTL仿真通过以后再调用QuartusII进行综合、编译与适配,最终生成编程文件即pof文件和sof文件.7阶NLMS算法自适应滤波器共消耗EP2S30F484C3芯片Combinational ALUTs 12692个,pins 38个,logic registrator 405个,DSP block 9-bit elements 128个,整体模型对应的模块如图6所示.

3 结语

笔者给出了基于NLMS算法的自适应滤波器的FPGA实现方法,如果想达到更快的收敛速度,更小的稳态误差,只需增加子系统,延迟单元即可,笔者直接调用DSP Builder里面的模块进行设计,而不必采用硬件描述语言进行底层模块的编写,使更多的精力放在算法级的研究上.

[1] 田 耘,徐纹波,张延伟.无线通信FPGA设计[M].北京:电子工业出版社,2008.

[2] 赫 金.自适应滤波器原理[M].郑宝玉,译.第4版.北京:电子工业出版社,2003.

[3] 迪尼,著.自适应滤波算法与实现[M].刘郁林,译.第2版.北京:电子工业出版社,2004.

[4] BERSHAD N.Analysis of the Normalized LMS Algorithm with Gaussian Inputs[M].IEEE Trans.Acoust,Speech,Signal Processing,1986,ASSP-34:793-806.

[5] SLOCK D T M.On the Convergence Behavior of the LMS and the Normalized LMS Algorithms[M].IEEE Trans.Signal Processing,1993,41:2 811-2 825.

[6] TARRAB M,FEUER A.Convergence and Performance Analysis of the Normalized LMS Algorithm with Uncorrelated Gaussian Data[M].IEEE Trans.Inform.Theory,1988,IT-34:680-691.

Design of Adaptive Filter Based on the Normalized Least-Mean-Square Algorithm

ZHANG Yin-hang,YANG Hui-yuan,SONG Zhi-guo

(College of Physical Science and Mechatronic Engineering,Jishou University,Jishou 416000,Hunan China)

The convergence rate of the Normalized Least-Mean-Square(NLMS)algorithm with variable step length is higher than that of the Least-Mean-Square algorithm,and the Field Programmable Gate Array(FPGA)design of the adaptive filter using Altera DSP Builder and QUARTUS II 7.2 is accomplished.

NLMS algorithm;DSP Builder;adaptive filter;FPGA

book=104,ebook=6

TN911.72

A

10.3969/j.issn.1007-2985.2012.02.019

(责任编辑 陈炳权)

1007-2985(2012)02-0080-04

2011-12-16

吉首大学校级资助课题(11JD044)

张银行(1982-),男,河南焦作人,吉首大学物理与机电工程学院讲师,硕士,主要从事射频集成电路设计研究.