基于DSP的雷达干扰控制与处理系统

谢晓霞,傅其祥

(国防科技大学电子科学与工程学院,长沙410073)

1 引言

雷达电子战是现代信息作战中的重要部分,随着数字信号处理(DSP)芯片技术的飞速发展,各种高速处理芯片已广泛应用于各类电子对抗装备中。美国TI公司推出的TMS320C6701是具有修正的哈佛总线结构的32位浮点型通用DSP,基于此款DSP设计的雷达干扰系统控制与处理器是某干扰机的核心部分。它的功能是负责整个系统(包括射频分系统、干扰信号模拟分系统、控制与信号处理分系统以及PC机)的控制、数据处理与监控。

2 TMS320C6701简介

在该DSP分系统设计中,采用美国TI公司的TMS320C6000系列32位浮点数字信号处理器TMS320C6701,其浮点运算速度可达1GFLOPS,已在众多领域中得到了充分应用。它的主要特点有:

采用了修正的哈佛总线结构,内部有一套256位的程序总线、两套32位的数据总线和一套32位的DMA专用总线。这种灵活的总线结构使得数据传输瓶颈对系统性能的限制大大缓解。

DSP核采用改进的甚长指令字(VLIW)体系结构和多流水线技术,具有8个可并行执行的功能单元,。当芯片内部8个处理单元同时运行时,其最大处理能力可以达到1336MIPs或1GFLOPS,大大提高了系统实时处理分析能力。

片上集成了大容量的高速程序存储器和数据存储器,最高可以200Mbit/s的速度访问。程序存储器为64K字节、256位宽,还可灵活设置为高速CACHE使用;数据存储器采用双存储块,每个存储块又采用多个存储体,可灵活支持8/16/32位数据读写。片上集成了32位外部存储器接口EMIF,可直接支持各种规格的 SDRAM、SBSRAM、SRAM、ROM、FLASH、FIFO 存储器。

从以上特点可知,TMS320C6701具有高速的数据吞吐能力和极高的数据处理速度,还可以实现与外部存储器的直接接口,这些特点都很好的保证了雷达干扰控制与处理分系统的实现。

3 控制与处理器设计

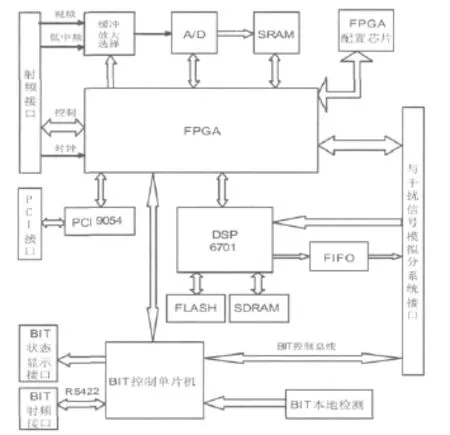

控制与处理器的功能是负责整个系统的控制、数据处理与监控。它负责的控制功能包括射频系统的控制(包括射频系统的开关控制、增益控制、频综控制、射频通道选择)、干扰控制(包括干扰样式、干扰时机等的控制);数据处理主要完成射频系统中瞬时测频接收机的测频结果的实时处理和干扰信号模拟分系统采集到的高中频信号(100MHz~500MHz)的1024点FFT(快速傅立叶变换)结果的谱分析(用来实现数字测频)。为了解决单一测频方式所带来的测频速度和测频精度之间的矛盾,本干扰机系统采用了瞬时测频与数字测频相结合的雷达信号测频技术。测频结果的分析以及利用测得的频率引导干扰则由控制与处理器的数据处理部分实现。监控功能则包括整个系统的自检以及视频信号和低中频信号(0~40MHz)的采集上传。系统可分为五个模块与三个接口:DSP模块、FPGA模块、BIT(自检 )模块、A/D模块、PCI接口模块;射频接口、干扰信号模拟分系统接口以及PCI接口,其结构框图见图1。

图1 控制与处理分系统结构框图

下面分别就各模块的设计思路进行介绍。

3.1 DSP模块

DSP模块是整个控制与处理器的核心模块,要完成整个系统的控制以及大部分的数据处理和部分监控功能。DSP模块由DSP处理器、数据存储空间以及程序存储空间几部分组成。

C6701片内有64kBytes的数据存储器和64kBytes的程序存储器,但由于系统运行过程中要存放大量数据,系统采用1片大容量的SDRAM映射到DSP的外部存储空间以存放数据。程序存放在外部非易失存储器(FLASH)中,在系统启动后被调入片内高速运行。

DSP模块通过外部中断来实现与其它模块之间的功能交互。TMS320C6701共有4个外部中断,除了一个用于DSP的复位,其它三个中断分别用来响应来自主机的控制指令,来自干扰信号模拟分系统的取数据指令和响应外部视频包络,用于干扰控制。

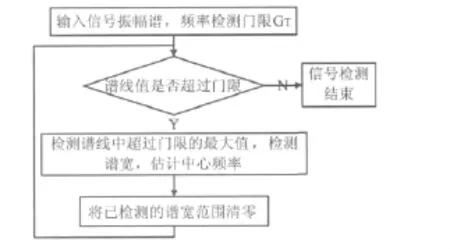

DSP模块接收来自主机的控制指令,解读后发指令给FPGA,经过FPGA译码完成对其它各模块的控制。DSP模块将接收到的射频部分的瞬时测频结果进行统计分析,在上传给主机的同时引导干扰系统对准目标频段;来自干扰信号模拟分系统的高中频信号的1024点FFT结果的谱分析也由DSP模块完成,具体的处理流程见图2所示。

图2 FFT处理流程

DSP模块完成的监控功能主要是根据主机指令设置本地自检芯片的门限电平。

3.2 A/D模块

为了实现有效干扰必须对干扰机所面临的辐射环境进行侦察。为此本系统设计了A/D模块,用来采样低中频信号和视频信号,将采样数据送给主机进行雷达信号的分选与识别。低中频信号的中心频率为30MHz,带宽为20MHz。利用100MHz A/D电路采集低中频信号,通过采集这样的中频信号经过分析处理得到信号带宽、脉内特征调制、信号时宽、重复频率等一系列参数;视频信号则通过一个40MHz的A/D电路采集得到,通过分析处理可以得到脉冲宽度和脉冲到达时间等参数。通过获得这些参数以及DSP模块分析得到的测频结果来实现对辐射源的有效识别,为干扰决策提供有利支持。

视频信号与低中频信号并不同时输入,因此通过一个二选一的高速模拟选择器选择一路信号进来,信号通过缓冲器再送给A/D,A/D采集的数据存到SRAM里面,由DSP发出指令,在FPGA的控制下将采集得到的数据通过PCI接口上传至主机。

3.3 FPGA模块

FPGA模块在控制与处理器中起到了桥梁的作用,它的主要功能是实现大量的逻辑控制电路,DSP的协处理和大量的接口电路。

FPGA模块接收DSP传送来的控制指令,对其译码后输出A/D电路的控制信号(包括高速模拟选择器的控制、A/D芯片控制与SRAM控制)、PCI接口芯片的工作模式选择信号以及总线仲裁逻辑控制;DSP的总线连接以及BIT总线连接等也由FPGA完成。利用FPGA模块C6701实现了对分系统中各电路模块的控制,使各部分可以协调工作。

3.4 BIT模块

BIT模块即系统的自检模块,它的功能是以单片机为核心,采集系统的关键测试信号,包括各种电源电压、温度、关键信号电平、主要脉冲信号的频率计数测量等,在先验知识的前提下,自动判断系统状态信息,形成告警信号,为整个干扰系统的故障定位提供信息支撑。

射频前端的BIT检测结果通过422总线实时传送给本系统,干扰信号模拟分系统的BIT检测结果通过数据与控制总线实时传送,本地检测则由片上芯片DS1780完成(它可同时监测6个模拟量,包括4个电源电压和2个温度结果)。利用单片机(51单片机)实时将系统所采集到的各种工作状态通过BIT总线送给主机用以显示与决策,同时该信号也输出到系统面板上,通过面板上的指示灯直观的看到系统工作状态正常与否。

3.5 PCI接口模块

随着ISA总线逐步被淘汰,基于PCI总线的接口设计越来越被广泛地应用于各种高速、大数据量的处理系统中。本系统采用专用 PCI接口芯片PIC9054来完成PCI接口设计。它是PLX公司推出的一种32位33MHz的PCI总线主控I/O加速器。它采用多种先进技术,使复杂的PCI接口应用设计变得相对简单。在具体的电路设计中将PCI1054的所有地址线、数据线和控制线与 PFGA连接,由FPGA完成其工作模式选择以及总线仲裁逻辑。数据传输采用的是突发方式下的DMA传输。PCI总线采用的是中断共享机制,所有PCI扩展板在PCM插槽上共用一根信号线INTA#,通过电平触发方式响应PCI中断。

3.6 接口电路

系统包括三个接口电路:射频接口、干扰信号模拟分系统接口以及PCI接口。

射频接口主要是数字信号,考虑到传输电缆相对来说较长,容易受到干扰,因此采用422差分传输方式。干扰信号模拟分系统接口为了保证数据准确传输,在数据传输口增加一个双向同步FIFO,FIFO起到缓冲的功能,提高效率与通信准确度。其内部有两个独立的FIFO存储器,两个FIFO存储器共用总线,这样的设计使得两个分系统之间的读写不发生冲突,不用总线仲裁机制,两个分系统可以同时读也可以同时写,保证数据高效准确传输。另外与干扰信号模拟分系统的接口还需要一些控制信号,这些控制信号通过FPGA与DSP连接,受到DSP的控制。PCI接口用于实现控制与处理分系统与主机的连接。PCI总线采用的是中断共享机制,主机的驱动程序利用中断使能寄存器和中断状态寄存器对中断类型进行识别,然后响应相应的中断服务子程序。

4 系统应用

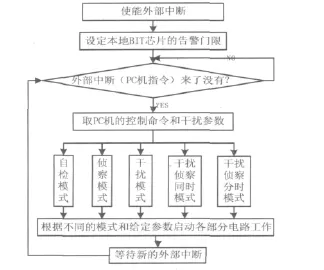

在整个系统工作时,控制与处理分系统接收来自主机的指令,完成对整个干扰系统的控制。DSP的工作流程如图3所示。

由图3,DSP工作后将所有外部中断开启,设定本地自检芯片的门限,然后开始等待外部中断(PC机指令)。操作员输入指令后,给DSP发中断,DSP响应外部中断后,首先将控制指令和干扰参数读出,然后根据读出的指令和给定的参数启动各部分电路工作。

图3 DSP工作流程图

5 结束语

基于DSP的控制与处理分系统是整个干扰系统的核心部分,可以实现整个系统干扰的控制与自检监控以及数据处理,是DSP处理技术的又一种有效应用。

[1] Texas Instrument Incorporated[Z].TMS320C6701 数据手册.

[2] 曹瑞.一种基于DSP的雷达信号实时处理系统[J].微处理机,2001(4):38-40.

[3] 于凤芹.TMS320 C6000 DSP结构原理与硬件设计[M].北京:北京航空航天大学出版社,2008.