基于 FPGA的QDPSK数字调制与解调

东北石油大学电子科学学院 李德鹏 牟海维 冯际彬 杨 成

基于 FPGA的QDPSK数字调制与解调

东北石油大学电子科学学院 李德鹏 牟海维 冯际彬 杨 成

在分析四相相对移相QDPSK信号调制解调原理的基础上,提出了一种码元判别方法,通过原理设计、 VHDL语言编程、Modelsim仿真和FGPA编程实现,完成了QDPSK数字调制解调器的电路设计,并通过下载试验,得到了良好的调制解调效果。

QDPSK;FPGA;调制解调;码元判别

QDPSK(Quadrature Differential Phase Shift Keying)通常称为正交差分相移键控[1-3],是利用前后码元之间的四种不同的相对相位变化来表示四进制数字信息的调制方式[4,5]。QDPSK调制技术是一种恒包络调制技术,受系统非线性影响小,具有较高的带宽利用率和功率利用率,目前已广泛应用于数字微波通信系统、数字卫星通信系统、宽带接入、移动通信及有线电视系统之中,成为现代通信中一种十分重要的调制方式。

1.QDPSK调制系统

1.1 基本原理

QDPSK信号可表示为:

式中:A为常数;kθ为第k个码元对应的相位,它可以取4种相位(如0、、、,从式(1)中可以看出QDPSK是一种恒包络调制。

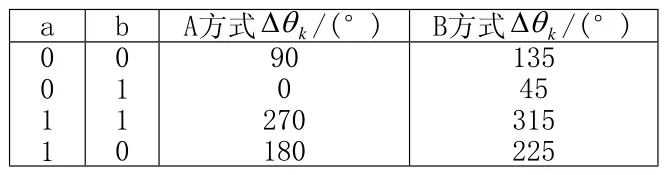

QDPSK调制系统每个码元包含2bit信息,通常被称为双比特码元,用ab代表这两个比特,它们有00、01、11和10四种组合,利用这四种不同的四进制数字信息来表示前后码元之间的四种不同的相对相位变化,则信息编码与载波相位关系可表示于表1所示。

表中kθΔ是相对于前一相邻码元的相位变化。这里有A和B两种方式,A方式中的kθΔ取值0°、90°、180°、270°;B方式中的kθΔ取值45°、135°、225°、315°。

在B方式中相邻码元间总有相位改变,故有利于在接收端提取码元同步。另外,由于其相邻码元相位的最大相移为± 1 35°,比A方式的最大相移小,故在通过频带受限的系统传输后其振幅起伏也较小。本系统即采用B方式作为调制方式。

1.2 调制器的FPGA实现方式

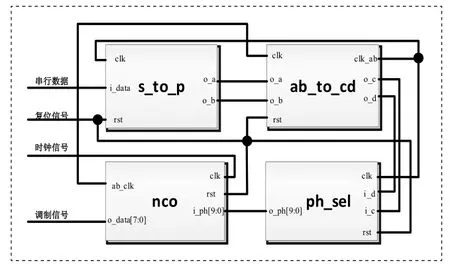

QDPSK数字调制系统的电路设计模型如图1所示。

系统调制过程为:串行输入码元i_data经过串并转换s_to_p模块后变为并行码元o_a和o_b,并行码在ab_to_cd模块中进行码变换得到差分码o_c和o_d,编码后的码元在相位选择ph_sel模块中选择载波需要输出的相位o_ph,最后由数控振荡器nco模块输出调制信号data_o。

2.QDPSK解调系统

2.1 极性比较法的改进

QDPSK信号的解调方法有极性比较法和相位比较法两类。本文在传统的极性比较法基础上根据实际工程实践进行了改进,提出了一种极性判断方法。

表1 QDPSK双比特码元与载波相位的对应关系

表2 判决规则

图1 调制系统电路模型

图2 解调系统RTL示图

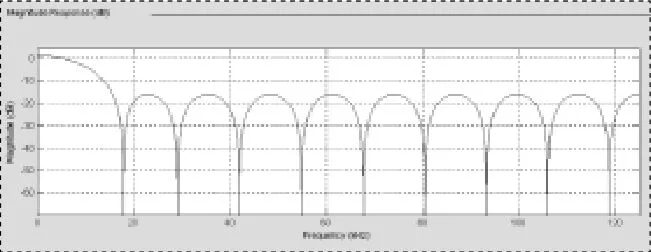

图3 FIR频率响应

图4 QDPSK调制的仿真波形

图5 解调仿真波形图

根据经低通滤波后的信号波形的特点,这里对信号进行了整形,令滤波后信号的峰值为 Af,将信号幅值大于的码元判断为+1,将信号幅值小于大于的码元判断为0,将信号幅值小于的码元判断为-1。整形后的波形通过表2所给出的判决规则即可得到码元信号的相位。

传统的QDPSK极性比较法利用的是双极性码元判决方法,该方法在极性判别完成后还需要通过锁相环提取码元同步信号进行码元判断。而本文在实际工程应用中通过增加码元一位极性的方法发现,码元在固定的同步载波相位处发生变化,并在一定时间内保持稳定,使得在码元判断中只需在同步载波信号的 0°相位处进行码元判断即可,从而避免了用锁相环提取码元同步这一步骤。该过程的实际工程仿真波形可在图5中看到。

2.2 QDPSK解调器的FPGA实现方式

解调系统的电路设计模型如图2所示。

mult为乘法器模块用于输入信号已调制信号i_data与载波同步信号i_sin和o_cos相乘,相乘后的两路信号经过filter低通滤波模块滤除载波二倍频信号,经过滤波后的信号分别经过两路操作,一路是通过锁相环ph_loop和数控振荡器vco构成载波同步模块,提取载波同步信号;另一路通过抽样判决模块sample、逆码变换模块recode和并串转换模块p_to_s得到原始的串行数据。

2.3 低通滤波器的设计

数字滤波器分为IIR滤波器和FIR滤波器。IIR滤波器设计比较简单,但难以保证线性相位。FIR滤波器虽然稍微复杂一些,但能严格保证线性相位,能够始终稳定工作。因此低通数字滤波器用FIR实现。利用matlab自带的Digital filter design工具可以自动生成FIR滤波器系数。本文设计采用的是21阶FIR滤波器,根据仿真需要采样频率为250k,通带频率为7.8k,截止频率为15.6k,其幅频相应图如图3所示。阻带衰减大于20db满足设计所需要的条件。

3.系统仿真结果

采用以上方法,选用Altera公司的主流低成本FPGA,CycloneII系列器件EP2C8Q208C8在Quartus II开发平台上对整个调制解调系统进行了综合,并利用Modelsim进行了系统仿真验证。

图4为调制系统的仿真波形,从上到下一次为载波同步时钟clk_ad,输入串行数据i_data,并行码元o_a和o_b,变换码元o_c和o_d,相对相位ph和输出调制信号o_data。

解调系统的Modelsim硬件仿真波形如图5所示。其中de_data为输入的已调制信号,o_sin为载波同步模块产生的一路正交相干载波,mu_sin为相乘后的波形,fir_sin为经过低通滤波后的波形,data_one和data_two为整形后的数据,o_a和o_b为抽样判决后的并行码元,re_data是最后解调的串行数 据。

4.结语

QDPSK调制方式是现代通信系统的一个重要数据调制方式,在抗干扰方面都优于ASK和FSK系统,特别是在抗频率选择性衰落和多径干扰方面,因此在第三代移动通信的三个国际标准中都无一例外地采取了该调制方式。FPGA使QDPSK调制系统成为一个完全的硬件构架,比用传统通信系统的处理速度快,提高了系统的可靠性,并且系统功能可以通过程序来修改和升级,具有很大的灵活性。整个系统在Quartus II环境下利用Verilog HDL语言编程实现,程序下载到FPGA芯片上,形成在线可编程嵌入式系统,不仅集成度高、功耗小、可靠性好、调试维护方便,而且形成了自己的技术内核。

[1]LINN Y.A Self-normalizing Symbol Synchronization LockDetector for QPSK and BPSK[J].IEEE Trans-actions on WirelessCommunications,2006,5(02):347-353.

[2]Floyd M.,Gardner.A BPSK/QPSK timing error detector for sampled receivers.IEEE Transaction on Communicatio ns,1986,COM-34(5):423-429.

[3]齐刚,杨燕翔.基于DSP的QPSK调制的设计与实现[J].电子设计工程,200917(1):26-27.

[4]周维龙,姚晓玲.基于FPGA的QPSK调制器的设计与实现[J].湖南冶金职业技术学院学报,2008,8(4):99-101.

[5]郭培源,李焕杰.基于FPGA的QPSK解调器设计与实现[J].北京工商大学学报(自然科学版),2005(1):37-41.

注:本文属国家大学生创新实验项目(编号:101022033)。

李德鹏(1988—),男,黑龙江牡丹江人,现就读于东北石油大学电子科学学院。

牟海维(1963—),男,黑龙江绥化人,东北石油大学电子科学学院教授,主要从事油汽井测试、信号处理等应用方面的研究。