基于Cycle True准则的算法仿真和RTL代码生成方法研究

宋 灿

(安徽理工大学 安徽 淮南 232001)

0 引言

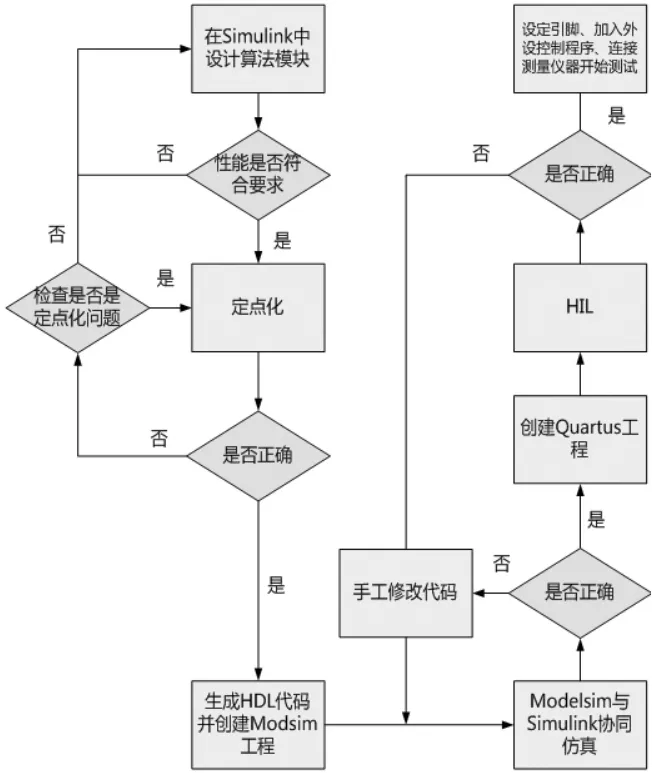

与纯粹的算法仿真不同,实现性的仿真不仅需要确定算法的正确性和性能,还需要生成实时语言硬件代码RTL。通常这种实现过程并不是直接通过手工编写的方式来实现算法的硬件代码,而是建立在部分算法仿真的基础之上。首先,在Matlab中搭建Simulink仿真模块。然后,进行数据定点化,确认无误之后可以通过HDL coder来生成硬件代码。然而生成的这些代码未必直接能在硬件平台上运行,那怕只是仿真编译都未必可以通过,这时候我们就需要后续的一系列手段来保证硬件代码生成后可以在硬件平台上顺利运行。通常我们以一个5步流水的方式来生成最后可在硬件上运行的代码。整个过程的流程图如图1所示。

图1 基于Cycle True准则的RTL代码实现的流程图

1 仿真环境介绍

为了更好地介绍硬件代码的实现过程,首先介绍一下在这个过程中需要使用到的仿真环境。整个流程中我们使用到的仿真环境主要有MATLAB是矩阵实验室(Matrix Laboratory)、Quartus II:由Altera公司针对自家生产的硬件所设计的综合性PLD开发软件、Mentor公司的ModelSim:一款HDL语言仿真软件,业界唯一的单内核支持VHDL和Verilog混合仿真的仿真器。

2 RTL代码实现流程

2.1 Matlab的理论验证和性能确定

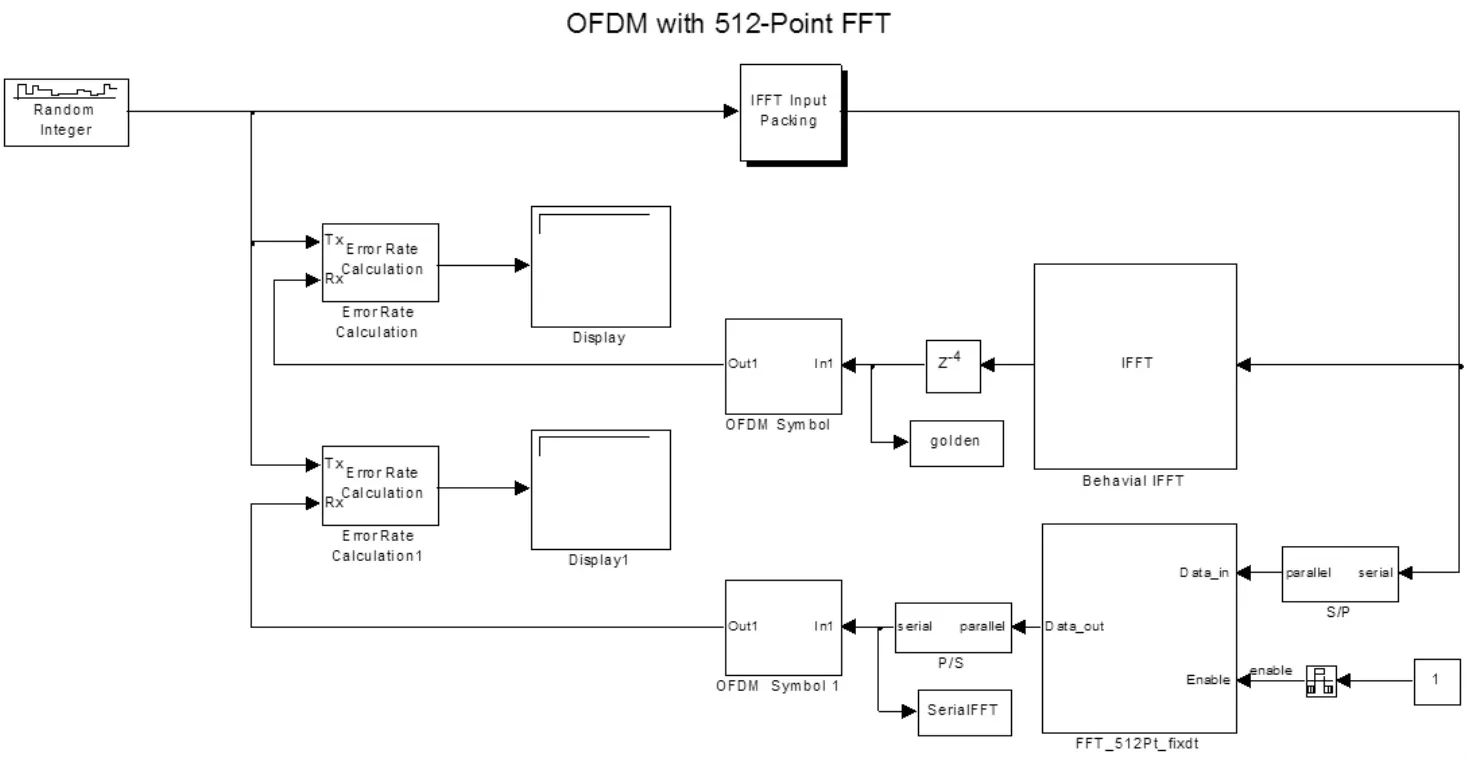

这是所有理论设计的第一步验证,通过Matlab-simulink搭建系统模型,并在仿真运行后观察系统关键位置的数据是否符合理论标准,以及确定整个算法的性能。之后的步骤不再影响或考虑性能因素,只涉及正确性问题。其中需要说明的是,理论验证一开始需要先搭建一个行为级的算法实现,每个模块直接由Simulink提供,这一步基本上就已经确定了算法本身的性能。但是这一步所实现的算法,仅仅是性能验证而已无法用来生成硬件代码。这一步得到的结果我们称之为x版或行为级模块。接下来需要通过最基本的逻辑电路来搭建一个可实现级的算法模块。这一步得到的结果我们称之为q版。以OFDM解调使用到的FFT模块为例,图2给出了FFT算法的Simulink实现以及仿真方法。

接下来,我们将x版和q版中同等位置的数据作差,如果得到的差为0则说明得到的结果相同,若结果不同结果应为±1,则说明出现了错误。对这个结果取绝对之后再循环累加来统计出先错误的次数。通常情况下我们要求累加结果一直为0。之后的每一步算法或代码实现后都要类似的与原始的x版进行比较。

图2 带有512点FFT的OFDM仿真

2.2 定点化仿真

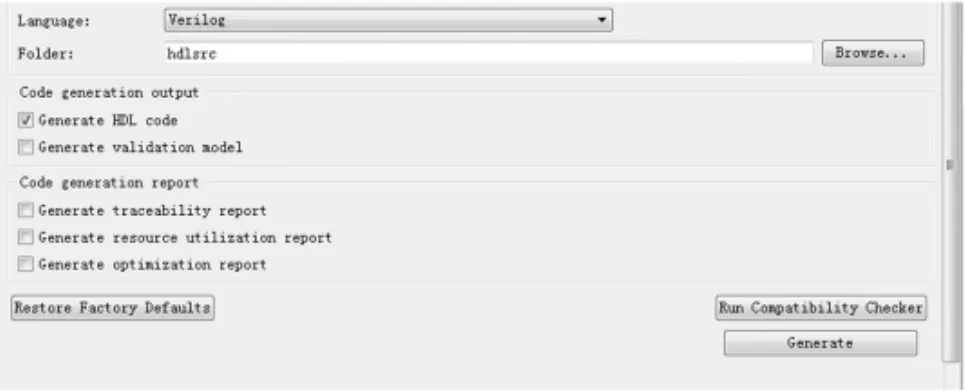

定点化:在实际硬件中信号仅可传递2进制数,因此需要一个将各输入输出节点及线路上的数据类型转化为2进制定点数表示。除此之外既然是定点数据,那么的长度也是该步骤需要考虑的问题。在对数据精度某个特定的要求情形下确定各个节点的长度,防止某些节点出现数据溢出,或必要时截断某些数据,这些步骤决定了定点化是一个工作量比较大的仿真环节。以一个无符号二进制整形数据为例,1位2进制数类型设为Boolean。十进制整数先换算成二进制 (比如144先2进制表示为10010000)从而确定其宽度为8位,因此设定类型uint8即无符号8位2进制数。值得注意的是某些电路节点的数据宽度是可变的,例如在一些反馈回路中 输出和输入的位宽不同 (比如循环累加器)并且输出信号可能再次成为输入信号,按照原有既定的输入宽度在累加到一定次数后即可能溢出。因此输入的宽度要和累加器输出最大宽度保持一致。对于有符号数或小数的则要确定小数,比如对于一个整数部分为3位小数部分为11位的一个有符号小数,则需要将数据类型选择为sfix(14,11),其中14表示总共的二进制数的位数为14,其中小数占据11位。因此我们需要将输出数据类型Output data type(如果可能的话还包括输入数据类型Input data type)由继承内部规则Inherit via internal rule改为进过计算后得出的类型。定点化所生成的模块版本成为e版。仿真运行正确后,可以使用Matlab内建工具生成HDL代码,为后面的HIL仿真和最后的硬件仿真做准备工作。在我们实际应用中生成的是Verilog HDL代码。图3给出了HDL代码的生成工具。

图3 HDL代码生成界面

2.3 Simulink与Modelsim的协同仿真

协同仿真Co-simulation是一种用到了2个或多个仿真环境的仿真方法。可以认为是软件仿真向硬件仿真的过渡。这里需要Simulink和Modelsim协同完成。Modelsim和Simulink分别调用了各自的库文件。其中Modelsim的库文件很多来自于Altera,因此和硬件库相关。而Simulink的库几乎都来自于Matlab,更贴近我们最原始的算法版本。因此可以认为这一步是由到HDL代码生成到硬件回路仿真(HIL)的过渡。验证生成的代码是否可综合。实际操作中可以用新建的cosimulation模块替换原有的e版模块。

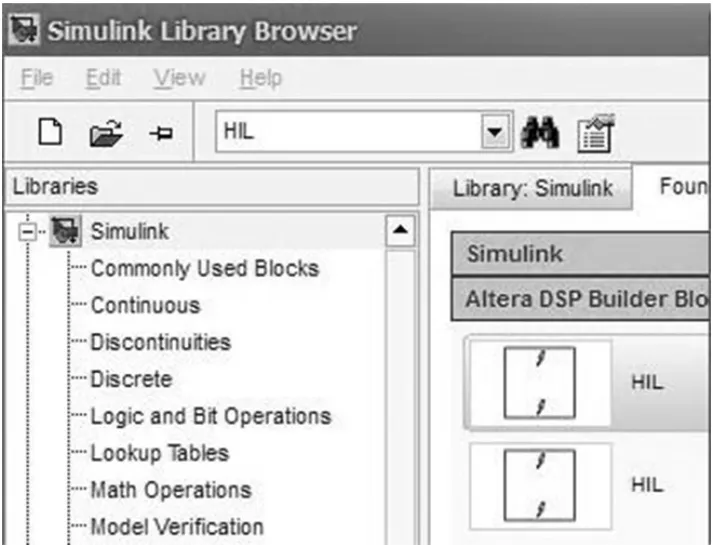

2.4 HIL

这一步称为硬件回路仿真:Hardware in the loop(HIL),是一种硬件级的仿真。我们采用的是DSP builder与QuartusII联调方式,因此也是一种协同仿真。DSP builder是Altera提供的一个基于Simulink的仿真组件。HIL模块示意图如图4所示。

图4 HIL模块

HIL被证明是一种有效的解决方法。该技术能确保在开发周期早期就完成嵌入式软件的测试。到系统整合阶段开始时,嵌入式软件测试就要比传统方法做得更彻底更全面。这样可以及早地发现问题,因此降低了解决问题的成本。HIL仍然是一种协同仿真,只是这次不同的是用到了FPGA硬件。验证编译器将HDL代码综合成硬件代码并验证是否正确。需要注意的是如果这一步可能会出现一些问题,而不同的问题反应了前面不同的地方存在着问题。硬件代码在编译综合时消耗了过长时间或无法综合说明原有代码生成工具可能存在问题,因此需要进行检查代码并手工修改。

2.5 硬件仿真

在以上各步骤均验证正确或符合性能指标之后即可进行硬件系统搭建。值得注意的是上一个步骤使用到的硬件并非完整的系统,通常只是用到了一个FPGA处理器,并不包含其他元器件。而这一步则是要对制作好的硬件pcb板在算法或功能上进行全面调试。因此除了要测试算法以外,还要对外设驱动,控制程序等做全面测试。

3 总结

在实际的工程应用中由于工作量大,细节繁琐,那么仿真过程中如果出现问题在普通的机制下往往会出现有错无从查找原因的尴尬局面。基于Cycle True准则的仿真和RTL代码生成的方法很好的保证了每个环节的正确性或可纠错性。一旦在当前步骤发现错误,可以很快的根据Cycle True准则在相关的环节中寻找错误。因此极大的提高了工作效率和可靠性。

[1]应启衍,郑君里.Matlab综合实验[M].北京:高等教育出版社,2008.

[2]冈萨雷斯.数字图像处理Matlab版[M].电子工业出版社,2005,9.

[3]Alan V.Oppenheim&John R.Buck.Discrete-Time Signal Processing[M].西安交通大学出版社,2001,9.

[4]桑吉特·米特拉.数字信号处理:基于计算机的方法[M].电子工业出版社,2011,9.