基于FPGA设计的FIR滤波器的实现与对比

崔 亮,张芝贤

(沈阳航空航天大学 电子信息工程学院,辽宁 沈阳 110136)

数字滤波器通常都是应用于修正或改变信号的属性[1]。最为普通的数字滤波器就是线性时间不变量 (LTI)滤波器。LTI与其输入信号之间相互作用,是经过一个线性卷积的过程。

LTI滤波器分为两类:IIR和FIR滤波器。在数据通讯,语音信号处理,图像处理,雷达信号处理中,不能有明显的相位失真,而有限长单位冲激相应FIR具有严格的线性相位的特点;此外,FIR滤波器的单位抽样响应序列是有限长的,因此是一个稳定的系统,故FIR滤波器在上述领域中得到广泛应用[2]。

随着现代电子技术的发展,采用FPGA(Field Programmable Gata Aarry)[3]进行数字信号处理技术得到广泛应用。以现场可编程门阵列(FPGA)为代表的ASIC器件得到迅速普及和发展。数字滤波器的设计正摆脱传统的设计模式,而采用FPGA技术来设计FIR滤波器正成为设计的趋势。目前在FPGA中用于设计FIR滤波器有很多种方法,即直接乘加结构、乘法器复用结构、乘累加结构、DA(分布式算法)。在文中是以一32阶FIR滤波器进行比较的。

1 FIR滤波器实现过程

1.1 FIR参数

这里设计的是低通滤波器,其中Fpass=23 MHz,Fstop=40 MHz, Fs=160 MHz,Apass=0.1 dB,Astop=80 dB。 通过调用MATLAB中滤波器设计的工具箱[4](FDATool),生成FIR系数。

1.2 直接乘加结构

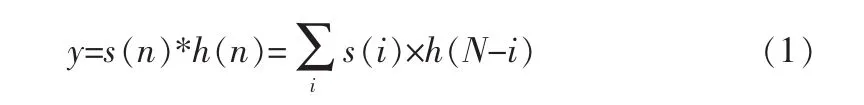

从FIR公式出发[5],可以得道fir滤波器的输出是输入数据和系数相卷积得到的,如公式(1)所示。

具有严格线性相位FIR滤波器具有对称的性质,即满足偶对称性或奇对称,在这里介绍下偶对称的结构,即满足公式(2):

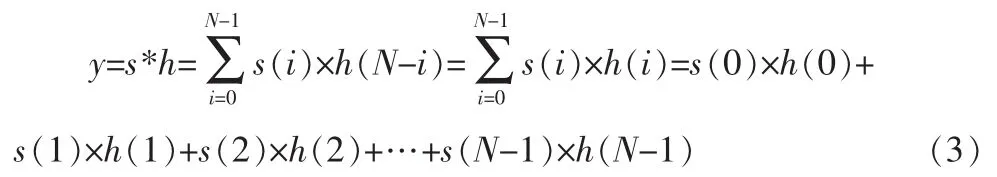

由上面讨论知道FIR的输出等于输入信号与FIR系数的卷积,如式(3)所示:

s为输入信号,h为FIR滤波器系数,N为滤波器的系数。

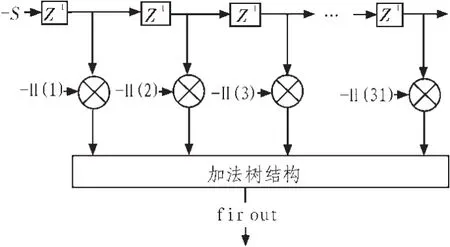

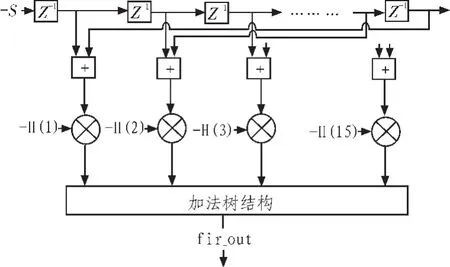

从公式可得到是把输入数据进行延迟,与系数相乘后加在一起即可得到最后输出结果。据此可以得到直接乘加结构[5],整体框架如图1所示。

输入数据通过32个延迟单元并和系数相乘,相乘后的结果通过加法树就可得到输出数据。该结构使用了32个乘法器和31个加法器。对于更高阶的滤波器,使用的乘法器和加法器更多,需要占用大量的FPGA资源。

图1 整体框架Fig.1 Overall diagram

1.3 乘法器复用结构

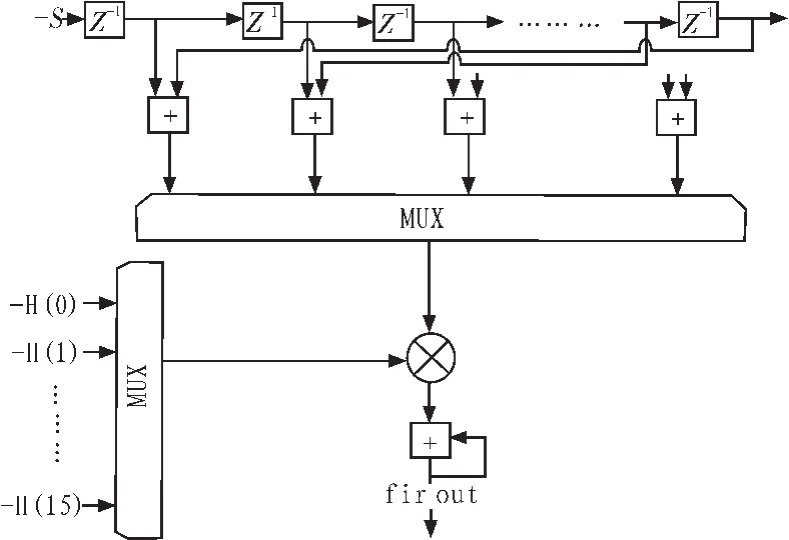

由于严格线性相位的FIR具有偶对称的性质,即h(i)=h(N-i),因此在实现中可以先进行延迟再把数据进行两两相加并与对应的系数相乘,然后通过加法树得到最终输出结果。

先定义32个寄存器用于保存通过延迟单元延时的数据,然后把寄存器中的数据进行两两相加再同系数相乘,最后通过加法树得到最后的输出结果[6]。整体框图[3]如图2所示。

图2 整体结构Fig.2 Overall diagram

该结构使用了16个乘法器和31个加法器,比直接乘加结构节省了一半的乘法器,但是如果对于阶数很多的滤波器,仍然会占用大量的资源。

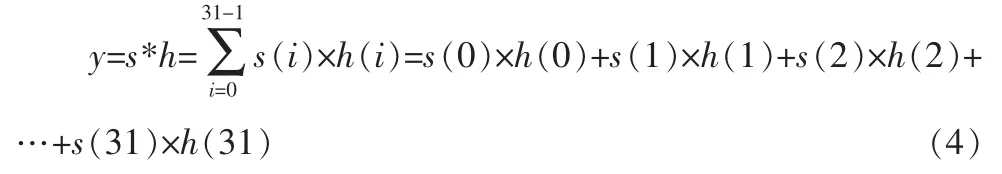

1.4 乘累加结构

乘累加结构是通过对输入数据进行延迟后先进行两两相加,再选择对应的数据和系数作为乘法器的输入数据,再把相乘后的结果通过累加器的累加得到最终的输出结果[6]。整体框图如图3所示。

图3 整体框图Fig.3 Overall diagram

通过观察框图可看出只使用了1个乘法器和1个加法器,这会节省很多的资源,相应的会造成时序控制的复杂性。

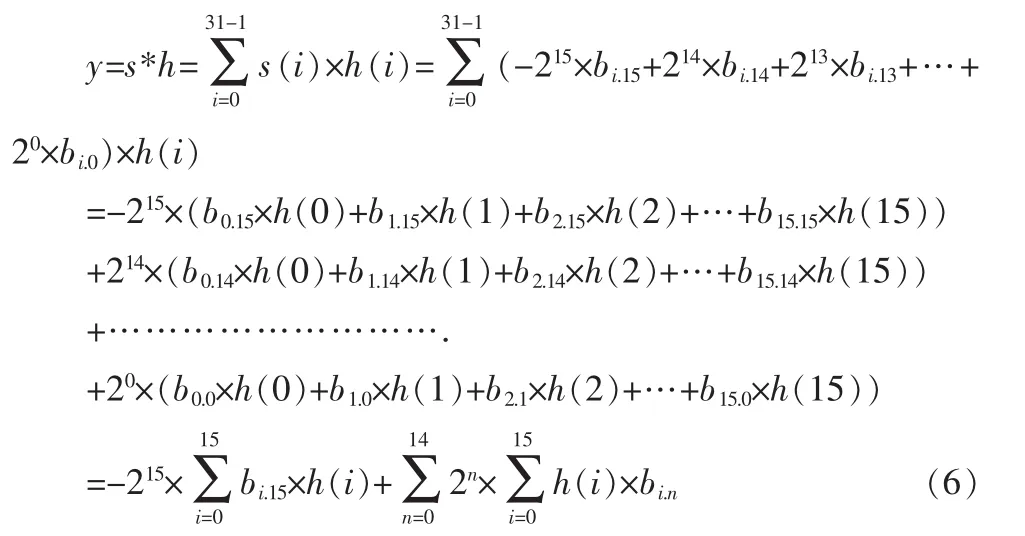

1.5 DA算法

分布式算法(DA算法)是一种以实现乘加为目的的运算方法[6]。它是在完成乘加功能时是通过将各输入数据每一对应位产生的部分积预先进行相加形成对应部分积,然后再把各部分积保存起来作为查找表的内容,通过将输入数据的每一位最为查找表的地址读出数据,再通过加法树得到最终输出结果[6]。FIR公式可用式(4)表示。

对于一个16位的有符号数,x(i)可表示为:

代入式(4)可得:

从式 (6)可看出当输入数据很多时,则查找表需要做2^16=65 536个部分积,即查找表要存储65 536个可能组合值,这个数据是很多的,不利于工程实现。因此这里可以先做一个4阶的查找表,把这4阶的查找表做成一个4阶的FIR滤波器,再把这4阶的FIR滤波器构建一个32阶的滤波器。

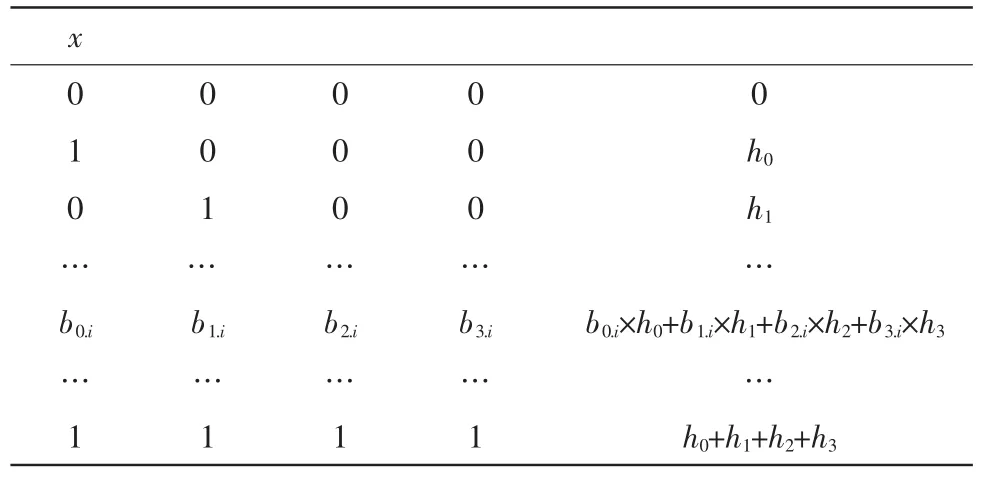

4阶FIR查找表结构如表1所示。

表1 查找表中值的设置Tab.1 Median of the lookup table setting

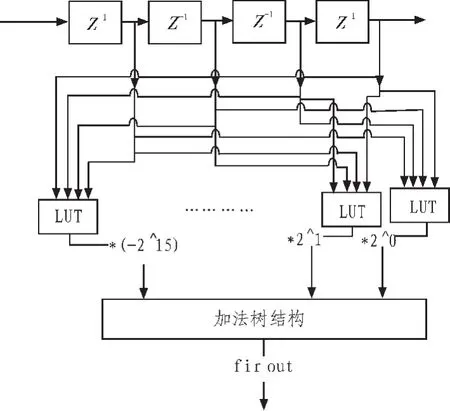

4阶的FIR整体框图结构如图4所示。

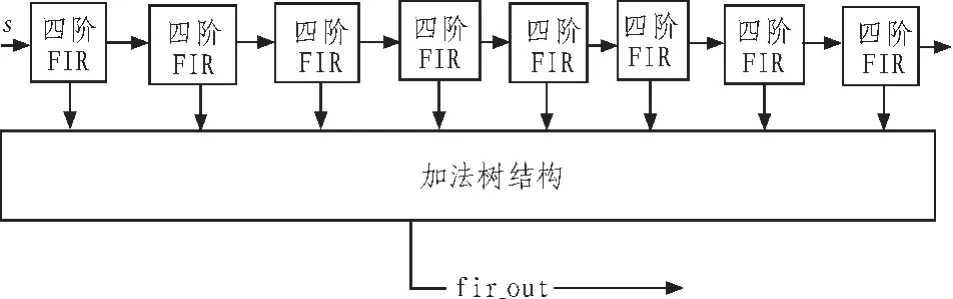

32阶FIR滤波器结构如图5所示。

DA算法仅使用加法器和查找表的结构,而不使用乘法器,这样会节省很多资源,在现在工程量很大的情况下可以节省很多资源。

1.6 资源统计表

在这里可以对上述各种实现结构做一个资源统计表如表2所示。

图4 4阶FIR框图Fig.4 Overall diagram of 4 FIR

图5 32阶FIR滤波器结框图Fig.5 Overall diagram of 32 FIR

表2 资源统计表Tab.2 Resource statistics

2 结束语

根据表格2得到乘法器复用结构比直接乘加结构会节省一半的乘法器、而乘累加结构只使用了一个乘法器、DA只使用加法器没有用到乘法器。在FPGA中乘法器会占用大量的逻辑资源,从统计表中得到DA算法虽然没有用到乘法器但是用到的资源是比较多的,相比下直接乘加结构占用的资源最较少,但是他用到了乘法器。

[1]Lyons R G.数字信号处理[M].2版.朱光明,译.北京:机械工业出版社,2006.

[2]余琳,黄光明.基于FPGA的FIR滤波器的性能研究[J].电子设计工程,2011,19(9):125-128.YU Lin,HUANG Guang-ming.Performance of FIR digital filterbased on FPGA.ElectronicDesign Engineering,2011,19(9):125-128.

[3]王旭东,潘广桢.MATLAB及其在FPGA中的应用[M].北京:国防工业出版社,2006.

[4]罗军辉,罗勇江,白义臣,等.MATLAB 7.0在数字信号处理中的应用[M].北京:机械工业出版社,2005.

[5]程培青.数字信号处理教程 [M].北京:清华大学出版社,2007.

[6]田耕,许文波,张延伟.无线通信FPGA设计[M].北京:电子工业出版社,2007.