高精度时间对准系统研究

张 坡,张 方

(中国电子科技集团公司27所,郑州 450047)

0 引 言

在很多复杂系统中,为了保证各分系统(设备)信息的实时性和准确性,需要有一个时间对准系统来实现系统的时间同步。不论是采用原子钟还是基于全球定位系统(GPS)同步设备,批量装备代价较高,并且不易维护。

为降低设备成本,简化设备的操作和维护,同时又能满足系统的时间同步要求,本文提出了一种基于复杂可编程逻辑器件(CPLD)时间同步技术,并通过使用高精度、高稳定度的恒温晶振来实现系统内的时间同步。

1 目前存在的时间对准系统

目前存在多种时间对准系统,每种又具备不同的特点,而不同的时间对准系统的时间同步精度有较大差异。

1.1 互联网时间对准系统[1]

现在解决分系统(设备)间的时间同步问题最直接、最简单的方法就是通过互联网进行时间比对,它仅仅需要为分系统(设备)提供标准的授时软件,并且提供与时间服务器的接口,分系统(设备)就能通过授时软件访问时间服务器,从而保证时间同步,精度通常可以达到ms级。互联网时间对准系统采用NTP协议,使得分系统(设备)在任何地点既能连接上Internet与世界标准时间服务器进行时间同步校准,也可以连接到局域网上的时间服务器进行时间同步校准。它不需要分系统(设备)针对时间同步问题专门配备时间接收、测试模块,减少软硬件成本。

互联网时间对准系统不受地域限制,非常容易实现,但由于网络数据传输的不确定性及不稳定性,其同步精度不高,限制了其在时间同步精度要求较高场合的应用。

1.2 无线电波授时系统

无线电波授时系统采用无线电波传递时间信息和时间标准,然后由无线电波接收器对接收到的时间信息同本地时钟进行比较,同时自动扣除在传播路径上的延时以及其他各种因素造成的误差,从而实现不同分系统(设备)间时间的同步。无线电波授时同步技术的授时精度较高(长波为ms级,短波为μs级,超短波可达10 ns级),它需要分系统(设备)具有无线电波接收模块。

无线电波授时同步技术至今已经有至少80年的历史,其应用范围广,相对来说无论发送还是接收设备实现简单、价格低廉。此技术最大的优点是可以实时地校准本地时钟,但其应用受到了发射台的地域限制。

1.3 GPS授时系统[2]

GPS是美国海军天文台建立的一套高精度导航卫星全球定位系统,它由21颗工作卫星和3颗在轨备用卫星(总共24颗卫星)组成。它们按一定的规则分布地球的轨道上,人们在任何地点、任何时刻都能看到4颗以上的卫星,从而满足了随时随地进行定位、测量的需求。

GPS是一种单程系统,它只向用户发送信息而不接收,因此用户非常隐蔽并且其数量不受限制,授时精度可达300 ns。但GPS授时系统有一个严重的缺陷,其现在受美国军方控制,无法保障用户应用数据的稳定和安全。

1.4 IRIG-B码[3]

IRIG-B码(以下简称B码)是美国靶场测量组推荐的格式时间码之一,该码在世界各国靶场应用广泛。B码又分直流码IRIG-B(DC)(以下简称DC码)和交流码IRIG-B(AC)(以下简称AC码)。DC码传输距离短,但授时同步误差小;AC码传输远,但授时同步误差相对较大,其同步精度目前能够达到μs级。

2 高精度时间对准系统的实现

CPLD是一种较可编程逻辑器件(PLD)更为复杂的逻辑元件,是当今应用非常广泛的可编程专用集成电路(ASIC)。CPLD具有静态可重复编程和动态系统重构的特性,可以像软件一样通过编程来修改数字电路,极大地提高了系统设计的灵活性和通用性,延时可预测,稳定性好,设计灵活,抗干扰性强,克服了硬件分立器件的不足。

本系统使用Altera公司的MAXII系列芯片EPM1270TI144I5,采用了全新的CPLD体系结构,其速度快,功耗小,容量大,同时又保持了原有的易用性、非易失性和即用性。在主时统模块中CPLD主要实现逻辑控制、计时器、产生秒脉冲等功能,在从时统模块中CPLD主要实现逻辑控制、计时、接收秒脉冲清零、测量延时误差等功能。

3 高精度时间对准系统

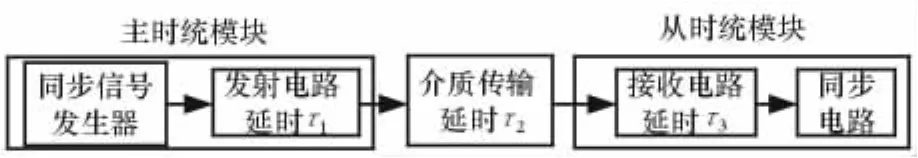

高精度时间对准系统原理示意图如图1所示。

图1 高精度时间对准系统示意图

图1采用主从时统结构,主从时统模块采用相同的高精度频率源和时统电路,该时统系统采用清零对时法和自适应测距校正法来完成分布式多站时间同步。主时统模块和从时统模块中由于采用相同的高精度频率源和时统电路,所以它们的频率偏差和时间漂移带来的累积误差是相同的。时统模块中的计时模块主要分为可精确到秒级的时钟A和精确到纳秒级的时钟B,时间同步主要是指时钟B的同步。

时间同步的误差主要有2个来源:第1种是频率源的频偏和长时间工作造成的累积偏差;第2种是延时误差,当同步通信线路造成的延时误差与同步精度相同或相近时,就需要对其进行校正。

对于第1种误差可通过周期校正来降低误差。主要采用2种手段:

(1)由主时统模块发送秒脉冲信号,对从时统模块秒以下时统清零;

(2)主时统模块产生秒脉冲信号的同时,产生中断读取秒以上时间,发送给从时统模块,从时统模块收到后更新秒以上时统信息。

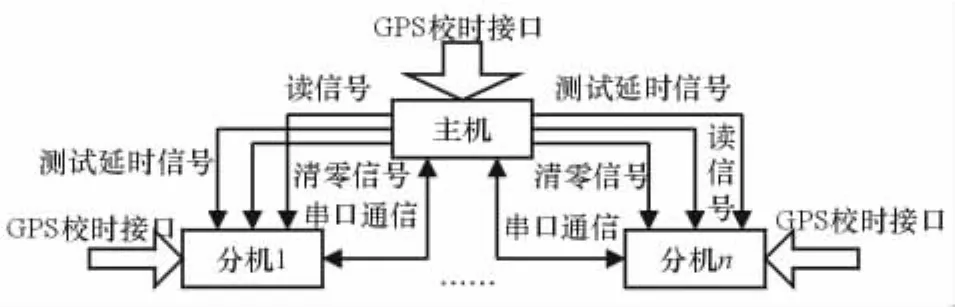

对于第2种误差可以通过在从时统模块设定测距单元来测量校正。延时误差组成框图如图2所示。

延时误差主要有内部传输电路延时(同步信号发出经处理电路到达发射端的延时τ1,同步信号由接收端经处理电路到达同步电路的延时τ3)、外部传输延时(同步信号在介质中传输延时τ2)。电路延时主要与电路复杂程度和器件反应速度有关,一般为10 ns~0.1μs量级。介质传输按光速计算,300 m电缆传输延时即达到1μs,总延时误差τ采用最大估算为τ=τ1+τ2+τ3。一旦系统硬件设计和传输介质固定,则τ值固定。时统模块中设有测距单元,可在设备复位或通过指令对各分站进行延时测量校正。

图2 延时误差组成框图

测距单元的工作原理是:向各分站发送1个测距信号,此测距信号同时作为计时开关开始计时,当各分站接收电路收到测距信号后,利用硬件把测距信号直接转发回去;测距单元收到转发过来的信号后关闭计时开关,停止计时,计时器的计时信息即是主从时统模块两站之间的信号延时τ,所以在从时统模块中的时刻应该是当前时刻加上τ。

高精度时间对准系统实现框图如图3所示。

图3 高精度时间对准系统实现框图

图3中,在主机时统模块和分机时统模块中采用了同一种恒温晶振,计时电路和控制电路全部在CPLD芯片中设计,这样大大降低了硬件成本。设备开机后由主机向分机发送测试延时信号,测得延时时间τn并保存。在主机时统模块中,每秒钟产生清零信号,同时锁存秒以上时刻T。主机时统模块将清零信号和时刻T传输给分机时统模块,分机在清零信号到达时对分机时统模块中秒以下计时器清零,在收到秒以上时刻T后由分机更新分机时统模块秒以上的时刻。主机向各分机下发读取脉冲信号,同时锁存主机时刻T z,由读取信号分别锁存分机时刻T f1和T f2,也可以采用GPS校时接口引入GPS信号,测试出Tz、T f1和T f2,最后比较T z、T f1+τ1、T f2+τ2的值,计算出误差值即时间同步误差。

从上述内容可以看出,在此时间对准系统中,时间对准分为秒以上时间数据(含秒级)的对准和秒以下时间数据的对准。秒以上时间数据对准由主时统模块每秒向从时统模块发送一次主机计数器的秒以上时间数据(含秒级)保证。秒以下时间数据对准由主时统模块每秒钟发送秒脉冲信号对从时统模块秒以下时间计数器清零和保证恒温晶振器件的性能。主时统模块的时刻应该是其时统电路的时刻,而从时统模块中的时刻应该是其时统电路的时刻加上外部传输的延时。此方法比较容易实现且成本比较低廉,只需要在主机和分机上采用相同的恒温晶振和时统电路就可以实现较高的时间同步精度。

4 结束语

目前基于CPLD的时间对准系统已在多个大型的系统中得到应用,在相同的硬件成本条件下,成功提供了时间同步的精度。某大型系统在采用频率20 MHz、频率稳定度5×10-8晶振的条件下,实现了0.5μs的时间同步。应用结果表明:此方法采用了单向时间同步信息的发送机制,仅需要少量的时间信息交换就可以在相同的硬件成本下实现较高时间同步精度。

由于时间数据信息量小、时间同步精度高的特性,所以该系统对时间同步精度要求比较高而硬件成本较低的大型分布式系统有着广泛的应用价值。预期此时间对准系统统可以达到更高的时间同步精度。能够进一步提高时间同步精度的方法主要有:

(1)提高时钟频率源的频率,可有效降低时间同步误差;

(2)提高时钟频率源的频率稳定度,减少时钟晶体累积误差。

[1]张九宾,张丕状,杜坤坤.基于GPS的无线传感器网络时间同步技术[J].传感器与微系统,2009,28(6):31-33.

[2]吴宁,潘小龙,虞皆侠.高精度GPS同步时钟的研究与实现[J].电力系统自动化,2008,32(10):16-18.

[3]GJB2991-97,B时间码接口终端[S].