基于FPGA的数字稳定校正单元的实现

王胜华

(中国电子科技集团公司第二十研究所 陕西 西安 710072)

雷达从体制上可以分为相参雷达和非相参雷达,由于磁控管发射机的起始相位不固定、存在幅度抖动和频率漂移,对接收回波无法做相参积累[1],所以采用磁控管发射机的雷达属于非相参雷达。而现代信号处理中相参积累可以获得更大的增益和更多的功能,例如成像或动目标检测都需要发射和接收信号具有相参性。因此对原有非相参雷达进行相参改进[2-6]成为提高雷达性能的关键。

非相参雷达相参化主要是在信号处理部分来实现,这样既可以节约成本又便于改造实现。而信号处理的核心就是数字稳定校正(DSU)[2-4,6],DSU 的主要作用就是消除发射信号的相位抖动,使接收信号具有相参性。

在数字技术飞速发展的今天,信号处理的硬件实现主要有FPGA[7-8]和DSP等来实现。大规模可编程逻辑器件FPGA在处理速度和集成度等方面发展很快,用户可自定义逻辑功能、可重复编程,同时FPGA还具有成本低、使用灵活方便等优点,在雷达信号处理硬件实现中得到广泛的应用。由于雷达信号处理数据量大、实时性强、动态范围大和数据精度高,结合片内存储能力本文选用ALTERA公司的StratixⅡ系列芯片。

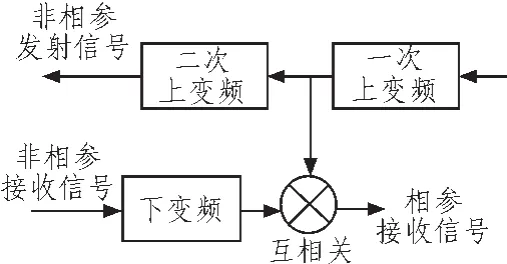

图1 数字稳定校正单元工作框图Fig.1 Structure diagram of the digital stable unit

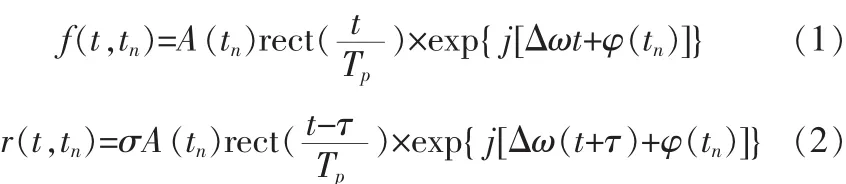

假设这里只考虑脉冲间的幅相不一致,可得发射信号和接收信号的基带形式可以表示为

式中:t为快时间表示,tn表示第n个发射或接收脉冲;A(tn)为第n个发射脉冲随机振幅;φ(tn)为第n个发射脉冲随机相位函数;σ为包含传播衰减和目标散射的系数;rect(t/Tp)为发射脉冲矩形包络函数;Tp为脉冲宽度;Δω为雷达发射机自频调系统静差;τ为接收目标回波的延时。

将式(1)和(2)作相关处理后,可得:

1 数字稳定校正单元的工作原理

可见DSU利用A/D对发射脉冲样本进行取样,然后用该取样值和回波信号进行相关或卷积来实现相位校正,达到消除随机初相的目的。经后续能量归一可以消除幅度不稳定造

数字稳定校正单元(DSU)的主要作用是实现接收信号的相参处理,DSU是利用发射信号对接收的回波信号进行匹配来获得相参性。DSU工作的原理框图如图1所示。成的影响。所以经过DSU处理,可以消除或减小磁控管产生的发射脉冲幅相不稳定性。

2 基于FPGA的DSU实现

由于本雷达信号处理数据量大、实时性强、动态范围大和数据精度高,结合片内乘法器和存储能力本文选一片ALTERA公司的StratixⅡ系列EP2S90 FPGA芯片。Stratix II系列的EP2S90器件具有152个接收机和156个发送机通道、支持1Gbps的高速差分I/O信号、具有LVDS、LVPECL和Hyper Transport标准接口、具有9Mbit的RAM存储器、允许设计者将外挂SRAM和DRAM大容量存储器件。

整个处理流程如下:发射脉冲信号在进入信号处理模块后,首先进行A/D采样,对采样后的数据进行正交分解形成I、Q两路信号,这里发射脉冲内采样为16个数据,发射脉冲数据在发射样本采样门的控制下分I、Q两路存储到发射脉冲存储区,作为DSU相关的权函数使用,记为fI和fQ;接收回波信号在A/D采样后,经过正交分解形成数据流rI和rQ,然后对接收数据进行相关操作,即回波数据以流水方式通过相关器与发射样本数据逐点进行乘加处理。

本论文涉及的内容是从发射脉冲信号和接收数据正交变换后的处理过程,即实现接收数据和发射脉冲样本进行相关的操作。DSU处理的计算公式如下:

这里采取在FPGA内完成相关运算,而对幅度的归一化可采用浮点运算能力较强的DSP器件完成。因为在FPGA内实现除法运算一般采用查表法和,查表法缺点是需要预先存储所有可能值的倒数,然后根据计算出的能量查找相应倒数,取出表中存储的倒数值再做乘法最终实现除法功能。可见再FPGA中实现除法(尤其是系数不固定)比较复杂。而在DSP内部实现除法运算比在FPGA内部实现要更加简单,而且DSP运算基于浮点操作,精度更高。而DSP芯片内的除法可以由乘以相应的倒数得到。能量的倒数通过一次求均方根倒数和一次乘法实现,运算量很小。所以能量归一化运算本文选择在DSP内部完成,实现更简单、精度更高。

图2 基于FPGA的DSU实现框图Fig.2 Realization diagram of the DSU based on FPGA

经过FPGA中的DSU和DSP中的能量归一,接收信号数据已经消除了发射信号的初相抖动和发射幅度不稳定的影响,形成了相参的信号。基于FPGA的DSU实现框图如图2所示,主要包括3个模块,模块1完成发射样本形成滤波器系数和接收数据时序控制;模块2完成对相关后数据的多路选择功能,形成相关后数据流;模块3完成接收数据和发射脉冲样本进行相关操作,由于每个接收数据要进行16次的乘法运算,所以我们同时形成16个乘加模块进行运算。

3 接收机仿真结果

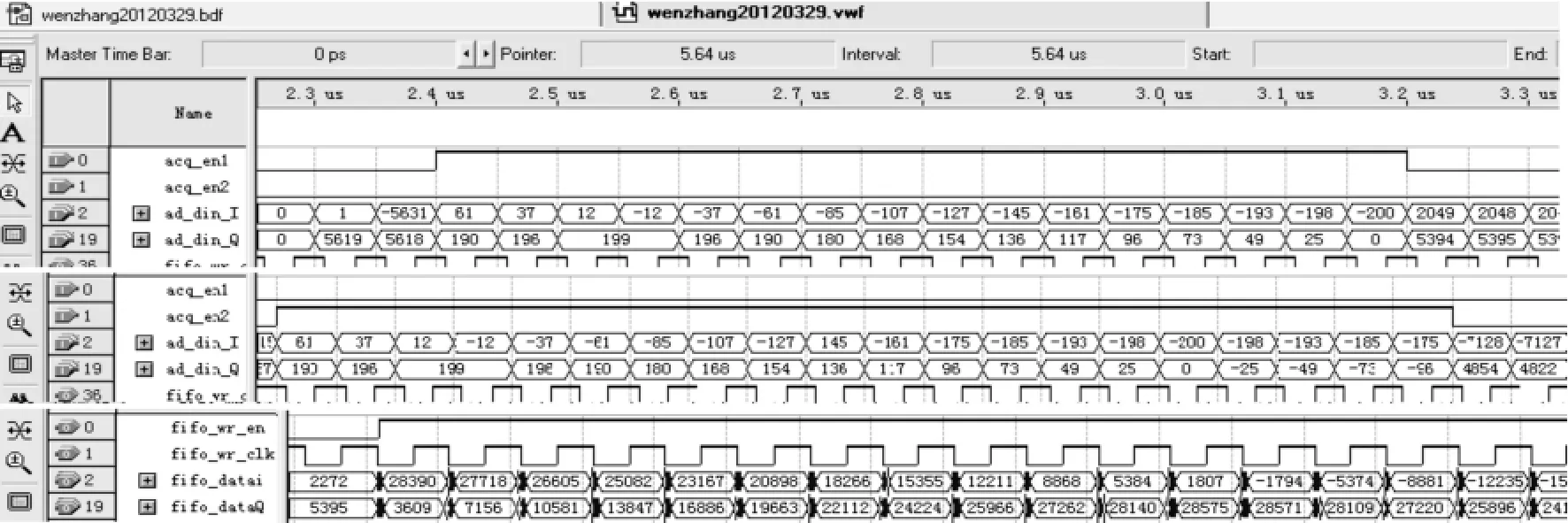

本系统仿真设计是在Quartus II 7.2(32-Bit)环境下进行的,编程代码采用VHDL语言进行编写,硬件芯片平台选择ALTERA公司的StratixⅡ系列EP2S90 FPGA芯片。

系统设计端口定义如下:

ad_clk:数据AD采样时钟

RST:系统复位信号

ad_din[31.0]:数据输入端口,发射数据和接收数据复用

acq_en1:对发射数据采集使能信号

acq_en2:对接收数据采集使能信号

fifo_wr_clk:DSU相参处理后输出数据时钟

fifo_wr_en:DSU相参处理后输出数据使能

fifo_data[31.0]:DSU 相参处理后输出数据端口,高 16 位为 I、低 16位为 Q

仿真中取两组发射和接收数据分别进行DSU处理,仿真结果如图 3、4 所示,从 fifo_datai和 fifo_dataiQ(即 fifo_data[3 操 1..0])可以看出,两组初相不同的数据经过DSU处理后得到了基本一致的结果,即去掉了发射信号的相位抖动。比较图3和图4的fifo_datai和fifo_dataiQ可以发现两者并不完全一样,这时由于FPGA编程为定点数作造成的。

图3 第一组数据的DSU仿真结果图Fig.3 DSU simulation result of the first data

图4 第二组数据的DSU仿真结果图Fig.4 DSU simulation result of the second data

4 结 论

该方法基于Stratix II系列的EP2S90 FPGA芯片实现了数字稳定校正功能,消除了发射信号的相位随机,使接收信号具有相参性。仿真结果表明了本文所述基于FPGA的DSU实现方法有效,另外该算法已经实际用于某非相参雷达改造上,并进行了外场实验,取得了良好的实测效果。

[1]孙青,陶建锋,孙勇.对限制MTI改善因子的因素分析[J].现代雷达,2005,27(5):9-12.SUN Qing,TAO Jian-feng, SUN Yong.Analysis of limitation factors to MTI improvement factor[J].Modern Radar,2005,27(5):9-12.

[2]丁建江,张贤达.幅相联合处理算法的分析和实时实现[J].清华大学学报,2002,42(3):398-402.

DING Jian-jiang,ZHANG Xian-da.Analysis and real-time implementation of A-P combined processing algorithm[J].Tsinghua Univ ersity,2002,42(3):398-402.

[3]俞志强,万山虎,武平,等.雷达幅相联合接收相干处理系统[J].现代雷达,2000,22(5):32-36.

YU Zhi-qiang,WAN Shan-hu,WU Wen,et al. Radar coheren t reception processing system with amplitude-phase combination[J].Modern Radar,2000,18(5):32-36.

[4]齐崇英,张永顺,陈伯孝,等.雷达回波接收相参处理及MTI技术的实现[J].系统工程与电子技术,2004,26(2):1798-1800.

QI Chong-ying,ZHANG Yong-shun,CHEN Bo-xiao,et al.Study and realization on coherent on receive processing of radar echo and the technology ofMTI[J].Systems Engineering and Electronics,2004,26(2):1798-1800.

[5]Gary B J.Comparison of tow major of coherent pulsed radar systems[J].IEEE Trans on AES,1975,11(3):363-370.

[6]Blatch R H.Digital pseudo cohering of radar pulses and results ofmeasurements on amagnetron based radar[A].The record of the IEEE International Conference Radar 97[C]//Edinburgh,UK:IEEElect.and CommuDivision,1997:715-719.

[7]王诚,吴继华,范丽珍,等.Alrera FPGA/CPLD设计(基础篇)[M].北京:人民邮电出版社,2005.

[8]王金明.数字系统设计与Verilog HDL[M].北京:电子工业出版社,2011.