N-LDMOSFET的掺杂分布与热载流子效应

罗 扣, 陈军宁, 高 珊, 张志伟

(安徽大学电子信息工程学院,安徽合肥 230601)

随着栅氧厚度、结深和沟道长度的减小,MOSFET沟道中的载流子在强电场的作用下将获得额外的高能量,这种具有很高能量的载流子称为“热载流子”。载流子通过声子发射越过Si/SiO2界面势垒进入SiO2氧化层,在界面处产生了界面陷阱,在氧化层中产生了氧化层陷阱,从而使得器件的许多电性参数退化,如阈值电压漂移,导通电阻漂移等,这就是热载流子效应[1]。热载流子效应是影响LDMOSFET可靠性的重要因素,LDMOSFET热载流子效应的程度受器件LDD区杂质分布、沟道区杂质分布、LDD区结构、场板结构、氧化工艺、掺杂工艺以及器件工作状态等多种因素影响。近年来,对LDMOSFET的结构与热载流子效应之间关系的研究已经有不少成果,本文研究LDD区结构、场板结构以及工艺条件均相同,而器件LDD区杂质分布、沟道区杂质分布不同时器件热载流子效应所表现出来的不同特征。

1 最坏热载流子应力条件分析

为了尽可能准确地预测器件的退化特性,通常将器件置于最恶劣工作条件中,即器件的最坏热载流子应力条件。因此,研究LDMOSFET热载流子效应要先找到LDMOSFET的最坏热载流子应力条件。由于场效应管中漂移区(N-)的存在,对器件的电势进行了再分布,从而普通MOSFET的最大衬底电流应力(VG=VD/2)将未必是LDMOSFET的最坏热载流子应力条件[2],本文将采用观察器件在不同栅压条件下,衬底电流和栅极热电子电流的变化曲线来寻找LDMOSFET的最坏热载流子应力条件。本文中器件采用常用的LDMOSFET结构,如图1所示,LDMOSFET采用横向双扩散的MOSFET硅工艺技术,即在同一窗口相继进行2次杂质扩散,2次杂质扩散形成的横向结深之差精确地决定了器件沟道长度。其中AB为栅极板,BC为场极板。

图1 N-LDMOS结构纵向剖面示意图

结构和掺杂参数如下:漏源浓度峰值均为7× 1019cm-3,衬底浓度为7×1014cm-3。AB长1.1μm,BC长2.7μm,栅氧厚度为30 nm,场氧厚度为520 nm。器件在常用栅压下,漏压15 V左右达到了饱和状态,击穿电压80 V,此处选取的漏端电压为40 V,保证了器件不发生击穿。5种不同掺杂浓度下衬底电流与栅压的关系,如图2所示。

图2 衬底电流与栅压的关系

图2中,n.ch、n.dr分别表示沟道掺杂浓度和漂移区掺杂浓度。在选取的5种LDMOSFET掺杂参数中最大衬底电流应力条件都并非如普通MOSFET为VG=VD/2,而是远远小于VD/2。并且增加漂移区掺杂浓度,其最大衬底电流应力条件呈现出向后漂移的趋势,这是漂移区的存在所致。因为有了漂移区在沟道与漏极之间充当缓冲区,器件中的电场分布发生变化,在漂移区中产生高场区,从而产生了新的碰撞电离区,使得衬底电流上升[3]。5种不同掺杂浓度下栅极热电子电流与栅压的关系,如图3所示。

图3 栅极电流与栅压的关系

图3表明了在选取的5种LDMOSFET掺杂中,进入到栅极的热电子电流随栅压的变化趋势与图2相似,但最大栅极热电子电流并非发生在最大衬底电流应力处,而是在更高的栅压处。由此可见,随着沟道掺杂浓度的增加,器件更容易达到最大栅电流应力条件(即最坏热载流子应力条件),栅极电流主要由沟道热载流子电流组成[3]。

LDDMOSFET是漏端轻掺杂器件,与LDMOSFET结构相似,其漏端轻掺杂结构与LDMOSFET的漂移区结构都起到有效抑制热载流子效应的作用。由于LDMOSFET和LDDMOSFET都是将漏端高电场转移、分散,伴随高电场的转移,器件的退化特点发生了变化[4-5]。这2种器件的退化特性具有相似性。图4所示为LDDMOSFET器件分别在VD=VG(沟道热载流子应力条件,CHC)、Isubmax(最大衬底电流应力条件,DAHC)应力下实验所得的饱和区漏电流退化比较[6]。

比较图2与图3可见,在较低栅压下2种电流变化趋势相似,说明衬底电流在较低栅压条件下可以作为器件热载流子效应强弱的表征量。在较高栅压下,衬底电流已经趋于饱和,但栅极电流会继续增加。在VDS=40 V时,栅压在20 V附近栅极电流明显高于最大衬底电流应力下的栅电流,图4的实验数据说明,LDMOSFET器件可以把沟道热载流子的多少作为最坏热载流子应力条件衡量标准。

图4 LDDMOSFET饱和区漏电流退化对比

2 区域掺杂与器件退化的关系

出于器件安全工作区域方面的考虑,在进行应力仿真实验时,选取了非常接近最坏热载流子应力条件的设置,以静态偏置为栅压VGS=16 V和漏压VDS=40 V来分析器件的退化情况。在器件的电极上施加此应力,表1中显示的是在沟道掺杂浓度为6×1016cm-3时,不同漂移区掺杂下的漏电流IDS、进入栅极的热电子电流IG、碰撞电离产生的衬底电流ISUB经过4.5×108s后的退化情况。表1表明这3种电流的退化都不是很明显,随着漂移区掺杂浓度的增加,器件的这3种电流的退化速度减弱了,可见适当地提高漂移区掺杂浓度可以有效降低器件的热载流子效应。表1中的负值说明衬底电流值是上升的,这是由于漂移区的存在,器件退化过程中,电势发生再分布,导致了局部碰撞电离增强,这是LDMOSFET独特的退化特性[7]。

表1 器件退化率与漂移区掺杂浓度的关系 %

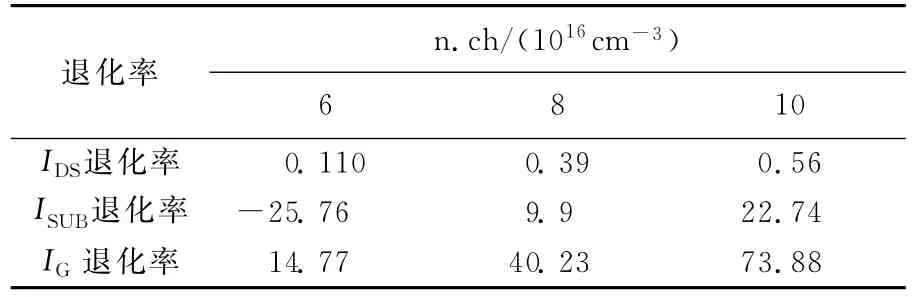

表2中显示的是在漂移区掺杂浓度为6× 1016cm-3时,不同沟道区掺杂下的漏电流IDS、进入栅极的热电子电流IG、碰撞电离产生的衬底电流ISUB经过4.5×108s后的退化情况,表2说明随着沟道区掺杂浓度的增加,器件的退化变得很剧烈,直接影响到了器件的使用寿命。

表2 器件退化率与沟道区掺杂浓度的关系 %

通过对表1和表2的数据进行分析,可知沟道的掺杂对器件的热载流子效应更具有影响力,这是在器件漂移区结构、场板结构相同的情况下所表现出来的特征。

比较表1和表2可以发现,随着沟道区掺杂浓度的减少或者漂移区浓度的增加,漏电流、栅极电流和衬底电流的退化速度都会明显减弱。可见由于漂移区的存在,器件的退化特性具有了新的特点,即漂移区的存在使得LDMOSFET的热载流子效应得到有效的抑制,下面将对这一现象进行详细的解释。

3 区域掺杂与热载流子作用机理

器件的热载流子效应由MOSFET的栅极电流直接反映,本文将根据栅极电流的来源,详细分析LDMOSFET中热电子的产生以及对器件的作用机理。

3.1 区域掺杂与电场分布

图5所示为漂移区掺杂浓度作为递增变量时LDMOSFET中的电场曲线图。

图5 LDMOSFET电场强度分布

由图5可见,随着漂移区掺杂浓度的升高,器件的高电场由近漏端区域向场极板以下区域以及近沟道区域转移,在高电场下碰撞电离加剧,文献[8]中提出衬底电流与漏极电流、漏压和电场的关系如下:

其中,Ib为衬底电流;C1为系数,ID为漏极电流;Ei为热电子通过碰撞电离产生电子 -空穴对所必须具有的最小能量;E为高场区的电场强度。λ为热电子得到能量kBTe所经过的平均自由程,其中kB为玻尔兹曼常数,Te为热载流子温度。增加栅压和漏压虽然可以增加漏极电流ID,但同时也增强了器件的热载流子效应。从(1)式可以看出,衬底电流与电场强度是增函数的关系。

鉴于LDMOSFET的特殊结构,发生碰撞电离的区域与器件的电场分布以及电流密度有着紧密的联系。由图5可以看出,一定的应力条件下,随着漂移区中掺杂浓度的增加,电子碰撞几率上升,在漂移区内发生强烈的碰撞电离,从而衬底电流又有了新的来源。但是由于器件独特的漂移区结构,在漂移区内产生的热载流子并不能直接影响栅氧化层,由于场氧层的势垒比栅氧层高出许多(本文中LDMOSFET所采用的场氧厚度是栅氧厚度的17倍),对场氧的损伤也是非常小,有效地抑制了器件中的热载流子效应[9-10]。

3.2 LDMOSFET中的碰撞电离分布

通过仿真,得到了碰撞电离分布图。图6 a、图6 b分别表示的是漂移区掺杂浓度、沟道掺杂浓度作为递增变量时LDMOSFET中的碰撞电离分布图。图中显示出发生碰撞电离的区域,可以比较直观地发现热电子电流的来源。

图6 碰撞电离分布

从图6可以看出,碰撞电离主要发生在沟道与漂移区相遇形成的PN结附近和近漏极区域,其中近沟道的场极板下方区域碰撞电离程度较强烈。比较图6a、图6b可以发现,随着沟道掺杂浓度降低,漂移区掺杂浓度升高,器件的碰撞电离主要分布区有向漂移区转移的趋势,这与图5中的电场强度分布相对应。

3.3 区域掺杂与器件退化

通过以上仿真结果及理论分析,可知增加沟道掺杂浓度,加剧了热载流子效应,直接提高了热电子进入栅氧的数量;增加漂移区浓度,对热载流子效应略有加强,但是漂移区内产生的热电子进入的是场氧区[11],从而被栅极收集到的热电子更是极少,而且场氧厚度达到520 nm(栅氧厚度为30 nm),所以场氧的势垒高度远远高于栅氧,热电子进入场氧的概率是非常小。这样就定性地解释了表1和表2中漏电流、栅电流、衬底电流的退化机制。

4 结 论

通过以上的仿真结果以及理论分析,器件的区域掺杂与器件热载流子效应的关系为:

(1)增加器件掺杂浓度,提升器件驱动能力的同时,缩减了器件的安全工作区(击穿电压降低),也使得热电子效应加剧,降低了器件的稳定性和可靠性。相对于增加沟道掺杂,增加漂移区掺杂可使这一矛盾得到缓和。

(2)增加沟道区的掺杂浓度和漂移区的掺杂浓度都会增强热电子效应,其中,增加沟道区的掺杂浓度会使得器件的电学特性退化更加明显,而增加漂移区的掺杂浓度结果正好相反。通过仿真数据分析可知,沟道区的掺杂浓度对器件的热载流子效应比漂移区掺杂具有更大的影响。因此,在保证器件驱动能力的情况下,在确定各个区域的掺杂时,要本着沟道掺杂不调或微调的原则,来规划漂移区的结构和掺杂。

[1] 刘恩科,朱秉升,罗晋生,等.半导体物理[M].第4版.北京:国防工业出版社,2009:105.

[2] Mahapatra S,Parikh C D,Rao V R,et al.A comprehensive study of hot-carrier induced interface and oxide trap distribution in MOSFET's using a novel charge pumping technique[J].IEEE Transactions on Electron Devices,2000,47(1):171-177.

[3] Anil K G,Mahapatra S,Eisele I.A detailed experimental investigation of impact ionization in n-channel metal-oxidesemiconductor field-effect-transistors at very low drain voltages[J].Solid State Electronics,2003,47(6):995-1001.

[4] Corso D,Aurite S,Sciacca E,et al.Measurement of the hot carrier damage profile in LDMOS devices stressed at high drain voltage[J].Microelectronics Reliability,2007,47(4/5):806-809.

[5] Nigam T,Shibib A,Xu S,et al.Nature and location of interface traps in RF LDMOS due to hot carriers[J].Microelectron Eng,2004,72:71-75.

[6] 于春丽.超深亚微米LDDMOSFET器件模型及热载流子可靠性研究[D].西安:西安电子科技大学,2004.

[7] Ashot M M,Ma T P.Lateral profiling of interface traps and oxide charge in MOSFET devices:charge pumping versus DCIV[J].IEEE Transactions on Electron Devices,2001,48:2303.

[8] 曾树荣.半导体器件物理基础[M].第2版.北京:北京大学出版社,2007:205-207.

[9] Ludikhuize A W.A review of RESURF technology[C]//Proc ISPSD,2000:11-18.

[10] 谌婧娇,陈军宁,高 珊.对称薄膜双栅MOSFET温度特性的研究[J].合肥工业大学学报:自然科学版,2012,35(6):776-779.

[11] Yi Kun,Zhang Bo,Luo Xiaorong,et al.Techniques for improving breakdown voltage using deep trench[J].Microelectronics,2004,34(2):203-205.