一种带有增益提高技术的高速CMOS运算放大器设计

宋奇伟,陆安江,张正平

(贵州大学 贵州省微纳电子与软件技术重点实验室,贵州 贵阳 550025)

随着当今集成电路技术遵从摩尔定律的快速发展,在深亚微米级甚至纳米级工艺下电源电压及MOS管特征尺寸不断降低,器件的诸多性能已达到瓶颈。因此,各种高性能模拟或混合集成电路如∑-Δ调制器、开关电容滤波器和流水线A/D转换器中的高性能运算放大器[1]的研究已成为当今的热点。速度和精度是模拟集成电路中均很重要的性能指标,前者需要器件有大的带宽,短沟道以及单极点系统设计;后者则需要在小偏置电流、长沟道、多级放大器设计的同时实现高增益[2]。因此两者的实现必然会产生设计上的冲突,而这种矛盾也激励着电路设计师去根据应用的需要的同时折中考虑并且创新电路结构来满足系统的要求。

1 电路的选择

1.1 主运放的选择

高速运算放大器作为Pipelined ADC中的一个重要模块,它的特性直接决定了电路系统的整体性能,对于作为ADC前置放大器的设计,运放要有大的单位增益带宽和高的开环增益;同时,要兼顾功耗以及输出摆幅、共模抑制比(CMRR)等参数的考虑。共源共栅结构能够对速度和精度有很好的折中,已广泛应用于运算放大器、基准源和滤波器等模拟器件中。它总的划分有两种结构:套筒式共源共栅结构(telescopic-cascode)和折叠式共源共栅结构(fold-cascode)。

套筒式共源共栅运放只有两条支路组成,功耗较小,且由于次主节点附近的寄生电容较小,所以带宽更大,速度更快。但该电路由于是由多级管层叠而成,共模输入范围和输出摆幅过小,如果不接二级电路很难在低压下正常工作;折叠式共源共栅运放的次主极点周围的寄生电容较大,频率特性相对于套筒式共源共栅结构较差但差距不大。由于结构呈折叠状而省去了层叠的多层管,其共模输入范围及输出摆幅均远大于套筒式共源共栅的对应值,但其结构为4条回路,故其功耗略大。

根据实际需要从应用角度考虑,作为ADC前置放大器,所设计的运放要求要在能保证精度基础上有尽可能快的速度。上述分析表明,两种基本的共源共栅结构所构成的运放均有较高的速度,但是相对而言折叠式共源共栅比套筒式共源共栅有更大的共模输入范围和输出摆幅,且其输入输出可以短接而且输入共模电平更容易选取,因此折叠是共源共栅运放更符合要求[3]。

1.2 增益提高(gain boosting)技术

在深亚微米及纳米级工艺水平下MOS管最小沟道长度越来越小,器件的带宽越来越大从而速度越来越快,但增益却越来越低,单级共源共栅运放的增益也降至约40 dB左右,这样的结构很难满足对精度的基本要求。故本设计增加了增益提高级。其基本原理如图1所示:将 M1看成一个反馈电阻,与M2构成一个从电流到电压的负反馈环路,通过减小由输出到输入管漏极的反馈,使得M1的漏电压随输出电压的变化很小,流过M1的电流更加稳定,因而产生了更高的输出阻抗。设辅助运放Aadd放大倍数为A,则输出阻抗为:

其中,ro1、ro2分别是 M1、M2管得小信号等效电阻,gm2是M2的跨导[4]。可见利用增益增强技术可以是输出电阻提高A倍,从而也使得电路的直流增益增大了A倍:

图1 带增益提高放大器的电路Fig.1 Circuit of opamp with gain booting

但增益增强技术在提高增益的同时也带来一个明显的缺点:在图1电路中得输出端和M1的漏端分别形成运放的主极点和次主极点。因此经常会在辅助运放的单位增益带宽附近产生零极点对,尽管不会影响运放的频率响应,但它却使运放的建立特性变差。通常的处理方法是提高零极点对的发生频率,即提高辅助运放的单位增益带宽[4],但若将辅助运放的单位增益带宽频率提高到主运放的第二极点附近时,整个运放将不稳定。因此,通过分析得出使辅助运放Aadd的单位增益带宽要介于运放闭环-3 dB带宽和主运放的非主极点值之间[5],并在辅助运放输出端和地之间增加补偿电容C0和C1进行微调即可,其大小约为负载电容的1/2~1/3。

图2是各级运放的增益带宽关系示意图。Aorig为未加增益辅助运放的增益曲线,Aadd为辅助运放增益曲线,Atot为添加辅助运放后主运放的增益曲线。若要使系统稳定,则需:

图2 各级运放增益示意图Fig.2 Gain bode plots of all level stage

1.3 全差分折叠式共源共栅放大器

文中设计的主运放如图3所示,采用带增益增强辅助电路的全差分折叠式共源共栅运算放大器。主运放采用以PMOS管为输入管的全差分折叠式共源共栅结构。若输入管采用NMOS对管,由于电子比空穴迁移率大,虽然能得到更大的增益,但同时其折叠点会产生更大的寄生电容,直接影响了运算放大器的速度。由于本设计对速度的要求是第一位的,所以采用PMOS管作为输入管来提高主运放的次极点频率并且能降低运放的噪声。同时,临近输出端的MOS管要经过合理的调试,既要满足支路电流的要求,又不能引入过大的寄生电容而影响到系统的频率特性。

增益提高辅助运放也采用了两个全差分折叠式共源共栅结构,既可以减少电路的面积和功耗,又减少电路内部节点的电容。在辅助运放An的输出端添加两个补偿电容C0和C1,用以消除在主运放单位增益带宽附近产生的零极点对。其中,由于Ap必须工作在较高的共模电压下,故选择NMOS管作为运放的差分输入管,相反,An是以PMOS作为差分输入管。以Ap为例,如图4所示,NMOS输入管接M9、M10的漏极,经过放大后输出到M7和M8的栅极,Ap只需提供M7,M8饱和工作所需的共模电平,因而不需要大的摆幅。同时由于M7和M8的栅极电容构成了Ap的容性负载,所以2个管子不能太大。辅助运放如图3所示。An的拓扑结构和Ap类似,但采用PMOS管作为输入对管[6]。

由于辅助运放主要为主运放提供增益上的改善,不需要太快的速度和建立时间,因此它的尾电流一般为主运放电流的1/10~1/4,大大降低了整个电路的功耗和面积。且由于增加了增益提高辅助运放,即使采用最小尺寸也很容易实现100 dB以上的增益,因此主运放中各MOS管均采用最小尺寸,这也可以有效地提升非主极点的位置,而辅助运放则不需要使用最小尺寸。

1.4 共模反馈

因为采用全差分结构,放大器的输出共模特性对器件的不匹配非常敏感,由于放大器的输出阻抗较高,很小的电流偏差也会使作为电流源的MOS管进入线性区而不能正常工作,且此情况不能通过差动反馈进行遏制,所以必须在输出端增加共模反馈电路(CMFB)来改善输出特性。

图3 主运放电路图Fig.3 Circuit of main circuit

图4 辅助运放Ap电路图Fig.4 Circuit of auxiliary opamp Ap

由于本设计的运放要应用于Pipelined ADC中,故主运放采用开关电容(SC)共模反馈,如图5所示。开关电容共模反馈电路工作在两相不交叠时钟下,当phi2为高电平时,C2充电到Vref—Vbias。而当phi1为高电平时,C1与 C2相连,C2进行放电,从而决定C1上的电压值。共模反馈电路产生的调节信号CMFB则由C1通过反馈回路产生。使用开关电容共模反馈电路既可以节省功耗,又使取样电路不会限制主运放的输出摆幅。

图5 开关电容共模反馈电路图Fig.5 Circuit of switched-capacitor(SC) CMFB

但是,开关电容共模反馈电路并不适合两个增益提高辅助运放。因为两个辅运放负载电容较小,若采用开关电容共模反馈,电容会更小,导致电路精度下降。且辅运放不需要大的输出摆幅,故文中对辅运放采用传统的连续时间共模反馈。

1.5 三支路基准电流源

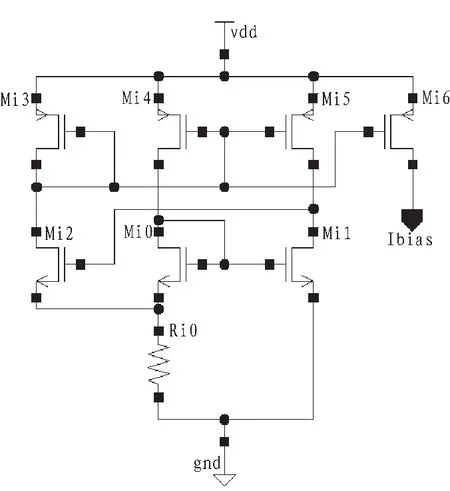

为提高CMOS集成电路中电流基准的精度和稳定性,一个具有高PSRR的基准电流源是必需的。由于传统的电流基准以及共源共栅电流基准的节点电压正反馈限制了电流基准的性能,三支路基准电流源如图6所示。

图6 三支路电流基准源电路图Fig.6 Circuit of triple-branch current reference

此结构由于节点电压成负反馈,拥有更高的PSRR。该基准电流源的输出电流为:

可以看出:其输出电流与系统的电源电压无关而只与调节电阻Rs有关,通过调节合适的Rs的阻值,即可得到精确的基准电流。故本文采用三支路电路基准源的设计,而偏置电路采用低压宽摆幅共源共栅结构。

2 仿真结果

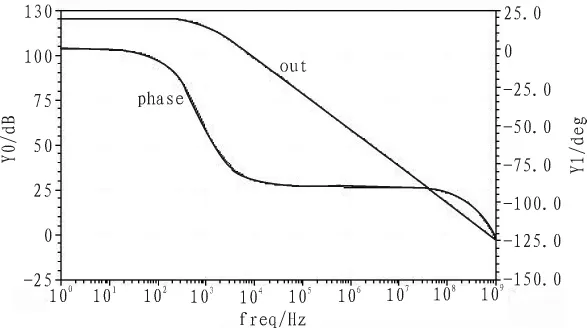

采用SMIC 0.25μm CMOS工艺模型,在Cadence环境下对电路进行 仿真, 单电源供电,模拟结果显示:运放的直流增益为124 dB,单位增益带宽为720 MHz,相位裕度64°CMRR高达 153 dB。

图7 运放的幅频相频曲线Fig.7 Amplitude-frequency and phase-frequency curves of the opamp

图8 运放CMRR曲线Fig.8 CMRR curves of the opamp

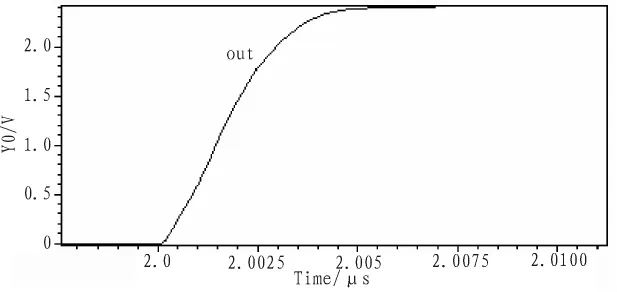

运放的瞬态建立特性如图9所示,于输入端2μs处加2.5 V的阶跃响应,由输出波形测得转换速率885 V/μs;达到0.1%的稳定精度的建立时间为4 ns。

图9 运放的输出建立时间曲线Fig.9 Settling time curves of the opamp

图10 是运算放大器的版图,通过了DRC与LVS验证,结果显示性能良好。

3 结 论

图10 运放的版图Fig.10 Layout of the opamp

文中提出了一种可用于高速Pipelined ADC中的前置放大器,结合开关电容共模反馈与三支路共源共栅基准电流源等技术,详细分析了增益提高技术的设计原理、弊端及改进方法,实现了一个全差分带增益提升级的折叠式CMOS运算放大器。仿真结果表明:该运放的直流增益达到124 dB,单位增益带宽720 MHz,达到0.1%精度建立时间为4 ns,转换速率高达885 V/μs。性能良好,满足系统设计要求。

[1]SU Li,QIU Yu-lin.Design of a fully differential gain boosted fold-cascode op amp with setting performance optimization[J], IEEE JSSC,2005,3(8):441-444

[2]Butt K,Geeien G.A fast-settling CMOS op-amp for SC circuit with 90-dB DCgain[J].IEEE Jof Solid-State Circuits,1990,25(6):1379-1384.

[3]Razavi B.Design of Analog CMOSIntegrated Circuits[M].Mc.Graw-Hill, Inc.,2001.

[4]蔡坤明,何杞鑫,陶吉利.一种增益增强型套筒式运算放大器的设计[J].电子技术应用,2010,36(5):66-69.CAI Kun-ming, HE Qi-xin, TAO Ji-li.Design of a gain boosted telescopic operational amplifier[J].Application of Electronic Technique,2010,36(5):66-69.

[5]YAO Zhi-jian,MA Cheng-yan,YE Tian-chun,et al.Design and analysis of a Gain-Enhanced, fully differential telescopic operational transconductance amplifier elec[J].Journal of Semiconductors,2008,29(2):269-274.

[6]刘瑞强,景新幸,张祥祯.一种高增益低功耗CMOS运算跨导放大器的设计[J].电子设计应用,2007(2):39-42.LIU Rui-qiang, JING Xin-xing, ZHANG Xiang-zhen.Design of high DC-Gain and low power CMOS operational transconductanceamplifier[J].Electronic Design&Application,2007(2):57-59.