锁相环设计中的功率分配与分频器配置方法

杨继松,韩 喆,邢 钧,宁永海

(1.河南科技大学 电子信息工程学院,河南 洛阳471003;2.国家广播电视产品质量监督检验中心,北京100015)

锁相环频率合成器[1]是基于一个高精度和高稳定度的标准参考频率源,产生一系列参考频率倍数的输出频率,且具有相同的精度和稳定度。锁相环频率合成器特别适用于具有固定频率间隔的广播、电视和多信道无线通信中,最典型的应用是在超外差式接收机中产生混频器所需的本地振荡信号[2]。众所周知,基于锁相环的频率合成器由作为参考频率源的晶体振荡器、相频检测器、压控振荡器、环路滤波器和分频器组成,是一个数字控制型的模拟电路结构[3]。在电路设计中必然会涉及到模拟电路的阻抗匹配、功率传输与分配、滤波等问题,以及数字分频器的配置问题。本文针对该应用目的,对工程设计中遇到的关键技术问题进行研究。

晶体振荡器为锁相环提供参考频率,较强的参考频率信号强度会带来较好的相位噪声性能。因此,晶体振荡器的输出功率应尽最大可能地提供给锁相环的参考频率输入端。然而,锁相环参考频率输入端的纯容性输入阻抗对最大功率传输,以及满足晶体振荡器正常工作条件所需的端接电路的设计带来了极大的挑战。传统的馈电电路结构存在不足,难以兼顾二者的需要,需要进行改进,合理地设计馈电电路[4]。压控振荡器的输出阻抗是50Ω,正常工作条件下,应该端接50Ω的负载,但由于压控振荡器的输出除了作为本地振荡频率提供给混频器外,还要分出一路反馈信号提供给锁相环的射频输入端。混频器的输入阻抗通常也是50Ω,而锁相环的射频输入端的输入阻抗是复阻抗,远远偏离50Ω,且随频率变化,这给压控振荡器的输出端口阻抗匹配和本地振荡器的最大功率输出非常不利,需要采取阻抗匹配措施。传统的阻抗匹配电路功率损耗太大,也需要进行改进。另外,锁相环射频反馈支路上的N分频器是一个双模预分频器结构,包含A和B两个分频器(N=A+P×B,其中P是预分频值,可选取8,16,32,64等固定值),用于降低VCO的输出频率,并与晶体振荡器经参考分频器(R)分频后的参考频率信号进行相频比较。对于给定的参考频率源和所要产生的一系列本地振荡频率值,如何合理地配置R,A和B分频器的值,也是工程设计中需要解决的问题,本文将提供一个通用的算法。尽管环路滤波器也是锁相环频率合成器设计中的一项重要内容,但由于关于环路滤波器的设计[5]已有类似于ADIsimuPLL的仿真设计软件可以方便地进行。

1 理论分析

1.1 晶体振荡器对锁相环参考频率输入端的馈电问题

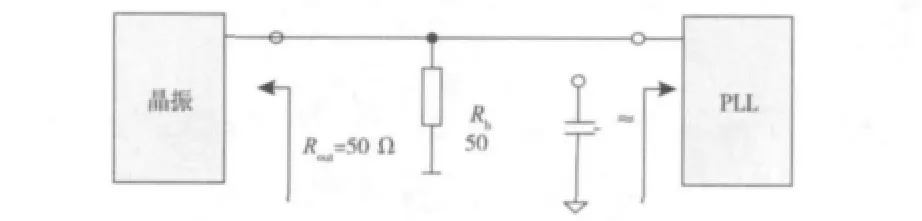

晶体振荡器是锁相环频率合成器的重要组成部分,它的作用是为PLL参考频率输入端提供一个稳定的参考频率。除了参考频率的相位噪声应远低于系统设计指标要求外,参考频率的功率也应该达到一定的电平,尽管PLL对参考频率功率电平的可接受范围很宽,但较强的参考频率信号强度会带来较好的相位噪声性能,如+5 dBm(相对于50Ω系统)的功率电平将会产生优越的性能。对于晶体振荡器来说,提供+5 dBm的功率电平并非难事,但问题的关键是PLL参考频率输入端的等效输入阻抗呈容性,等效于一个容值为5 pF的电容[4],晶体振荡器相当于对一个纯电容负载馈电。尽管晶体振荡器并不严格要求负载是50Ω,但端接一个纯电容负载严重地偏离了50Ω的最佳工作状态,导致输出频谱中出现了较强的二次谐波和三次谐波成分。通常的做法是在PLL参考频率输入端并联一个50Ω的电阻Rb,以改善晶体振荡器的工作条件,如图1所示。在晶振和PLL的参考频率输入端之间并联一个电阻Rb,但此时的负载相当于电阻Rb和PLL参考频率输入端等效电容C并联,对于容值为5 pF的电容和10 MHz的晶振频率,电容的容抗要远大于50Ω的电阻,从而导致晶振输出电流的绝大部分被电阻Rb分流,能量消耗在电阻Rb上,PLL分得的信号能量极少,造成参考频率信号能量的极大浪费,因此需要对这种馈电方式进行改进。

图1 晶振和PLL参考频率输入端的连接电路示意图

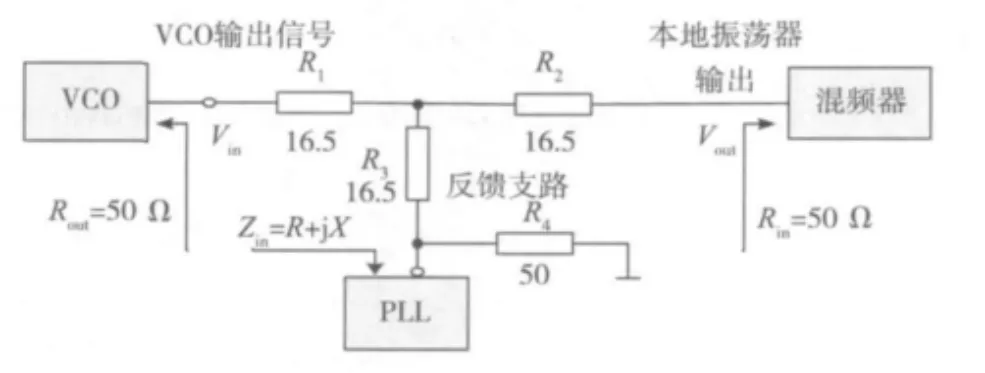

本文提出的改进方法如图2所示,在晶振和PLL的参考频率输入端之间串联一个电阻Rc,这样电阻Rc不但不会分流,而且还和PLL的等效输入电容一起构成一个RC低通滤波器,能够滤除晶振因负载失配所产生的谐波成分。电阻Rc和电容C是分压关系,调整电阻Rc的值可改变二者的分压比例,同时也改变了RC低通滤波器的截止频率。如果把截止频率点设置到晶振的基波频率上,则电容分得的电压是晶振输出电压的0.707倍,相应地分得的功率是晶振输出功率衰减3 dB后的值,即功率的1/2。实验测试结果也证实了,采用这种串联方式,极大地提高了PLL输入参考频率信号的能量,很大程度地减少了能量损失,于此同时还能抑制或滤除二次谐波、三次谐波和其他高次谐波成分,为改善PLL的相位噪声性能创造了有利条件。

图2 改进的晶振和PLL参考频率输入端连接电路示意图

1.2 VCO输出功率分配与阻抗匹配电路改进型设计

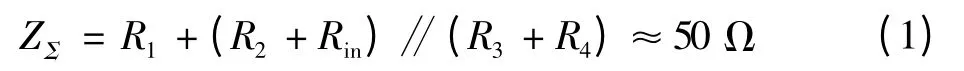

当锁相环频率合成器用于混频器的本振信号源时,总希望本振输出的信号有足够的强度。而本振输出功率的大小并不完全由VCO的输出功率决定,因为VCO的输出除了供给混频器外,还要分出一路反馈给PLL的射频信号输入端,这样VCO的输出端口与混频器和PLL射频信号的输入端三者之间构成了一个T型电路结构。由于VCO输出阻抗和混频器的输入阻抗均为50Ω,在正常工作条件下,均要求端口外接50Ω的负载,为了满足端口外接匹配负载的要求,通常采用如图3所示的T型电阻匹配网络[6]。

图3传统的T型电阻匹配网络

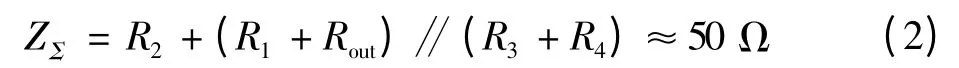

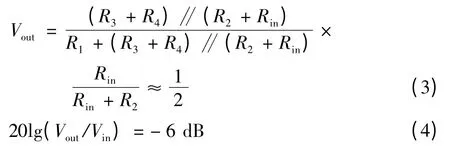

图3 中电阻R1,R2,R3的阻值均为16.5Ω,并联于PLL射频信号反馈输入端口的电阻R4的阻值为50Ω,其目的是与PLL射频信号反馈输入端口的输入阻抗Zin并联后实现与外部50Ω系统的匹配(其实这种假设很难成立)。从VCO端口向匹配网络看进去的总的输入阻抗ZΣ是电阻R3和R4串联后与电阻R2和混频器输入阻抗Rin(等于50Ω)串联后的阻抗并联,然后再与电阻R1串联,公式为

同理,从混频器输入端口向匹配网络看进去的总的输入阻抗ZΣ是电阻R3和R4串联后与电阻R1和VCO输出阻抗Rout(等于50Ω)串联后的阻抗并联,然后再与电阻R2串联。它们的共同特征是总的输入阻抗,公式为

可见,该T型电阻匹配网路从任意端口看进去的输入阻抗均等于50Ω,满足VCO和混频器外接负载的要求。但该匹配网络的插入损耗为

因此采用这种电路连接形式,从VCO输出的信号能量输入到混频器时衰减了6 dB。以Mini-circuits生产的JTOS-400型的VCO为例,其输出功率高达9 dBm,但经T型电阻匹配网络衰减后,混频器得到的能量不足3 dBm,不能满足混频器对本振的输出功率要求,需要增加额外的驱动放大电路;而另一方面,PLL所需的射频输入信号能量很小,一般-20 dBm就足够了,但反馈回来的和混频器得到的一样,也是3 dBm,造成了能量的极大浪费,所以需要对这种电路结构进行改进。在满足PLL正常工作所需要的射频反馈信号能量,以及VCO和混频器端口外接负载的条件下,为了最大限度地把VCO输出的能量分配给混频器,减小因过多的反馈给PLL所造成的能量损失,摒弃了传统的T型电阻匹配网络形式,提出了如图4所示的改进的T型匹配网络结构。

图4 改进后的T型匹配网络

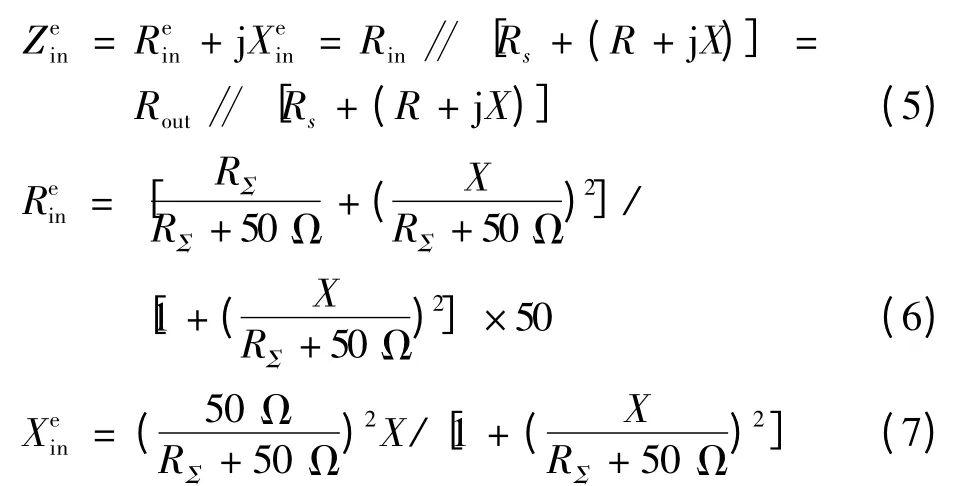

直接在反馈支路上串接一个大电阻Rs,使其满足Rs+R≫50Ω条件,此时无论是从VCO输出端还是从混频器输入端向T型网络看进去的输入阻抗均为该大电阻Rs与PLL系统的输出阻抗(R+jX)串联后再和50Ω的系统阻抗并联的结果,即

式中:RΣ=Rs+R,Rin=Rout=50Ω。当RΣ≫50Ω,RΣ≫X时,(X/(RΣ+50Ω))2≈0,RΣ/(RΣ+50Ω)≈1,则≈50Ω,RΣ≫X。

例如,若取Rs=500Ω,当R=15Ω,X=80Ω满足RΣ=Rs+R=515Ω≫50Ω的条件,且RΣ≫X=80Ω时,有=j=(45.66+j 0.614)Ω≈50Ω。所以,图4所示电路均满足VCO和混频器端口对外接负载的要求,且电路比较简单。最重要的是,VCO的输出电压和混频器的输入电压的比值为1,没有分压衰减,且由于反馈支路串联了一个大电阻Rs,电流分流也很小,VCO输出能量的损失也就很小。实测结果可以使VCO提供给混频器信号能量高达8 dBm,也使从VCO反馈给PLL的信号强度降低到-20 dBm水平,减少了不必要的能量损失,提高了锁相环频率合成器的输出功率,不需要增加额外的驱动放大电路就能够满足混频器对PLL频率合成器作为本振的输出功率要求。

1.3 锁相环R与N分频器的配置方法

PLL频率合成器的输出频率fout与参考频率fi和PLL的分频器R和N之间的关系fout=fi×N/R=fi(A+P×B)/R可知,对于给定的参考频率fi,fout取决于对R和N的配置。其中参考频率信号fi经过R分频后输入鉴相器,此频率称为相频检测频率,即fPFD=fi/R。对于PLL系统,要求相频检测频率的取值应与接收信号的信道间隔频率之间成整数倍关系,即信号频率间隔应能被相频检测频率整除(频相检测频率最大可等于信道间隔频率)。满足此条件时锁相环才能锁定,输出稳定的合成信号。因此R分频器值的确定取决于PLL系统对相频检测频率的要求。一旦R分频器的值确定,那么N分频器的值也就确定了。但由于N分频器是一个双模预分频器结构,它由A和B两部分组成(N=A+P×B,其中P是预分频值,可选取8,16,32,64等固定值),给分频器的配置带来了一定的困难。这里将结合实际应用例子分别给出多频点和单频点输出的PLL频率合成器中R与N分频器的配置方法。

1.3.1 多频点PLL频率合成器中R与N分频器配置方法

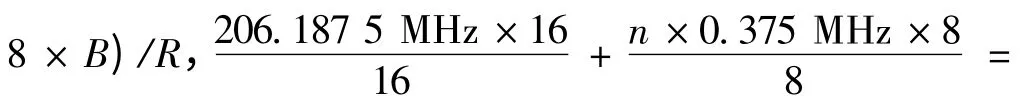

假设某一型号的GMSK接收机接收的信号频率范围为135.187 5~173.5 MHz,信道间隔为0.375 MHz,信道的中心频率为:fn=(135.187 5+n×0.375)MHz,其中(n=0,1,2,…)。若要求各信道信号经混频器混频后,均转换成中心频率为71 MHz的固定频率信号,则对应地要求作为本地振荡器的PLL输出一系列的频率信号:fout=fn+71 MHz=(206.187 5+n×0.375)MHz,其中(n=0,1,2,…)。由于fout=(206.187 5+n×0.375)MHz=fi(A+式中fi/R是相频检测频率,它与信道间隔频率之间应满足整数倍的关系,这是综合设计PLL环路滤波器时所要求的。即fPFD=fi/R=0.375 MHz/Z,这里Z和R必须取正整数。当fi=10 MHz时,若取Z=1,即相频检测频率等于信道间隔,此时计算所得R不是整数,不满足要求;依次寻找,当Z=6时,对应的参考分频R=160,相频检测频率为:fPFD=fi/R=0.062 5 MHz,因为6×fPFD=0.375 MHz,相当于每6个相频检测频率间隔取1个数据,仍然可以满足锁相环的稳定条件。所以,R=160符合锁相环的设计要求。当R=160时,得16fi/R=1 MHz,将此项值代入(3 299+n×3×2)MHz中,则B=(3 299-A)/8+n×3/4。

1)当n=4m(m=0,1,2,…m)时,B=(3 299-A)/8+3m。若取A=3,则B=412+3m(其中,m=n/4)。

2)当n=4m+1(m=0,1,2,…)时,B=(3 299-A+6)/8+3m。若取A=3+6=9,则B=412+3m(其中,m=(n-1)/4)。

3)当n=4m+2(m=0,1,2…)时,B=(3 299-A+12)/8+3m。若取A=3+12=15,则B=412+3m(其中,m=(n-2)/4)。

4)当n=4m+3(m=0,1,2,…m)时,B=(3 299-A+18)/8+3m若取A=3+18=21,则B=412+3m(其中,m=(n-3)/4)。

A,B,m各数据随n的变换规律总结如下:

n=0,1,2,3,4,5,6,7,8,9,10,11,…

m=[n/4]=0,0,0,0,1,1,1,1,2,2,2,2,…

B=412+3m=402+3×0,412+3×1,412+3×2,…

k=n-4m=0,1,2,3,0,1,2,3,0,1,2,3,…

A=3+6k=3,9,15,21,3,9,15,21,3,9,15,21,…

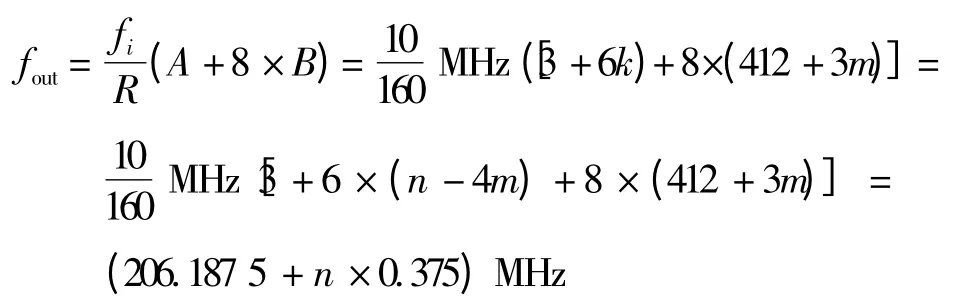

综上所述,PLL分频器A,B,R可取的一系列数值为:R=160,A=3+6k(k=0,1,2,3),B=412+3m(m=0,1,2,…)。可以验证,在参考频率fi=10 MHz和信道间隔0.375 MHz的给定条件下,将PLL的各分频器配置成:R=160,A=3+6k(k=0,1,2,…)和B=412+3m(m=0,1,2,3,…),则PLL作为本地振荡器产生的输出频率为

即证之这种配置方法可行。

1.3.2 单频点PLL频率合成器中的R与N分频器的配置方法

通常等频率间隔的多信道信号经混频器下变频后,输出的第一中频71 MHz固定频点信号,再经第二混频后得到一个10.7 MHz的第二中频信号,PLL作为混频器的本地振荡器仅需要输出一个81.7 MHz的固定频率信号,即:fout=fi(A+P×B)/R=fi(A+8×B)/R=81.7 MHz,(A+8×B)。

由于是点频工作,PLL的环路滤波器设计对相频检测频率fPFD=fi/R不再有限制。在给定的参考频率fi=10 MHz的条件下,R的取值只需保证10fi/R为整数即可。当取R=100时,则10fi/R=1,即可满足要求(对应地PLL相频检测频率为0.1 MHz),上式变为:817=A+8×B,即B=(817-A)/8。若取A=17时,则B=100。可以验证,在参考频率fi=10 MHz的给定条件下,给PLL的各分频器配置成:R=100,A=17,B=100,则PLL作为本地振荡器产生的输出频率为81.7 MHz,即证之。

2 结论

通过改变参考频率源与锁相环参考频率输入端之间的馈电电路形式,既改善了晶体振荡器的负载端接条件,又滤除掉了高次谐波成分,增强了锁相环参考频率信号的输入功率,提高了相位噪声性能。通过对传统的VCO输出T型电阻功率分配网络的改进,调整了VCO输出的功率分配比例,减小了因功率过多地分配给PLL反馈支路所造成的损失,最大限度地把VCO的功率分配给端接负载,提高了锁相环频率合成器的输出功率。给出了多频点和单频点PLL频率合成器中R与N分频器的通用配置方法。实验验证了理论分析和设计方法的正确性。

[1]远坂俊昭.锁相环(PLL)电路设计与应用[M].何希才,译.北京:科学出版社,2006:1-14.

[2]黄智伟.无线发射与接收电路设计[M].北京:北京航空航天大学出版社,2004:8-14.

[3]白居先.低噪声频率合成[M].西安:西安电子科技大学出版社,1995:90-109.

[4]张厥盛,郑继禹,万心平,等.锁相技术[M].西安:西安电子科技大学出版社,2006.

[5]GARDNER F M.锁相环技术[M].北京:人民邮电出版社,2007:80-102.

[6]TI.High-performance integer-N PLL frequency systhesizer[EB/OL].http:∥www.ti.com/.