基于CycloneII EP2C20的8051IP核的应用研究

樊 峰,陈西曲,叶艳艳

(武汉工业学院电气与电子工程学院,湖北武汉430023)

随着数字集成电路的应用越来越广泛,微电子技术以及EDA(Electronic Design Automation,电子设计自动化)技术的快速发展,利用FPGA(Field-Programmable Gate Array,现场可编程逻辑门阵列)来进行ASIC(Application Specific Integrated Circuit,专用集成电路)的设计也越来越流行;不仅仅如此,得益于半导体工艺技术的不断发展,可集成的晶体管数目已经可达到几千万个,从而使得微电子及其应用领域又发生了一场革命性变革——SOC(System On Chip,片上系统)技术的研究应用和发展。SOC技术是以IP(Intellectual Property,知识产权)核复用技术为支撑[1],基于IP核的SOC设计具有易于增加新功能和缩短上市时间的显著特点,是IC设计当前,乃至以后的主流设计方式,因此开发研究可综合的IP核对SOC技术的发展有着很重要的意义。

1 8051IP核整体系统构建

基于VerilogHDL语言设计综合的8051IP核,其指令集和标准的8051微控制器完全兼容[2];同时兼容汇编程序和C语言程序,其指令执行时间为1—4个时钟周期,执行性能却大大优于8051MCU;并且与标准的8051拥有基本相同的内部机构,都是由8-bit微处理器(CPU)、128字节的片上数据存储器(RAM)、4K字节的片上程序存储器(ROM)、两个16位的定时计数器、全双工的通用异步接收发送器(UART)、两个优先级的5个中断源、4个I/O口(P0、P1、P2、P3)这8 个主要模块组成。

1.1 8051IP核的顶层结构

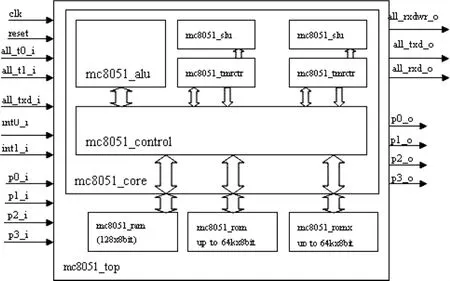

自顶向下(Top—Down)的设计方法正是EDA技术相对传统电子设计方法的优势所在,Top—Down设计方法的第一步就是要绘制顶层设计图[3]。图1所示为MC8051 IP核的顶层结构图,它显示了MC8051 IP核的顶层结构与三个存储模块的连接关系,以及输入/输出口。在MC8051 IP核的设计中,微处理模块由运算器(ALU)模块和控制器模块组成,并且为了便于IC设计,MC8051 IP核的I/O口并没有提供复用功能,包括4个8位输入输出口、串行接口、计数器输入口和外部中断输入口。各I/O信号的描述如表1所示。

图1 MC8051 IP核顶层结构图

表1 顶层信号名

1.2 MC8051 IP核内部各模块的构建

mc8051 IP核的内部结构模块主要是存储模块和控制模块,存储模块包括RAM、RAMX和ROM,控制模块包括处理模块和数据输出模块,即顶层结构中的mc8051_core模块。

1.2.1 ROM和RAM模块的生成

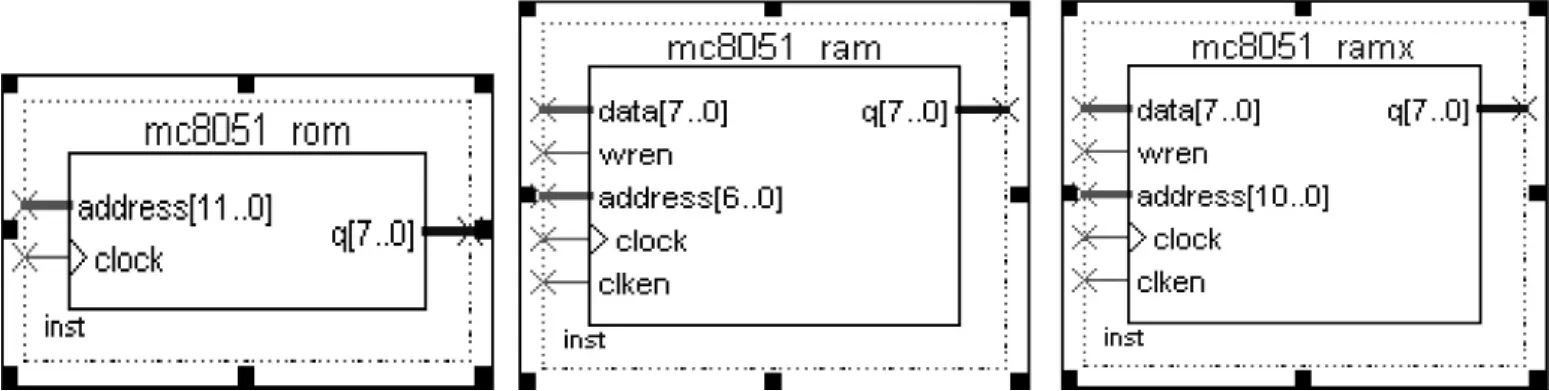

MC8051 IP中所需要的存储模块有RAM、外扩RAM、ROM,其中内部RAM和ROM是必要的,内部RAM固定为128 Bytes,ROM最大可选64 Kbytes,并且外部扩展RAM可选,最大可达64 Kbytes。

RAM和ROM的生成都是利用QuartusII软件自带的功能模块,通过【Tools】>>【MegeWizard Plug-In Manager..】生成。首先新建一个QuartusII工程,进入功能模块创建向导,通过功能模块创建向导最终创建的RAM和ROM模块如图2所示。

图2 RAM、ROM模块电路图

RAM和ROM的创建没有太大的区别,ROM的创建过程中,需要对其进行初始化,可以添加测试代码,而RAM不需要初始化。

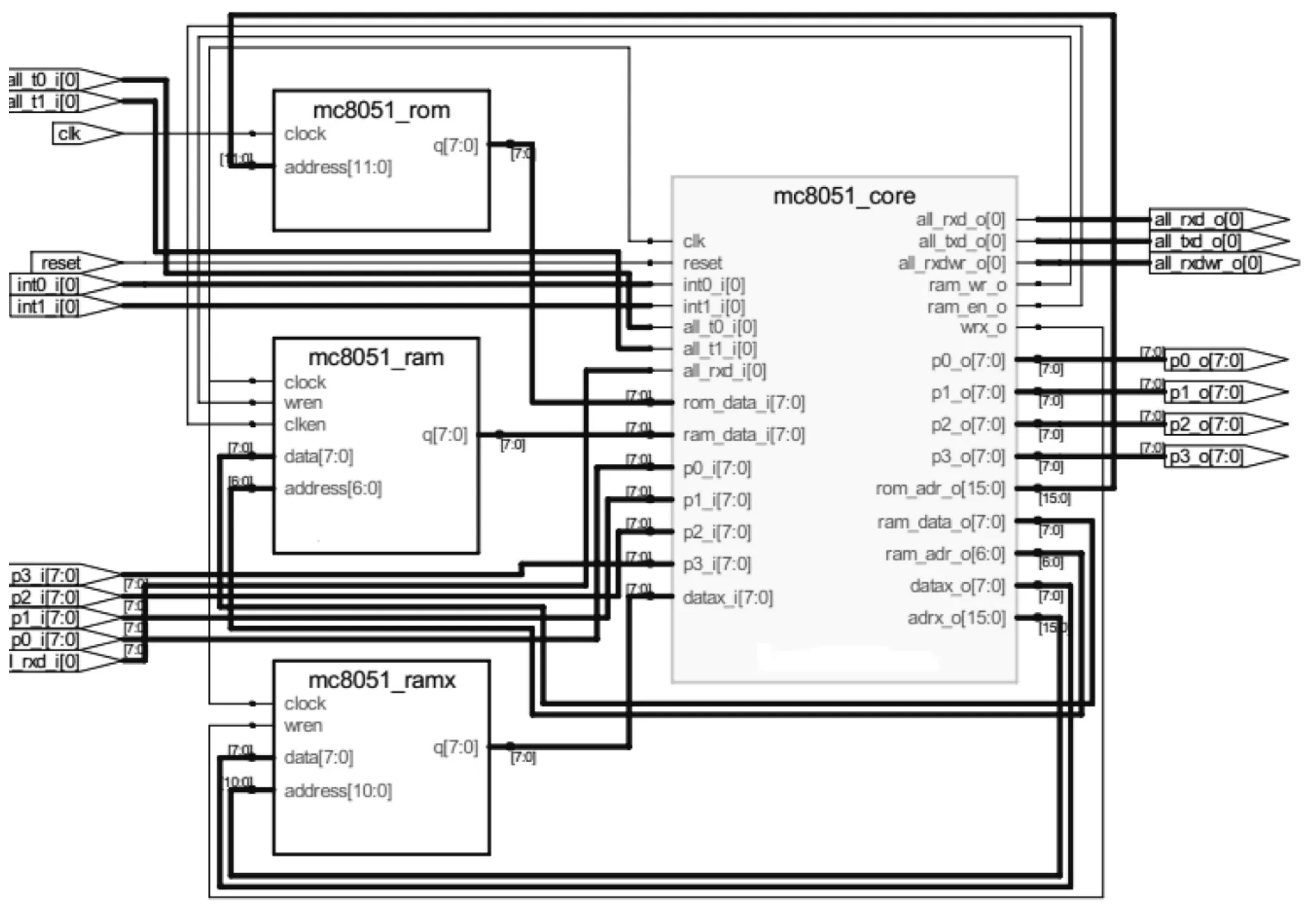

1.2.2 mc8051_core模块的创建

mc8051_core模块包含了处理模块和数据传输模块,是整个模块的核心;模块的封装需要通过第三方的综合软件,如Synplify Pro软件实现;首先将前面创建的存储器模块添加到工程中;然后利用综合软件进行综合生成 mc8051_top.vqm文件[4],综合编译后通过RTL图来检查模块之间连接情况,综合后得到的RTL图如图3所示。

图3 mc8051_core RTL图

2 MC8051应用测试模块的创建

2.1 MC8051应用系统模块的创建

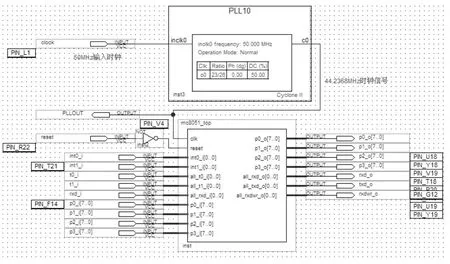

首先打开QuartusII软件,新建一个工程,将上面创建好的mc8051_top.vqm添加到工程中,打开创建的应用设计顶层图形设计文件mc8051_top.bsf,为了更好地进行板级测试,并为51核提供合适的时钟,需要为系统添加一个PLL模块,以便输出合适时钟频率;添加PLL模块和添加存储器RAM一样,通过【Tools】>>【MegeWizard Plug-In Manager..】生成,只需要设置好输入时钟和输出时钟即可;模块添加完后根据开发板引脚连接设置模块引脚分配,最后进行编译;编译成功后,得到应用系统顶层原理图如图4所示。

图4 系统顶层原理图

2.2 MC8051应用系统测试程序

MC8051 IP核完全兼容标准8051指令集,编程语言可以采用C语言,也可采用汇编语言,且可以采用熟悉的开发工具进行应用程序的编写。本系统采用C语言来编写测试程序,且在Keil平台下开发软件。主要测试MC8051 IP核的串口、定时/计数器、中断、I/O等模块,将通过Keil软件编译后生成的.HEX文件加载到QuartusII工程文件目录中,并将其初始化到8051IP核的ROM中,然后重新编译工程生成的配置文件.sof,最后利用QuartusII的下载工具将配置文件下载到EP2C20实验板中实现8051现实应用系统的测试。

2.2.1 外部中断0的测试程序

void key_down()interrupt 0

{

EX0=0;//关闭外部中断0,进行中断处理

led<<=1;//led左移以为,实现下一个灯点亮

P1=led;//将led值赋值给P1口,P1口连接led灯

if(led==0x00)

{

led=0xff;

}

EX0=1;//打开外部中断0,继续接收外部中断0的中断请求

}

利用按键来产生外部中断,P1口读取led的数据来实现按键控制流水灯的控制。

2.2.2 串口接收发送测试程序

char putchar(char ucWriteData)//串口发送程序

{

SBUF=ucWriteData;//将要发送的数据读入SBUF寄存器

while(TI);

TI=0;//判断数据是否读完

return(ucWriteData);//发送数据

}

void UartIsr(void)interrupt 4//串口中断

{

if(TI)//发送中断

{

TI=0;

}

if(RI)//接收中断

{

RI=0;

Rev=SBUF;

flag=1;

}

}

3 应用测试结果与分析

将构建好的测试系统初始化到IP核的ROM中,并对整个系统进行编译调试,并下载到EP2C20F484N7开发板中,利用程序控制,当有按键按下后,触发外部中断0,点亮第一个LED,再次按键,点亮第二个LED灯,从而实现流水灯操作。

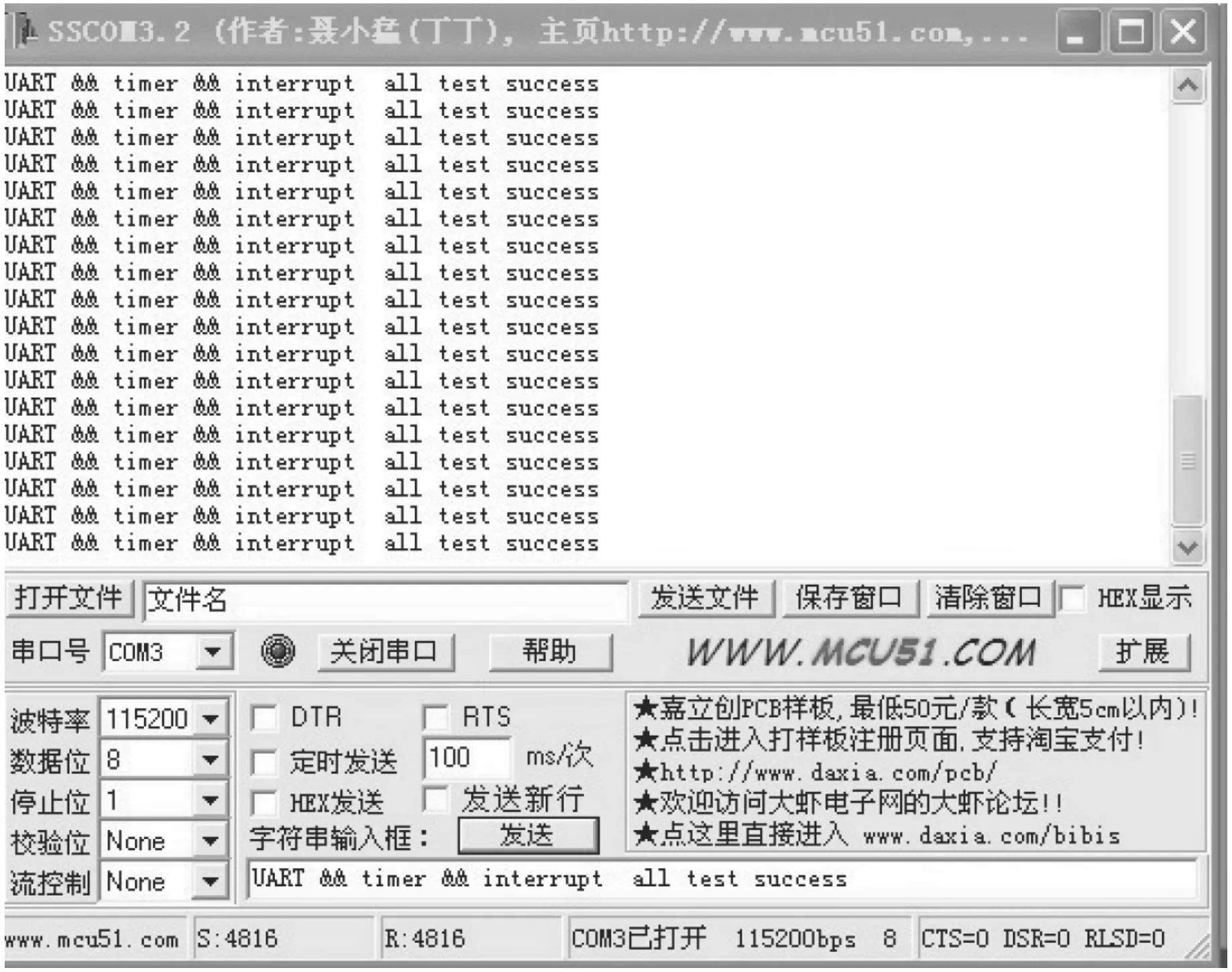

串口通信测试结果如图5所示,利用定时器1产生115200的波特率来实现串口数据的发送和接收,利用串口调试助手通过串口发送数据到开发板上,开发板接收数据后再次发回给PC机,从而实现8051IP核的串口通信控制。

图5 串口通信控制图

4 结束语

基于EP2C20F484N7的8051 IP核的测试结果可知,8051 IP核的串口、I/O口、定时器、中断系统、运算单元、存储器单元都能够稳定的运行。运用FPGA实现的8051IP核,在高时钟频率、稳定程度、易于升级、易于扩展使用等诸多方面相对传统的8051都有了很大的提高,从而大大提高以8051单片机为控制系统的各种应用系统的性能参数。研究8051IP核不仅可以更好的扩展存储模块的大小,更能够利用FPGA系统的丰富资源和IP核的复用技术,开发大规模的工程设计以及和其它模块的集成融合,例如移植简单的TCP/IP协议,实现一个完整的SOC功能。由此可知8051 IP核良好的复用性和可移植性在实际应用中有重大的意义。

[1] 史江义.基于IP核的SOC设计关键技术研究[D].西安:西安电子科技大学,2007.

[2] 张毅刚,彭喜元,董继成.单片机原理及应用[M].北京:高等教育出版社,2003.

[3] 刘小俊.基于EDA技术的兼容MCS-51单片机IP核的设计[D].武汉:武汉理工大学,2005.

[4] 李洪伟,袁斯华.基于 QuartusII的 FPGA/CPLD设计[M].北京:电子工业出版社,2006.