基于FPGA的车载图像记录仪设计

马轶男,陈 鹏,代东林,郭查清,沈志熙

(重庆大学 自动化学院,重庆 400044)

现代化交通的迅猛发展,在带给人们极大便利的同时也导致了交通事故的不断增多。这些事故大部分都是由于非规范行驶、超车、超速等造成的。然而,由于缺乏事故发生时的相关有效信息,使得事故责任的鉴定十分困难。为此,设计开发一种能够记录车辆行驶状态信息的车辆行驶记录仪,对于有效监督驾驶人员的驾驶行为,判断交通事故责任具有重要意义。

从技术上讲,目前汽车行驶记录仪多采用单片机来实现,主要记录汽车本身的运行参数。文献[1]提出了基于单片机的汽车行驶记录仪的设计,以实现对速度、加速度和开关量的测量,并产生对应的时间信息。文献[2]提出了一种多功能汽车行驶记录仪的系统设计方案,能够对时间、日期、车辆行驶速度、行驶里程等数据进行测量、记录和存储。但这些数据大多为文本格式,缺乏直观性。为此,文献[3]提出了一种基于ARM7的车载图像记录仪的设计方案。该方案采用ARM7作为系统核心芯片,用CMOS图像传感器实时采集图像数据,大容量图像信息数据的存储采用SDRAM与NAND型Flash双存储器结构来完成。文献[4]采用了 ARM9+DSP的系统结构,以ARM9作为主控制器,DSP实时地对送来的多路数据流进行分时压缩,但ARM由于计算速度和成本上的限制,更适合做事务处理和科研应用。

本文在学习和借鉴已有设计的基础上,对比和分析图像应用领域的主流核心处理器方案,提出了一种基于FPGA的车载图像记录仪实现方案,通过记录车辆行驶过程中的图像资料,为交通事故的责任判定提供了直观信息。

1 系统总体结构及工作原理

车载图像记录仪主要由控制模块、采集模块、存储模块和通信模块4个部分组成,其中:采集模块以SAA7113H作为A/D转换芯片,负责将模拟图像数据转换成数字图像数据后送入FPGA中;存储模块采用了SDRAM+Flash的存储结构,主要任务是将转换后的数字图像数据完整地保存;通信模块采用CY7C68013作为 USB接口芯片,将Flash中的数据传输到PC机中以便后续处理。整个系统以Altera公司的型号为EP2C20F484C8的FPGA芯片作为控制核心。系统结构如图1所示。

图1 系统总体结构

记录仪的工作原理为:记录仪启动后,首先对SDRAM和SAA7113H进行初始化;初始化成功后,SAA7113H将CCD传感器采集的模拟视频信号转换成数字信号传送给FPGA,此时,FPGA控制SDRAM实现图像数据的缓存;当存完一帧图像以后,FPGA发出控制信号,将SDRAM中的数据转存入FLASH中,完成实时图像的采集;FPGA在检测到启动数据传输信号后自动将数据通过USB接口传送给计算机。

此外,该记录仪还包括为各芯片、外围设备、I/O接口等供电的电源电路,为芯片内外时钟控制器提供工作时钟的晶振电路,以及芯片的复位电路等。

2 系统主要功能模块设计

2.1 控制模块设计

控制模块采用FPGA作为核心处理器,型号是 Altera公司的 cycloneII系列芯片EP2C20F484C8。FPGA拥有丰富的寄存器资源,适合于同步时序电路较多的数字系统,具有高速、高可靠性、功耗低等优点,不但可以使系统的集成化大为提高,而且还可以根据后期现场的需要进行现场编程,使得设计开发过程和后期现场调试都比较灵活[5-8]。这些优点使FPGA在数字图像系统中有着极为广泛的应用。控制模块是整个系统逻辑控制的核心,它的主要任务有:①实现虚拟I2C总线对SAA7113H进行正确的初始化;② 初始化SDRAM并控制SDRAM和FLASH对图像数据进行正确存储;③控制USB接口芯片将数据传输到PC机上;④ 控制图像数据的提取并作为数据在各模块中传递的通道;⑤ 保证各模块之间的时序匹配等。

2.2 采集模块设计

采集模块负责将模拟图像信号转换成数字信号并输入到FPGA中。设计采用Philips公司型号为SAA7113H的视频解码芯片。它是一款功能强大且操作简单的9位视频输入处理芯片,采用CMOS工艺,通过I2C总线与控制模块相连构成应用系统,实现将CCD传感器输出的模拟信号转换成数字图像信号[5]。它具有低功耗(<0.5 W)、低电压(3.3 V)、小封装(QFP44)的特点,非常适用于本系统。

需要注意的是,系统上电后,芯片不是立即采集模拟视频信号进行A/D转换处理输出数字信号,它必须由前端处理器通过I2C串行总线对其内部寄存器进行初始化配置后,才能正常工作。因此,对采集模块的控制,一个主要的任务就是完成对SAA7113H的初始化,也就是对其寄存器的正确配置,即首先是对I2C总线上的SAA7113H进行寻址,然后再将初始化值写到SAA7113H的寄存器中。根据设计要求SAA7113H的器件读写寻址字节SLA分别为4BH、4AH。利用虚拟I2C总线接口,将地址为12H、13H和58H的寄存器分别配置为7AH、01H和40H,其余寄存器保留默认值。详细的内部寄存器控制位的功能含义见文献[9]。初始化成功后,SAA7113H将CCD摄像头传送的模拟图像信号进行A/D转换,送入FPGA中。

图2为SAA7113H与FPGA的硬件连接,其主要引脚有视频信号输入引脚AI11、24.567MHz晶振输入引脚XTAL1、SCL和SDA组成的I2C总线接口、同步信号RST0和RST1以及解码后的数据输出引脚VPO[7:0]。

图2 SAA7113H与FPGA的硬件连接

2.3 存储模块设计

存储模块负责将解码后的数字图像信号完整地保存下来。为了尽量减少对图像质量的影响,采用直接将图像数据进行完整保存的方式,而不进行压缩处理,因此,记录仪存储的图像数据量非常庞大。考虑到现有的非易失性Flash存储器无法满足图像采集的实时性要求,而DRAM具有数据掉电易失性,存储模块采用了SDRAM与Flash共同组成的二次存储结构以保证图像数据的正确存储。SDRAM选用Micron公司的高速 CMOS同步动态随机存储器,型号为 MT48LC4M16A2。FLASH选用的是 SamSung公司的NANDFLASH,型号为K9F2G08U0M。

Micron公司的SDRAM的控制逻辑复杂,命令种类多样,在使用时需要考虑到周期性刷新、行列管理以及初始化等操作,因此需要设定1个SDRAM控制器来屏蔽掉SDRAM严格的状态机存储单元管理和刷新操作,提供1个类似于静态SDRAM的存储访问接口。SDRAM的主要引脚有A0~A11(地址输入引脚)、DQ0~DQ15(数据输入输出引脚)、CLK(时钟信号输入引脚)、CKE(时钟使能)、/CS(芯片选择)、/RAS(行地址选择)、/CAS(列地址选择)、/WE(写使能)、BA0-BA1(Bank地址输入信号引脚)等。

SDRAM在工作之前,需要进行初始化。初始化SDRAM和SDRAM控制器的流程为:上电之后需要一个100 μs的延迟以稳定内部电源和时钟电路,然后进入初始化操作:①预充电所有Bank;②至少执行2次自动刷新操作;③ 配置SDRAM模式寄存器;④ 配置SDRAM控制器内部寄存器2(REG2);⑤ 配置SDRAM控制器内部寄存器1(REG1)。此时,SDRAM和SDRAM控制器初始化完毕。SDRAM的模式寄存器一般被用于定义SDRAM的运行模式,在配置模式寄存器命令有效时由地址线A11~A0载入,其中:A0~A2用来定义突发长度(burst length);A3定义突发类型;A4~A6定义cas延迟;A7~A8定义运行模式;A9定义写入突发模式;A10和A11目前保留。根据设计要求,SDRAM模式寄存器的设定值为37H,REG1的设定值为12FH,REG2的设定值为5F6H。

SDRAM没有读写次数的限制,并且可以实现实时存储。但是,SDRAM存在掉电易失性,因而需要在完整存完一帧图片后将SDRAM中的图像信号及时转入Flash中。NAND型Flash具有读写速度快、存储密度大、可擦除、非易失以及命令、地址、数 据 线 复 用 和 接 口 便 利 等 特 点[10]。K9F2G08U0M的数据寄存器写入速度可达33 MB/s,但考虑到设计的可靠性,在设计时选择使用25MH的时钟设计,并在FPGA中开辟2个双口RAM作为数据缓冲区,大小为2 048×8 bit。当RAM1写满时,将RAM1中的数据加载到Flash的数据寄存器,同时将下一页的数据写入RAM2中。Flash设置为最大编程时间700 μs。

存储模块与FPGA的硬件连接图如图3所示,其中K9F2G08U0M的主要引脚有CLE(命令锁存允许)、ALE(地址锁存允许)、CE(片选)、WE(写允许)、RE(读允许)、WP(写保护)、R/B(准备好/忙)、PRE(上电读使能)、I/O0 ~I/O7(输入/输出)。

2.4 通信模块设计

通信模块负责将Flash中的图像数据传输到PC机中以便后续处理。USB芯片选择的是Cypress公司的 CY7C68013。CY7C68013芯片属于Cypress公司的FX2系列产品[11],在数据传输时主要利用了 4 kB的 FIFO,分为 7个端点:EP0、EP1IN、EP1OUT、EP2、EP4、EP6 和 EP8,其中 EP0、EP1IN和EP1OUT是3个64 B的缓存,只能被固件访问。EP0是一个默认的数据输入输出端口缓存,只能配置为控制传输;EP1IN和EP1OUT是单独的64 B缓存,可以配置这些端点为中断传输或批量传输;端点2、4、6、8是大容量高带宽的数据传输端点,可以配置为各种带宽以满足实际需要,端点2、4是输出端点,端点 6、8是输入端点。内部的传输控制是通过空和满2个控制信号来完成的,当端点为满时不能再写数据,当端点为空时不能再对FIFO进行读。

图3 存储模块与FPGA的硬件连接

在本系统中,USB的接口模式采用的是Slave FIFO模式,即FX的CPU不直接参与 USB数据处理,而只是作为USB和外部数据处理逻辑之间的通道,数据流通过FX的FIFO直接传输。设计采用异步读、写方式,由FPGA芯片作外部的主控制器,对端点2和端点6进行异步方式的读、写控制。图4是USB芯片与FPGA的接线图,其中:IFCLK为接口时钟,由芯片内部产生30 MHz时钟,接入FPGA芯片,用以产生频率较高的SLRD信号和SLWR信号;FLAGA-FLAGD为FIFO标志管脚,用于映射FIFO的当前状态,系统中分别用来标志端点2和端点6中FIFO的空、满标志,由寄存器PINFLAGSAB和PINFLAGSCD配置;FD[15:0]为16位双向数据总线,在系统中作为传递控制字和数据的通道;FIFOADR[1:0]用于选择当前操作的端点缓冲区,如表1所示;SLOE用于使能数据总线FD的输出,当SLOE信号有效时,才能开始从端点2读入数据;SLRD和SLWR分别作为FIFO的异步读、写选通信号。

图4 USB芯片与FPGA硬件连接

表1 端点配置

3 实验结果及功能验证

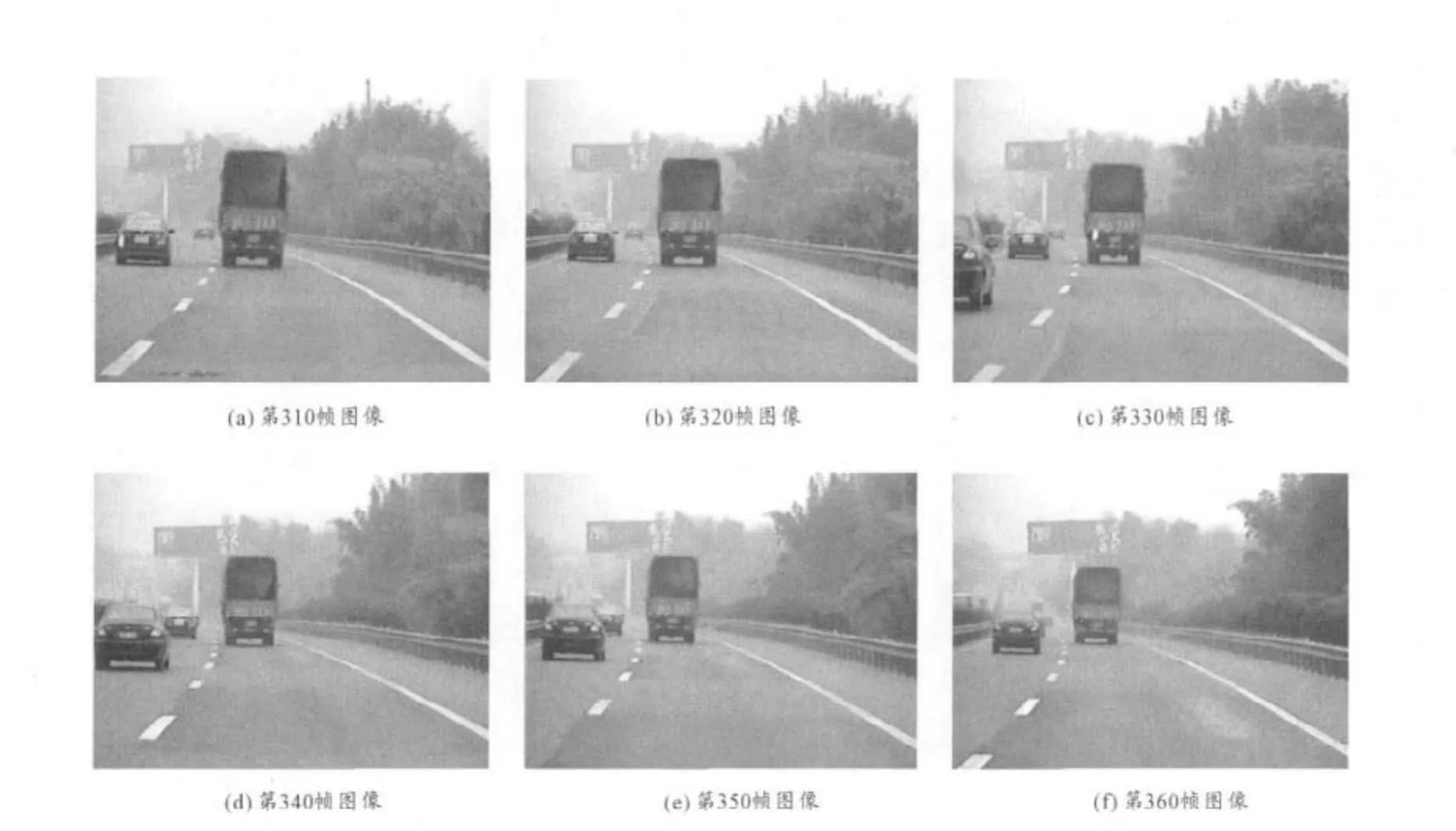

为测试记录仪图像采集效果,在汽车上进行了实际的调试实验,并将记录仪采集到的图像数据传输到PC机上分析实验结果。记录仪每秒钟能够存储约13帧大小为320×240字节的图片,最大存储容量为2 000帧。图5为将数据上传到PC机后,经 Matlab 还原后的第 310、320、330、340、350、360 帧图像。

图5 实验结果图像

实验结果表明,本记录仪能够有效存储汽车行驶过程中的前方图像数据,保证了系统实时性与可靠性的要求。

4 结束语

在FPGA的控制下,图像信号通过SAA7113H转换为数字信号,存储到由SDRAM与Flash组成的二次存储结构中。最后通过USB接口传输到PC机上供后续处理。该记录仪将图像技术应用到汽车电子方面,以图像的方式记录了交通事故发生的过程,为交通事故的责任判定提供了直观的材料,对解决目前交通事故责任判定的困难提供了一条比较有效的途径。

[1]苏晓东.基于单片机的汽车行驶记录仪的设计[J].信息技术,2009(8):2 -4.

[2]彭李明,连迅.多功能汽车行驶记录仪的系统设计[J].电子测量技术,2009(3):2 -4.

[3]叶林,李凌,张洪,等.新型车载图像记录仪[J].仪表技术与传感器,2005(10):1-2.

[4]余水,邓振,蔡洪斌,等.基于ARM+DSP的汽车视频黑匣子系统的总体设计术[J].计算机应用研究,2008(2):628-631.

[5]郑千洪,王黎,高晓蓉.基于FPGA的图像采集卡的设计[J].现代电子技术,2007(20):2-3.

[6]黄军友.基于OFDM技术FFT的FPGA研究[J].重庆三峡学院学报,2010,26(3):50 -54.

[7]邱震,靳世红,王晓东.基于FPGA的某型雷达视频采集预处理模块设计[J].四川兵工学报,2010,31(5):33-35.

[8]于亚萍,刘源,卫勇等.基于FPGA农村泵站远程监控系统的设计[J].安徽农业科学,2010,28(22):12117- 12118.

[9]Philps Corporation.SAA7113H datasheet[Z].Holand:Philps Corporation,1999.

[10]张元凯,靳世久,李一博,等.超大容量存储器K9F2G08U0M及其在管道通径仪中的应用[J].电子技术应用,2007(1):1 -4.

[11]谭安菊,龚彬.USB2.0控制器 CY7C68013与 FPGA接口的 Verilog HDL实现[J].电子工程师,2007(7):52-54.