ADS5287及其在MIMO接收机中的应用

刘晓明,何 徽,吴皓威,汪梦柔

(重庆大学 通信工程学院,重庆400030)

随着各种无线通信业务和宽带数据业务的不断发展,无线频谱资源越来越紧张。如何更高效地利用有限的频谱资源成为无线通信研究的焦点。多天线技术(MIMO)充分利用了空间资源,可以通过空间复用、空间分集或智能天线技术,达到提高数据比特率、降低误码率或提高信噪比的目的。MIMO技术可以在不增加系统带宽和天线总发射功率的情况下大幅提高信道容量,近年来成为无线通信研究的热点,得到了较为广泛的应用。

在MIMO接收机中,多根接收天线对模数转换模块的通道数目提出了要求,而且要求各通道的信号延迟和增益要相同。TI公司的8通道模数转换器ADS5287的时钟分配电路能将各通道的孔径延迟误差控制在±20 ps以内,并且8个模数转换通道均使用同一个参考电压,保证各通道的延迟和增益是相同的,所以该芯片适合用于MIMO接收机的模数转换。另外,TI公司在ADS5287的制造过程中,对每一块芯片的内部参考电压电路进行了校准,使得不同的芯片之间的参考电压一致,有利于在一个设计中使用多块ADS5287,同时保证每一个通道的增益相同,便于对系统的天线数目进行扩展。所以,本文选用ADS5287设计了用于MIMO中频接收机的硬件电路。

在该设计中输入信号为中频信号,在设计AD前端驱动电路时需要考虑与中频输入信号线阻抗匹配的问题。ADS5287采样为中频采样,采样频率较高,同时每个通道的数据输出方式为串行输出,数据速率高达650 Mb/s。所以在PCB设计中需要充分考虑数字信号的完整性问题。

1 系统结构

系统结构框图如图1所示。本设计采用TI公司的ADS5287对射频前端输出的8路中频信号进行采样,采用MINI公司的RF变压器TC1-1T+将单端中频信号转换为差分信号,作为ADS5287的模拟输入。采用Altera公司的CycloneⅢ系列FPGA芯片EP3C120F780C7N作为信号处理芯片,对模数转换得到的数据进行数字下变频及基带信号处理。使用TI公司的时钟发生芯片CDCE62005为AD采样芯片和FPGA提供时钟。使用宏晶公司的单片机STC89LE52来配置CDCE62005和ADS5287。

2 ADS5287简介

ADS5287是一款高性能、低功耗的8通道模数转换器,分辨率为 10 bit,最高采样率可达 65 MS/s,模拟输入带宽为520 MHz。ADS5287由时钟管理、模数转换、片内参考电压电路、控制寄存器、并串转换、LVDS驱动、功耗管理等模块组成。

ADS5287的采样时钟输入电路支持LVCMOS、LVPECL和LVDS电平标准。ADS5287中从时钟源到各个通道采样电路的时钟路径匹配,保证了各通道之间的孔径延迟误差在±20 ps以内。

由于采用了基于开关电容的差分采样保持结构,ADS5287的模拟输入电路在输入信号频率较高或采样频率较高的情况下仍然具有良好的交流性能。在输入模拟信号频率为25 MHz、采样频率为65 MS/s的条件下,其信噪失真比(SINAD)可达 62 dB[1]。

ADS5287内部用一个参考电压电路为8个ADC通道提供参考电压,这样,同一块芯片上的8个ADC通道所使用的参考电压均相同。另外,在制造过程中,每一块芯片的参考电压都经过校正,保证了不同芯片之间的ADC通道所使用的参考电压都是相同的。这有利于在一个MIMO接收机中使用多片ADS5287,同时保证每一个ADC通道的增益相匹配,便于对系统的天线数目进行扩展。

ADS5287内部有一组控制寄存器,控制整个芯片的工作方式。控制寄存器可以通过信号线CS、SCLK和SDATA按照规定的时序串行配置。通过对控制寄存器的配置,可使芯片工作在不同的模式。例如,可使整个芯片或部分ADC通道工作在休眠模式以节省功耗,可以选择LVDS输出的驱动能力以适应不同的负载等。在使用时可根据需要对ADS5287进行配置。

3 中频接收机中ADS5287外围电路的设计

3.1 时钟

对于模数转换器,时钟信号的稳定性很重要。采样时间的定时误差将造成采样幅度的误差,进而降低信噪比。模数转换器的信噪比和各影响因素的关系[5]如下:

其中,fa为输入模拟信号的频率,tJ为时钟信号抖动的RMS值,ε为 ADC的平均 DNL,N为 ADC的分辨率,Vn为热噪声。由式(1)可知,当信号输入频率较高时,时钟的稳定对信号的SNR影响很大。所以在本设计中使用TI公司的低抖动时钟发生芯片CDCE62005为ADS5287提供LVDS电平的时钟信号。时钟信号采用交流耦合方式。差分的时钟驱动有利于抑制共模噪声对时钟的干扰,降低时钟抖动,提高时钟稳定性。

3.2 模拟输入

ADS5287的模拟信号输入端需要从外部提供1.5 V的直流偏置电压,该电压可由ADS5287的Vcm引脚提供。ADS5287的模拟输入引脚需要一个直流偏置电流,8个ADC的输入总共需要直流电流的强度[1]为:

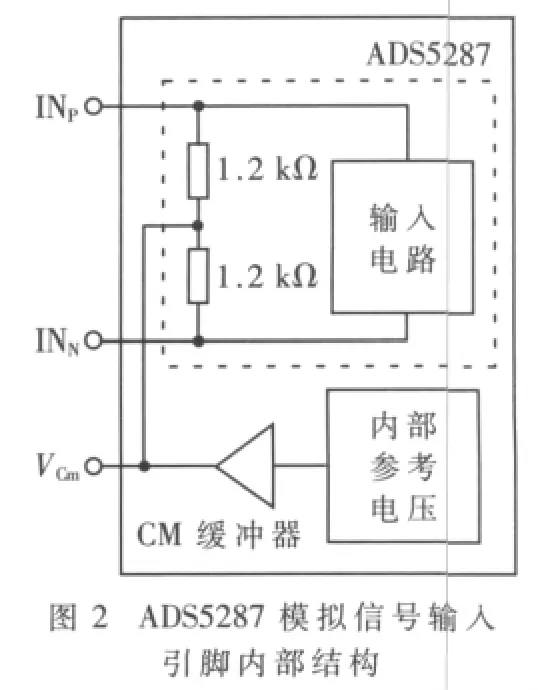

其中,fs是实际的ADC采样率。如果ADC的前端驱动采用直流耦合方式,则驱动端的直流驱动能力必须满足式(2)。实际上,每个模拟输入引脚在芯片内部通过1.2 kΩ的电阻连接到Vcm引脚,如图2[1]所示。 当ADC的信号输入采用电容交流耦合方式时,由Vcm引脚通过芯片内部的1.2 kΩ电阻提供输入端所需的直流偏置电压和电流。在这种情况下,从Vcm注入模拟输入引脚的电流将会在1.2 kΩ的电阻上产生压降,压降幅度由采样频率决定。例如,当采样频率为 50 MS/s,则将该采样频率代入式(2),在内部电阻上产生的压降为:

这对于ADS5287来说是不可接受的。所以在这种情况下不宜采用电容耦合方式。

另外,模拟信号的前端驱动方式还要考虑阻抗匹配问题,根据传输线理论,在高频信号的传输路径中若阻抗不连续,将会发生反射。如式(4)所示[6],其中Γ是反射系数,为阻抗不连续处反射电压与入射电压的比值。要减小反射系数,就要使负载的阻抗尽可能与传输线阻抗匹配。

基于以上两点考虑,本文中设计的模拟输入驱动电路如图3所示,ADS5287的Vcm引脚接到IF变压器的次级线圈的中间抽头,为模拟信号输入端提供直流偏置电压和直流偏置电流。该偏置电流将在R514和R515上产生压降,但因为R514和R515的值很小,该压降也很小,在采样频率为 50 MS/s的情况下,由式(5)计算得出,仅为0.59 mV,可以忽略。

阻抗匹配通过R509实现。ADS5287输入端阻抗很大,近似地看作是无穷大。故R509与后级电路并联后的阻抗仍为 49.9 Ω。TC1-1T+为 1:1变压器,所以从变压器初级线圈看,输入阻抗为49.9 Ω,与传输线的阻抗相匹配,可以减小IF输入端的信号反射。R514和R515的作用是减小由采样电流和寄生参数共同造成的振铃,减小采样频率的泄漏。

3.3 参考电压

ADS5287的参考电压的产生方式可以很灵活,有3种模式可供选择:内部产生、外部输入参考电压或外部输入VCM电压。

在本设计中,内部产生模式能够满足应用,并且使用内部模式不需要另外提供电压源,可简化电路设计。所以在本文的设计中,ADS5287的参考电压的产生采用内部产生的模式。

在内部产生模式下,内部参考电压电路产生REFt(2.5 V)、REFb(0.5 V)、Vcm(1.5 V),供 8 路 ADC 使用。REFt(2.5 V)和 REFb(0.5 V)电压差值为 2.0 V,决定了模拟输入信号的差分电压动态范围为2.0 Vpp。Vcm为1.5 V,模拟输入信号的直流偏置电压范围为1.5 V±0.05 V。

4 PCB设计与信号完整性仿真

4.1 PCB设计

考虑到该设计是用于MIMO技术的,因此各通道的信号应该同时到达ADC,故各通道的模拟信号线之间应该等长。另外,因为在该应用中ADS5287的采样率较高,而数据输出是串行输出,因此数据输出的信号速率很高。例如,若采样率为65 MS/s,AD采样分辨率为10 bit,则数据传输速率为 65×10=650 MHz。 这就要求在PCB设计时要充分考虑信号完整性问题和时序问题。需要慎重选择PCB的层叠结构、各类信号线的线宽,线距以控制走线的阻抗和差分线的差分阻抗。在本设计中,采用6层板,层叠结构为:信号-地-信号-电源-地-信号,层间填充介质选用介电常数为4.8的FR4。顶层信号层和底层信号层到地层距离为5 mil,顶层和底层单端信号走线线宽为 6 mil,走线的特性阻抗为57.34 Ω。顶层的差分信号走线线宽为 5 mil,间距为 5 mil,差分阻抗为 100.31 Ω。

各通道的差分数据线之间应该等长,且与时钟线等长。另外,每根差分对的差分线之间也要求等长、并且差分对内部两根差分线之间的等长要优先于差分对之间的等长,因为差分对内部差分线之间的长度不匹配会同时带来信号完整性问题和时序偏移问题。为了满足上述布线规则,PCB布线采用了蛇形走线。在布线设计时严格控制了 ADCLK、LCLK、OUT1~OUT8这 10对差分线的线长,任何两根线的长度偏差保持在±5 mil之内,保证了各信号在PCB走线上的传输延迟偏差很小(在±0.83/s之内),可以忽略。

4.2 信号完整性分析

在本文所设计的系统中,ADS5287的8个数据通道的输出以及2个时钟输出为高速信号线,数据速率高达650 Mb/s,均采用LVDS电平标准。为了验证高速信号线的信号完整性,在完成系统的PCB设计之后,使用Hyperlynx软件的Boardsim工具对PCB设计进行了信号完整性分析。仿真中,ADS5287和EP3C120F780C7N所使用的模型均为制造商提供的IBIS模型,所以得到的结果具有重要的参考价值。

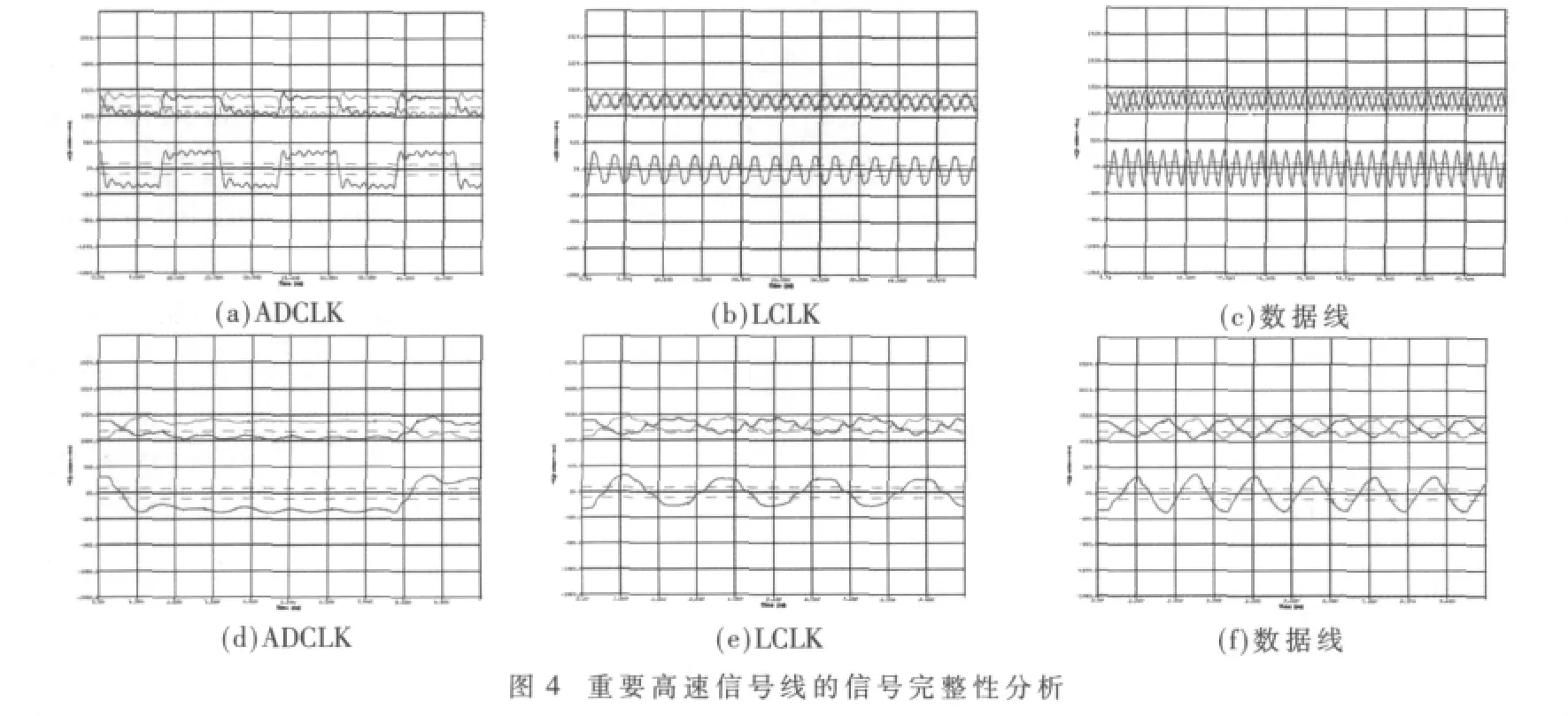

4.2.1 反射分析

图4所示为对三种信号线接收端波形仿真的结果,(a)、(b)、(c)的波形为 LVDS 接收端正负端信号,(d)、(e)、(f)的波形为接收端的差分信号(正端与负端的电压差)。主要观察(d)、(e)、(f)的波形,因为 LVDS接收器是通过检测正负接收端电压的差值来判决的。图 4(a)、(d)为ADCLK,其频率为 65 MHz,图 4(b)、(e)为 LCLK,其频率为 390 MHz,图 4(c)、(f)为数据线,数据速率为 650 MHz。(a)、(b)、(c)中示波 器横轴刻度 为 5 ns/div,(d)、(e)、(f)中示波器横轴刻度为1 ns/div。由仿真结果可知,使用差分信号线有效抑制了共模干扰,时钟线上波形在边沿处的单调性很好,较平滑,没有出现因反射而引起的锯齿状抖动。数据线上频率较高为650 MHz,波形也很平滑,没有出现因反射而引起的锯齿状抖动。

4.2.2 串扰分析

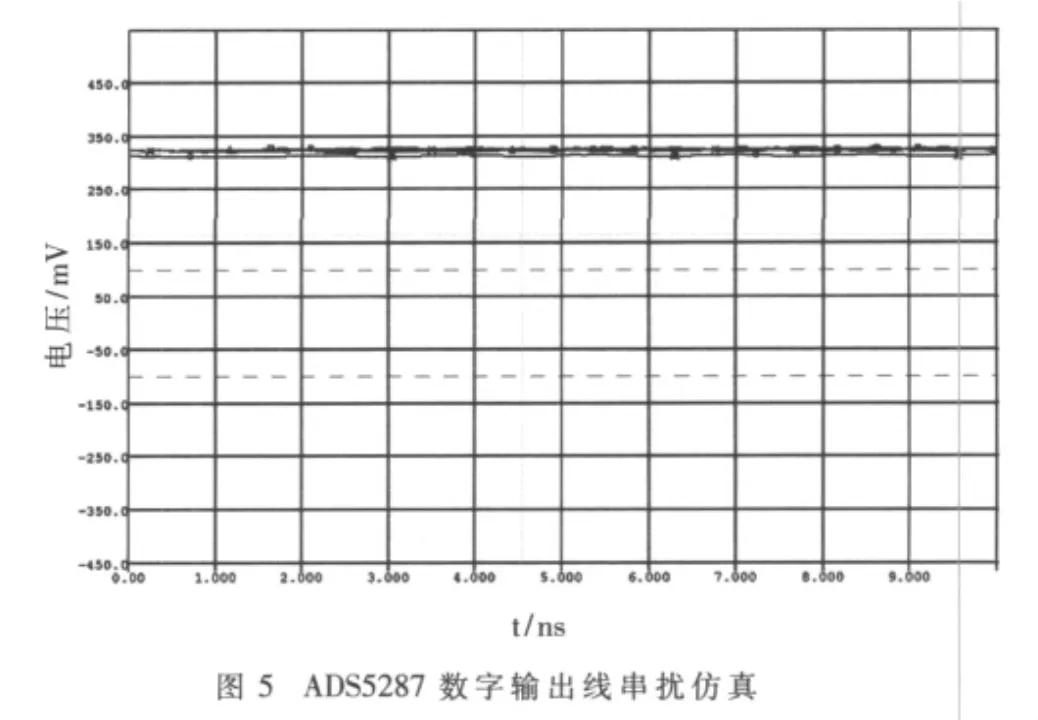

因为ADS5287的数据输出频率较高,而各通道的数据线彼此靠得很近,故有必要对这些线进行串扰分析。在Boardsim中对所有可能受到攻击的ADS5287的输出数据线和时钟线进行了串扰分析,结果如图5所示。图中虚线为接收端高低电平判决门限。实线为各接收端接收高电平时,叠加的串扰。由图5可知,结果中最大的串扰峰峰值为25 mV,叠加了串扰的高电平信号仍然远远高于高电平判决门限电平。从该分析可看出,利用LVDS电平标准来进行高速数据传输,能有效抑制信号线间的串扰。首先,作为攻击者,差分线上的电流大小相等,方向相反,差分线又彼此靠近,对外的干扰可相互抵消。其次,作为被干扰者,差分线由于彼此靠近,受到的干扰相同,差分信号中干扰被抵消。

本文介绍了TI公司的ADS5287模数转换器的结构、原理以及应用电路设计。并结合Altera公司的CycloneⅢ系列的FPGA芯片EP3C120F780C7N,设计了支持8通道的MIMO中频接收机的电路。对设计完成后的PCB中的重要高速信号线进行了信号完整性仿真。

[1]Texas Instruments.10 bit,Octal-channel ADC up to 65 MS/s[Z].2008.

[2]Texas Instruments.Five/Ten output clock generator/jitter cleaner with integrated dual VCOs[Z].2010.

[3]Altera.CycloneⅢdevice handbook[Z].2010.

[4]Altera.CycloneⅢdevice handbook[Z].2010.

[5]Analog Devices.Aperture uncertainty and ADC system performance[Z].1998.

[6]廖承恩.微波技术基础[M].西安:西安电子科技大学出版社.1994.

[7]STEPHEN H,GARRETT W,JAMES A.High-speed digital system design.lnd ed[M].New York:John Wilwy&Sons,2000.

[8]张海风.HyperLynx仿真PCB设计[M].北京:机械工业出版社.2005.