高速串行RapidIO总线背板信号完整性仿真研究

李 彦, 吴培明, 寇小明

高速串行RapidIO总线背板信号完整性仿真研究

李 彦, 吴培明, 寇小明

(中国船舶重工集团公司 第705研究所, 陕西 西安, 710075)

信号完整性(SI)是高速电路设计面临的一个主要问题。对109Hz以上高速信号的信号完整性问题从原理上进行了详细分析, 并针对损耗、串扰、反射等因素提出了改善信号完整性的方法。在高速串行RapidIO总线背板的设计中, 探索出一套利用HyperLynx工具进行仿真分析和设计验证的方法, 即利用前仿真工具LineSim对影响信号完整性的主要参数进行评估, 形成设计指导数据; 利用后仿真工具BoardSim对布线后的高速背板进行验证, 从理论上证明了高速串行RapidIO总线背板的设计是可行的。

信号完整性; 高速串行RapidIO总线; 背板; HyperLynx

0 引言

信号完整性(signal integrity, SI)是指信号在信号线上的质量, 良好的信号完整性是指在需要时, 信号仍能以正确的时序和电压电平值做出响应, 反之, 当信号不能正常响应时, 就出现了信号完整性问题。

RapidIO串行总线协议传输速率达到了3.125 ~6 Gb/s, 分布参数显现出不可忽视的影响。因此, 一些在低速率场合下被忽视的因素现在会导致越来越多的信号完整性问题, 成为制约进一步提高串行总线传输速率的瓶颈。

为解决串行RapidIO总线信号完整性问题, 保证良好的板级性能并提高设计效率, 本文探索了使用HyperLynx软件对3.125 Gb/s的高速串行总线传输通道进行仿真分析和设计验证的技术。

1 高速串行RapidIO总线背板信号完整性问题

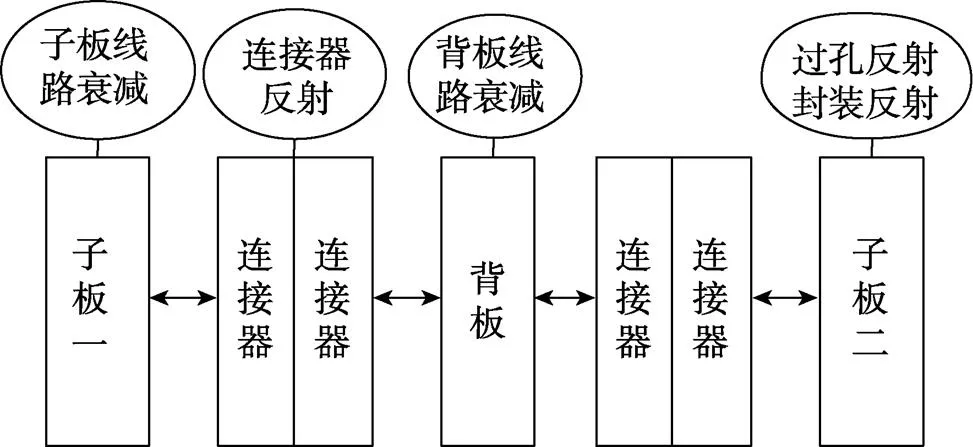

现代电子设备中, 各功能板卡之间的互连往往通过背板来实现(见图1), 这使得背板成为高速串行信号链路最复杂的情况之一。

图1 背板与子卡连接示意图

在速率为GHz量级的高速串行数据的传输中, 损耗、串扰和反射是信号完整性面临的主要问题。

1.1 损耗

损耗不仅降低信号能量, 而且会减慢信号的边缘速度, 进而导致信号发散和降低抖动容限, 形成码间干扰(inter symbolic impact, ISI)。而ISI是削弱高速串行信号在链路传输性能的最严重干扰。

对于GHz量级的高速串行信号的损耗主要来自2个方面,一是导线电阻和趋肤效应引起的损耗; 二是介质损耗, 如图2所示。

图2 介质损耗随频率变化曲线

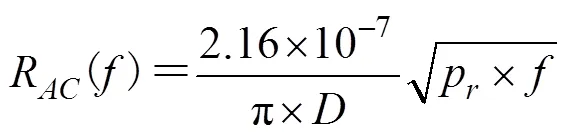

由于趋肤效应的影响, 电流在高频时将重新分布, 互连通道有效截面积随着速率上升而减小,信号和回路导体的串联电阻R会与频率的平方根成正比、与走线的直径成反比增长, 如式(1)所示, 导致信号传输回路的传输损耗增大[1]。

式中:为走线直径;为频率;p为相对铜的电阻率。

由于频率的相关性, 在较高频率上, 介质损耗开始在总损耗中占主导地位。从图2可以看出, 在GHz量级情况下, 介质损耗上升到阻抗损耗的3.5倍左右。

因此, 在高频场合下, 增大走线直径, 使用低介电常数的介质材料是减少损耗的有效手段。

1.2 串扰

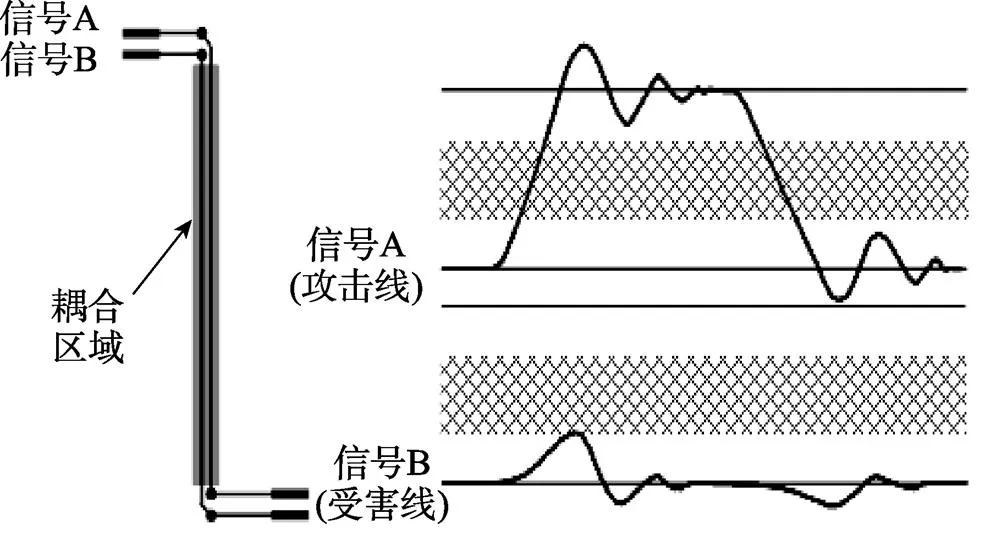

串扰是指某一回路中的电流或电压在邻近回路产生了电流或电压, 从而影响了该邻近回路的正常工作。串扰量与传输线间距成反比, 与通道间并行长度成正比, 是产生抖动并使波形失真的重要原因。

在高速背板系统中, 由于布线通路的限制, 有大量信号高密度、长线并行传输, 它们之间的耦合会产生两方面的影响。首先, 串扰会改变总线中受串扰的传输线的特性, 即等价地改变传输线的特性阻抗与传输速度, 这样会对系统的时序和信号完整性带来不利影响。另外, 串扰会对其他传输线造成噪声, 这样会进一步降低信号质量, 以及降低信号的噪声余量。如图3所示。

图3 两平行走线间信号串扰

最常见的对抗串扰的方法是在印刷电路板(printed circuit board, PCB)布线中遵循3W原则[2]。另外, 尽量拉大传输线间的距离, 减少相邻传输线间平行走线的长度, 改单端传输线为差分传输线, 相邻信号层垂直走线, 使用参考平面包夹信号层都是减少串扰的有效手段。

1.3 反射

信号的反射和多次反射是由于阻抗不连续造成的, 它迭加在串行信号的后续码流上, 使信号畸变和失真。反射系数由确定点的反射电压同输入电压的比决定, 这个点定义为传输线上的阻抗不连续点[3]。

式中:0为传输线特性阻抗;Z为不连续的阻抗。

高速背板串行链路的阻抗不连续[4]往往是PCB上差分走线因生产工艺和线宽引起的阻抗变化, 连接器的插接针和过孔的阻抗变化等反射因素导致的。因此, 在高速背板设计和加工时, 需要严格进行阻抗匹配设计(如减少使用过孔和等线宽控制, 并选用具有阻抗控制的连接器), 保证信号链路阻抗连续。

2 仿真试验

为了对上述SI措施进行验证, 设计了高速串行RapidIO总线背板电路进行仿真试验。

2.1 仿真电路的设计

在串行RapidIO总线背板电路原理图设计完成之后, 需要为电路元器件选定IBIS模型并确定仿真需要其他参数(如激励源、PCB叠层顺序及厚度等)。

1) 该电背板仿真电路使用Tyco公司的Multi Gig RT-2高速串行RapidIO连接器, 它具有阻抗控制和屏蔽保护功能。设定PCB板层数为8, 信号层与参考地层交叉分布。设定前仿真传输线长100 mm。使用“Simple-Diff”模型为激励源。

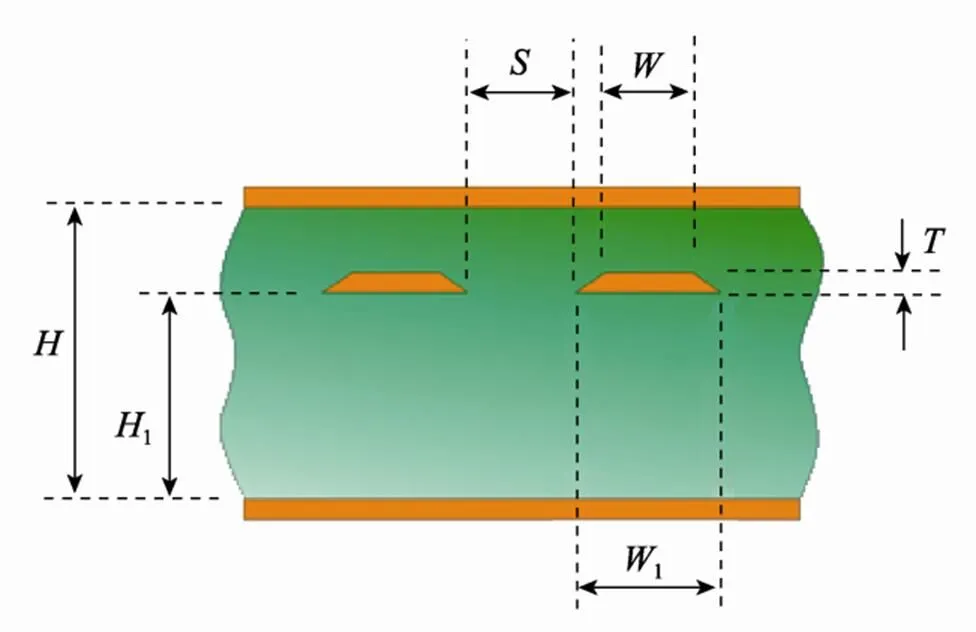

2) 所有高速串行差分信号线布线采用偏置的边缘耦合带状线方式(见图4), 间距恒定, 拐角度数相等(135°), 差分线长公差0.127 mm, 优先满足线长匹配。信号线在同一板层中完成点到点的走线, 避免在层间切换。在信号线相邻的层用参考地层进行屏蔽, 地层保持连续。

图4 偏置的边缘耦合带状线

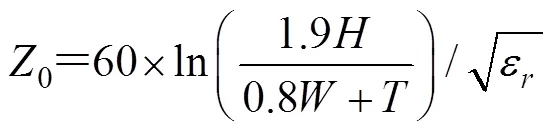

3) 传输线采用低电压差分信号(low voltage differential signal, LVDS), 要求差分阻抗diff= 100W±10%, 特征阻抗0=55W±10%。将设定的参数,1,,,和(设定1=)带入式(4)和式(5)(参数意义如图4所示), 计算diff和0。

同时, 利用HyperLynx仿真工具计算获得不同线间距的2组diff和0数值。3组数据见表1所示, 它们都满足设计要求。仿真值2获得数据最接近要求, 但是由于其要求的线间距大, 布板时不易满足。因此选择仿真值1所设定的参数作为设计参考。

表1 Z0, Zdiff理论值和仿真值

2.2 仿真试验

以传播速率为3.125 Gb/s, 长度为31bit的伪随机码序列作为仿真序列, 循环10次, 插入1%的高斯随机扰动, 分别进行仿真试验[5]。

2.2.1 前仿真试验

根据叠层安排和耦合关系的设置, 在Hyper Lynx中建立的串行链路Spice模型仿真电路, 如图5所示。

设定U1-U2链路为“攻击线”, U3-U4链路为“受害线”。从U1和U3端注入信号, U2和U4端差分信号眼图前仿真结果如图6所示, 图中,UI为单位时间间隔。

2.2.2 后仿真试验

从PCB布线中选取长度最大(92.9 mm), 走线环境最为复杂的一对差分信号进行仿真, 如图7所示。

图5 串行链路Spice模型仿真电路图

图6 前仿真眼图(TUI=320 ps)

图7 选取待分析的高速走线

图8是提取布线后的拓扑图, 从图中可以看出, 每条传输线按照耦合区域, 被分成若干小段传输线, 其特征阻抗均为51.8W。根据叠层分布和注入信号得到如图9所示的后仿真眼图。

图8 布线后的拓扑图

图9 后仿真眼图(TUI=320 ps)

2.2.3 试验结论

按照S-RapidIO物理层对接收端眼图参数的要求, 将眼图掩模的高度设为200 mV, 过零区边界位置为0.275, 有效数据窗口起始点为0.400。由上图可以得出以下结论。

1) 眼图对称, 眼线较细, 高低电平都比较光滑, 眼图掩模可以完全包围在眼图之中。说明根据规定参数进行的仿真获得了成功。

2) 后仿真的眼图质量比前仿真眼图质量要好, 是因为后仿真是无源背板单板仿真, 无法加入连接器模型, 减少了损耗和干扰。后仿真眼图说明背板高速信号的布线满足设计要求。

3 结束语

在封装和互连对于信号不再是畅通和透明的今天, 采用立足于可预见性的新设计方法越来越重要。利用仿真工具对高速电路的信号完整性设计进行仿真分析和验证可以获得各种直观的边界条件, 为设计提供了有效的支持, 将会大大提高设计效率和成功率。

[1] Stojanovic V. Channel-Limited High-Speed Links Modeling Analysis and Design[D]. Stanford University, 2004.

[2] Johnson H, Graham M. 高速数字设计[M]. 北京: 电子工业出版社, 2004.

[3] 顾海洲, 马双武. PCB电磁兼容技术—设计实践[M]. 北京: 清华大学出版社, 2004.

[4] Bogatin E. 信号完整性分析[M]. 北京: 电子工业出版社, 2005.

[5] Mentor Graphics. High-Speed Design Workshop[M]. USA: Mentor Graphics, 2009.

Signal Integrity SimulationofHigh Speed Serial RapidIO Bus Backboard

LIYan, WU Pei-ming, KOU Xiao-ming

(The 705 Research Institute, China Shipbuilding Industry Corporation, Xi′an 710075, China)

Signal integrity (SI) is a key problem in design of high speed bus. In this paper, the SI of high speed bus signal above 109Hz is analyzed, and ways to improve SI are put forward with respect to the influences of loss, crosstalk and reflection on SI. In the design of the high speed backboard, with the help of HyperLynx, a method for simulation and validation is proposed, in which LineSim is adopted to evaluate the main parameters affecting SI and achieve guiding data for design, and BoardSim is also adopted to validate the designed high speed backboard. The feasibility of the designed high speed serial rapidIO bus backboard is theoretically proved.

signal integrity(SI); high speed serial rapidIO bus; backboard; HyperLynx

TJ630.6

A

1673-1948(2011)03-0167-05

2010-07-01;

2010-08-24.

李 彦(1980-), 男, 硕士, 主要从事计算机硬件方面研究与设计.

(责任编辑: 陈 曦)

—— 晶体硅太阳电池研究进展(10)