基于DDS技术的电磁阀检测平台的设计

丁 磊,周凤星

(武汉科技大学 故障诊断及检测实验室,湖北 武汉 430081)

汽车电磁阀在汽车工业生产中需求量极大,模拟电磁阀工作环境,从而检测出其质量的优劣值得关注研究。笔者设计的电磁阀检测平台是基于DDS技术与单片机相结合,同时运用CPLD技术,模拟出电磁阀在工作期间的相关参数环境,从而判断电磁阀的好坏。

本设计采用直接数字合成(DDS)[1]技术,采用专用集成芯片AD9834作为三角波产生模块,利用51单片机和CPLD[2]来控制完成整个系统的设计。该系统输出的三角波低频特性好并且可以模拟斜坡信号,能产生可调占空比的方波信号,可调范围达1%~99%。

1 系统设计方案

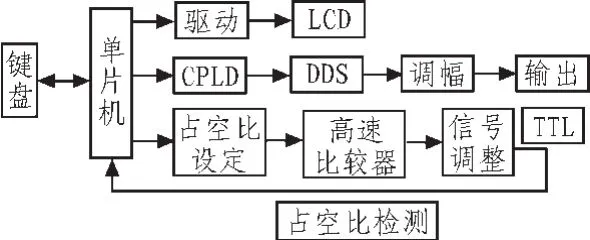

本文设计的数字信号源的系统框架如图1所示。

图1 系统框架Fig.1 System framework

本系统产生输出频率为0~25 kHz,最小精度为1 Hz的信号,占空比在0~100%范围内可调,变化周期为10 s的整数倍。系统输出电压VOUT范围0~40 V,最小精度0.01 V,输出电流最大可达10 A,方波低电压可调范围0~10 V,并且波形较好,可以连续变化,误差不超过1%。

单片机完成键盘扫描和按键处理,通过SPI总线对AD9831进行控制处理,通过AD7541进行采样处理。系统中的CPLD完成对单片机的扩展和测频功能。单片机发出的指令通过CPLD控制DDS以完成信号的产生。

2 模块电路设计

2.1 控制系统

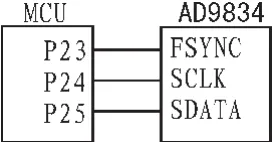

单片机控制整个系统工作,采用 12 MHz晶振,P1.0、P1.1、P1.2、P1.3、P1.4、P1.5 接一块 3×3 矩阵键盘 ,P0 口为扩展接口,连接一块8255芯片扩展端口,并且同时连接LCD的DB0、DB1、DB2、DB3、DB4、DB5、DB6、DB7 数 据 控 制 端 口 。P2.3、P2.4、P2.5 分 别 接 AD9834 的 FSYNC、SCLK、SDATA 端口。单片机各种数据和命令通过CPLD送出。

单片机向CPLD写数据时,读信号都一直置低电平,写信号口在上升沿时,CPLD开始读地址,写信号口在下降沿时,CPLD开始读数据;单片机从CPLD读数据时,将读信号口一直置低电平,读信号口在上升沿时,单片机开始读地址,写信号口在下降沿时,单片机开始读数据。时序图如图2所示。

图2 单片机读取数据Fig.2 Reading the data by Microcontroller

2.2 DDS信号产生单元

DDS原理:直接数字频率合成器 (Direct Digital Synthesizer)[3]是从相位概念出发直接合成所需波形的一种频率合成技术,一个直接数字频率合成器由相位累加器、加法器、波形存储ROM、D/A转换器和低通滤波器 (LPF)构成。DDS框架图如图3所示。

图3 DDS信号发生原理图Fig.3 Schematic diagram of DDS signal happening

其中K为频率控制字,P为相位控制字,W为波形控制字,fc为参考时钟频率,N为相位累加器的字长,D为ROM数据位及D/A转换器的字长。相位累加器在时钟fc的控制下以步长K作累加,输出的N位二进制码与相位控制字P波形控制字W相加后作为波形ROM的地址,对波形ROM进行寻址,波形ROM输出D位的幅度码S(n)经D/A转换器变成阶梯波S(t),再经过低通滤波器平滑后就可以得到合成的信号波形。合成的信号波形形状取决于波形ROM中存放大幅度码,因此用DDS可以产生任意波形。使用50 MHz的晶振理论上DDS可以产生15 MHz左右的失真度小于1%的正弦信号[4],信噪比可以达到60 dB,信号的输出频率可以表示为:

f0=(fc/2n)×M

fC为DDS时钟频率;N为相位累加器位数;M为相位累加器步长;f0为输出频率。

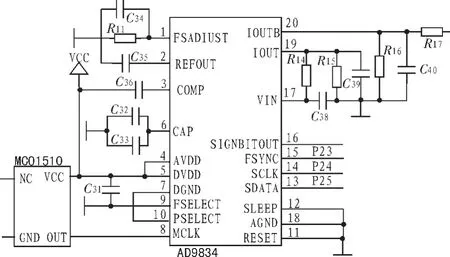

DDS与单片机的连接方式以及自身外围电路如图4,图5所示。

图4 单片机与DDS连接图Fig.4 Connection diagram between microcontroller and DDS

DDS9834驱动程序模块如下:

void write_word(uint word)

{

uchar i=0;

SCLK=1;

图5 DDS外围电路Fig.5 DDS peripheral circuit

FSYNC=0;

for(i=0; i<16; i++)

{

if(word&0x8000)

SDATA=1;

else

SDATA=0;

SCLK=0;

SCLK=1;

word<<=1;

}

FSYNC=1;

}

ulong send_fre(ulong freq)

{

ulong water;

water=268435456.0*freq/30000000;

return(water);

}

void set_freq(ulong Freq_value)

{

ulong value1,value2;

uint LSB_D,MSB_D;

value1=Freq_value;

value2=Freq_value;

LSB_D=(value1%0x4000)+0x4000;

MSB_D=(value2/0x4000)+0x4000;

“Fish vie to swim upstream, in early summer less rain.

write_word(LSB_D);

write_word(MSB_D);

}

void AD9834(uint freq2)

{

uint j,freq3;

freq3=freq2;

FSYNC=1;

SDATA=0;

write_word(0x21C2);

set_freq(send_fre(freq3));

write_word(0xC000);

write_word(0x2002);

for(j=0;j<100;j++) ;

SCLK=1;

FSYNC=1;

SDATA=0;

}

2.3 模块控制单元(CPLD)

复杂可编程逻辑器件CPLD(Complex Programmable Logic Device)[5],是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围,是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。本系统中,采用Altera公司的EPM3128[6]来连接单片机和DDS,单片机发出的指令通过CPLD来控制DDS芯片,同时检测频率为0~25 kHz的信号,检测误差小于 0.1%[7]。

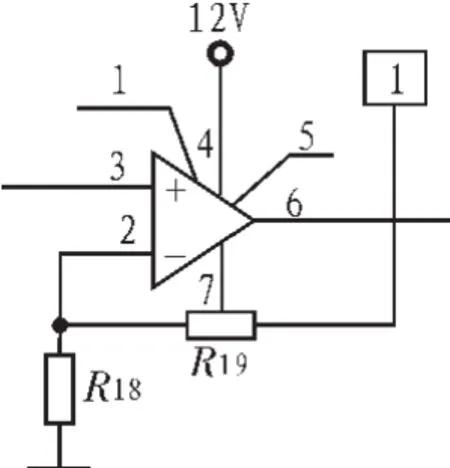

2.4 信号调理单元

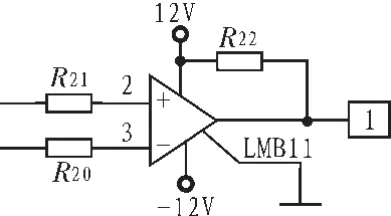

使用DDS9834所提供的互补输出信号IOUTB、IOUT,从IOUTB输出的信号是微弱的三角波电流信号,图6中端口3接AD9834的IOUTB,将输出三角波信号放大,图7的端口2接图6的端口6,图7的端口3接AD7541输出的平稳电压,经过比较,得出平稳的方波[8-9]。

图6 放大电路Fig.6 Amplifying circuit

图7 比较电路Fig.7 Comparative circuit

3 系统软件设计方案

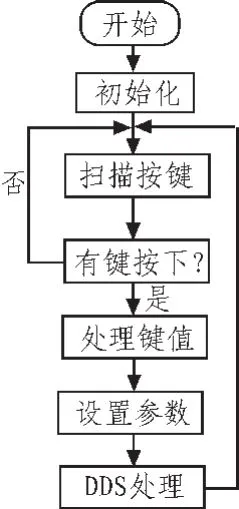

单片机采用C语言编程,在执行指令之前首先要完成各种初始化工作。其中包括时钟初始化、端口设置、看门狗设置、开机初始化,尤其注意对DDS9834的初始化驱动程序的设置,然后等待中断,进入键盘扫描和各种按键的处理程序[10],整体流程如图8所示。

4 结束语

直接数字频率合成(DDS)是DDS信号发生器的核心部分。本检测平台以单片机为核心,采用DDS技术实现了一种新型的低频特性好并且可以模拟的斜坡信号,可以产生可调占空比的方波信号,可调范围达1%~99%。经过测试,该检测系统平台可以实现信号源工作稳定,并且操作方便,成本低,通过样机的研制,测试效果较好,精度较高。

图8 系统流程图Fig.8 Flow chart of system

[1]Kolen P T.Self-calibration compensation technique for microcontroller-based sensor arrays[J].IEEE Transactions On Instrumentation and Measurement.1994,43(4):620-623.

[2]Ahuja V.Analyses of transient event in complex value and feed systems[J].AIAA,2005:45-49.

[3]刘建成,邹应全,行鸿彦.基于DDS9834函数发生器的设计[J].元器件与应用,2007(2):8-10.LIU Jian-cheng,ZOU Ying-quan,HANG Hong-yan.Based on the design of DDS9834 function generator[J].Components and application,2007(2):8-10.

[4]徐伟,周杏鹏.基于AD9834的高性价比型号发生器的设计[J].仪器仪表与分析检测,2008(1):6-8.XUWei,ZHOUXing-peng.BasedonAD9834highperformanceto-price ratio model generator design[J].Instrumentation and Assay,2008(1):6-8.

[5]徐正平,翟林培,田雅男,等.基于DDS技术的高频正弦波信号发生器的设计[J].单片机开发与应用,2009(2):69-76.XU Zheng-ping,QU Lin-pei,TIAN Ya-nan,et al.Design of high frequency sine signal generator based on DDS[J].SCM Development and Application,2009(2):69-76.

[6]周鹏.基于AD9851的多功能信号发生器的设计[J].电子元器件应用,2009(9):8-14.ZHOU Peng,AD9851 multifunctional signal generator based on the design[J].Electronic Components Application,2009(9):8-14.

[7]李季.信号发生器发展浅析[J].电子产品世界,2004,34(4):65-67.LI Ji.Signal generator development analysed[J].Electronics World,2004,34(4):65-67.

[8]郑毅.一种高精度直接数字式频率源的研制[D].武汉:武汉理工大学,2001.

[9]李凯.基于DDS技术的函数发生器设计与实现[J].电脑知识与技术,2009,5(9):2515-2517.LI Kai.Based on DDS technology function generator design and implementation[J].Computer Knowledge and Technology,2009,5(9):2515-2517.