基于DDS的励磁恒流源设计

马仔悦,王京梅,孙 俊,李 莉

(电子科技大学微电子与固体电子学院,四川成都 610054)

随着信息技术的发展,磁性材料广泛运用于通信、电力、信息、交通等领域中。磁滞回线是磁性材料中重要的磁性参数之一,是铁磁材料的本质特征。通常运用于与磁性材料有关的计算和研究中,对工业生产和科学研究具有重要的指导意义。材料的磁滞回线通过B-H测试仪可以测量得到,测试仪以电磁感应原理为基础,通过励磁电源对软磁材料样品的初级绕组加一定频率和幅度的电流,次级绕组两端将会产生感应电动势,对初级励磁电流和次级感应电动势实施同步实时采样。根据安培环路定理和电磁感应定理计算磁场强度H和磁感应强度B,进而可以计算动态回线,动态磁化曲线、铁损、动态磁导率等参数。励磁信号源主要包括正弦信号发生电路和功放电路两部分。目前励磁电源信号发生部分通常采用直接频率合成技术,主要功能电路由压控振荡器(VCO)、倍频器、分频器、混频器和滤波器等构成,整个系统采用开环控制,即输入设定值→频率合成→功率放大→输出励磁电流[1]。这种结构给励磁电源带来以下不足:(1)由于采用外部压控振荡器,励磁信号的频率范围受到限制,一般约为50 kHz。(2)系统使用开环控制,系统精度依赖于各组件的精度和稳定性,使得励磁电流的幅度精度和稳定性较差,仪器抗干扰性不强。(3)采用直接频率合成技术,系统中有大量模拟电路,导致系统体积大、重量大、耗电高、可靠性差。

为此,文中提出一种基于FPGA的DDS信号发生器。信号发生电路采用直接数字频率合成技术,即DDS(Direct Digital Frequency Synthesis)。它是以全数字技术,从相位概念出发,直接合成所需波形的一种新的频率合成技术。是将先进的数字处理技术和方法引入信号合成领域,把一系列数字量形式的信号通过数/模转换器转换成模拟信号,在时域中进行频率合成。直接数字频率合成器的主要优点是:输出信号频率相对带宽较宽;频率分辨力好、转换时间快;频率变化时相位保持连续;集成度高,体积小,控制方便等。整个信号源系统采用数字闭环控制,通过对励磁电流瞬时值经PID闭环控制,使得励磁电流可瞬时跟踪给定幅值,加快系统动态响应,提高非线性负载适应力,其较传统的信号源能更好地满足磁性测试设备的需求。

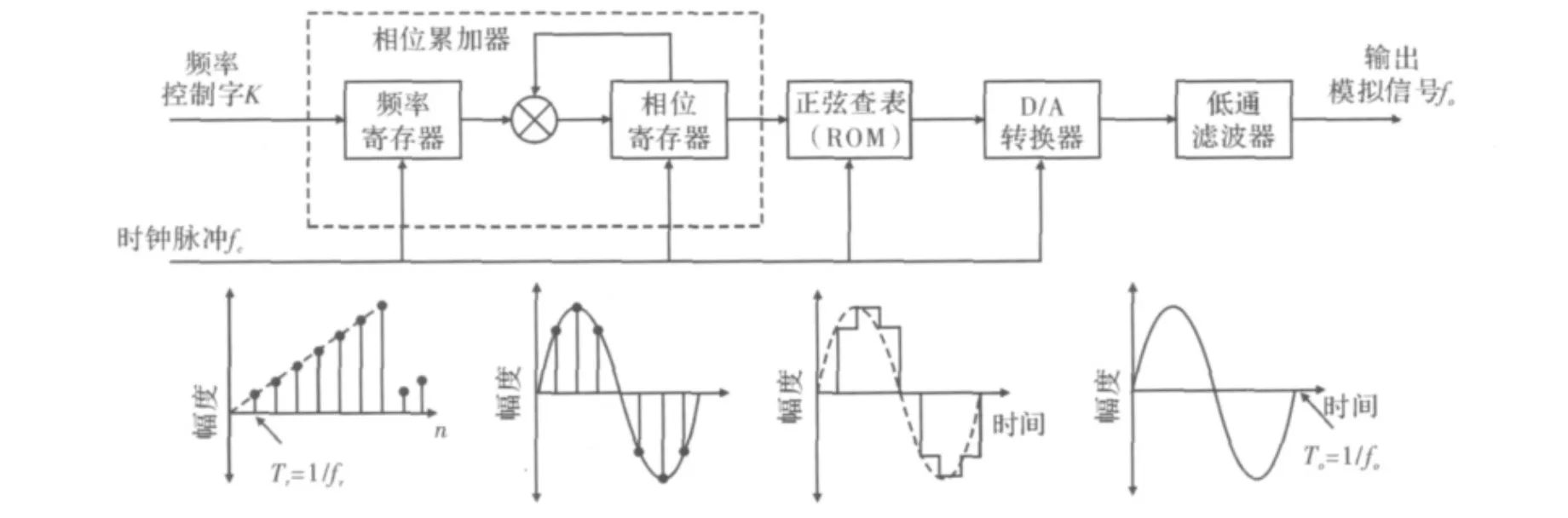

1 DDS的工作原理

DDS的工作原理如图1所示。主要有以下基本部件:相位累加器;相位-幅度变换器,即正弦查表ROM;D/A转换器和适当的滤波器等滤波器[2]。相位累加器是DDS系统的核心是相位累加器,它由一个加法器和一个相位寄存器组成,相位累加器在参考时钟的作用下,按频率控制字为步长不断累积,累加结果产生递增的传递给正弦查表ROM。正弦查询表中存储了一个周期正弦波在各相位点对应数字幅度信息。由于相位累加器的输出连接在波形存储器(ROM)的地址线上,因此其输出的改变就相当于进行查表。这样就可把存储在波形存储器内的波形抽样值经查找表查出,然后送至D/A转换器,经D/A转换器产生一系列以时钟脉冲为抽样速率的电压阶跃。滤波器则进一步平滑D/A转换器输出的近似正弦波的锯齿阶梯波,同时衰减不必要的杂散信号,使输出为要求的光滑波形。

图1 DDS工作原理框图

由于相位累加器字长的限制,相位累加器累加到一定值后,其输出将会溢出,这样波形存储器的地址就会循环一次,即意味着输出波形循环一周。故当频率字取不同值,就可以改变相位累加器的溢出时间,从而在时钟频率不变的条件下改变输出频率[3]。

设频率控制字为K,系统参考时钟为fc,相位累加器位数为N,输出频率为fo,则可以得到输入与输出的关系为

当K=1时,可以得到DDS的频率分辨率

2 励磁恒流源的硬件设计

励磁信号发生器电路系统主要由基于FPGA的DDS电路、MCU控制电路、DAC电路、低通滤波器(LPF)、人机接口、系统时钟和系统电源构成。系统框图,如图2所示。

图2 系统电路框图

2.1 基于FPGA的DDS电路

2.1.1 相位累加器

对于利用FPGA设计DDS信号源,相位累加器是决定DDS电路性能的一个关键部分。相位累加器是由N位累加器和N位寄存器级联构成,每来一个时钟脉冲,相位寄存器采样上个时钟周期内相位累加器的值与频率控制字K之和,并作为相位累加器在这一时钟周期的输出。由式(2)可知,相位累加器的位数N越大,得到的频率分辨率越小,但在较高的工作频率下,会产生较大的延时不能满足速度的要求[4]。在时序电路中,通常采用流水线技术来提高速度,代价是增加寄存器的数量,多占了FPGA的资料。综合考虑,采用32位累加器,四级流水线结构[5]。

2.1.2 相位-幅度变换器

相位-幅度变换器是由ROM构成,它把相位累加器的输出的数字相位信息变换成正弦波值。在FPGA中,ROM一般是由EAB来实现,并且ROM表的尺寸与地址位数或数据位数成指数增加的关系,因此相位-幅度转换器的设计是影响DDS性能的另一个关键,在满足信号设计指标要求的前提下,主要在于减少资源开销。考虑到本设计只需要输出正弦信号,正弦波信号关于点(π,0)奇对称,只需存储1/2周期的波形数据,又根据在左半周期内,波形关于直线x=π/2成偶对称,因此只需要存储1/4周期的正弦函数值,就可以通过适当的变换得到整个正弦码表,这样可以节约3/4的资源。

2.2 低通滤波模块

DDS有一个明显的缺点,即输出频率越接近Nyquist带宽的高端,采样点数越少,其输出的杂散干扰就越大。输出波形具有大量的谐波分量和系统时钟干扰。为得到所需频段内的信号,需要在DDS输出端加一滤波器来实现,而低通滤波器能较好地滤除杂波,平滑信号,所以低通滤波器的设计尤为重要,滤波特性的优劣对输出信号的性能起重要的影响[6]。

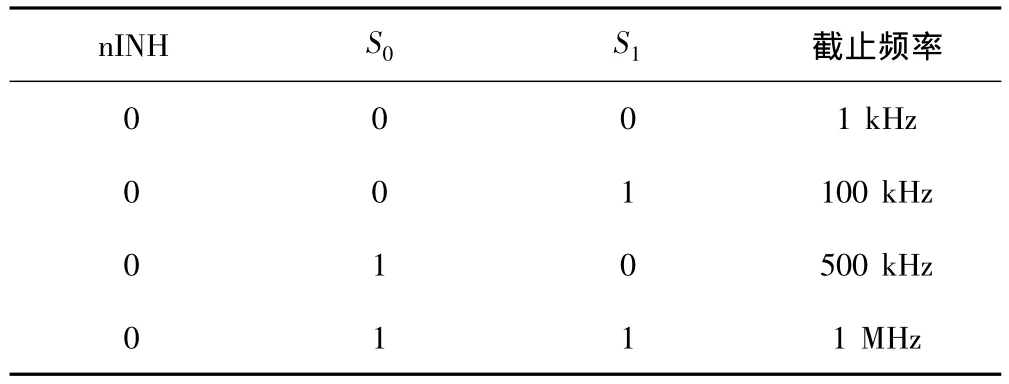

为取得较好的滤波效果,滤波器采用了由四选一模拟开关和精密运算放大器分段滤波的方式:采用巴特沃斯有源低通滤波器,该滤波器通带内幅度很平坦,滤波电路为二阶巴特沃斯低通滤波电路,滤波器频段参数的选择由FPGA输出的控制信号nINH,S0,S1控制模拟开关的选通实现。

表1 控制信号与截止频率

2.3 幅度控制

本设计幅度控制电路采用调节DAC参考电压的数字化控制方法,采用两个D/A级联的方式,数模转换器DAC2采用外部可变基准源,通过改变基准源的值来改变输出的满幅度电流值,该可变基准源通过DAC1产生。DAC1的基准电压采用输出电压为1.25 V精密电压基准芯片提供,设DAC1的幅度输出字为N1,则DAC1的参考电压为

设DAC2的数字输入字为N2,则经电流/电压转换后的输出电压为

2.4 人机交互

为方便快捷地控制DDS的频率字输入和幅度控制,本设计采用单片机来实现对DDS信号发生器的控制。DDS的频率字和幅度数据字位较多,而单片机输出端口位数有限,所以单片机与FPGA之间的通信采用SPI(Serial Peripheral Interface,串行外设接口)方式,单片机将控制命令字传送给FPGA。同时,为了输入控制方便,添加了键盘和显示系统。

3 数字闭环控制系统的实现

设计的励磁恒流源主要为磁性测量仪器提供激励电源,因而对其精度和稳定性要求高,采用电流控制型的控制策略进行闭环控制,结构框图如图3所示。

图3 闭环控制系统框图

励磁电流幅度调整时,首先对励磁电流进行多周期采样,然后计算其有效值,并与输入设定值相比较,若误差ε在允许范围之外,则根据误差的实际情况,通过单片机内增量式PID算法得出了一个新的控制量,传送给FPGA控制幅度调节经低通滤波器滤去高频成分,再经功率放大,得到高精度的励磁电流。

4 系统仿真与验证分析

在Altera公司的QuartusⅡ环境下编译完成,采用自上而下的设计方法,即先从系统总体要求出发将设计内容细化,最后完成系统硬件的整体设计。完成DDS设计后,通过编写Testbench在Modelsim进行仿真。在QuartusⅡ中,设定输出信号频率为1 MHz,经过50 μs后改变为500 kHz进行仿真,其仿真结果如图4所示。在Modelsim中生成的仿真数据经验证完全正确,满足设计需求。

图4 DDS仿真结果

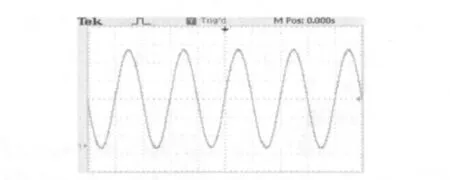

在对励磁信号源做硬件系统测试时,首先完成系统硬件连接,并加载程序,设定输出信号频率为1 MHz,示波器测得实际输出波形如图5所示。在Modelsim环境下仿真和在硬件平台上测试,结果表明励磁信号源可获得较好的设置波形,可以应用于磁性材料的测试中。

图5 实际输出波形

5 结束语

运用Verilog硬件编程语言结合DDS技术,利用FPGA器件强大的硬件功能,提高了系统集成度,实现了输出信号相对带宽宽、稳定性好;其相位累加器在一定系统时钟和累加器位宽条件,输出信号分辨率越小,频率控制字的传输时间以及器件响应时间都很短,使输出信号频率切换时间较短,可以达到ns级,且频率变化时,相位保持连续,系统采用闭环控制,励磁电流输出精度高,调节速度快。对磁性材料测量仪所要求的励磁信号源而言,本设计不但满足所有技术指标,而且集成度高、体积小、显著地降低了成本。

[1] 邓元,贺祥清.软磁铁氧体测量技术及标准进展[C].深圳:2003中国电子变压器第一届联合学术年会,2003.

[2] 白居宪.直接数字频率合成[M].西安:西安交通大学出版社,2007.

[3] 华清远见嵌入式培训中心.FPGA应用开发入门与典型实例[M].北京:人民邮电出版社,2008.

[4] 江志浩,孙明珠,蔡德荣.高精度DDS的FPGA优化设计[J].微计算机信息,2009,25(1-2):191-192.

[5] 李航,曲永志,雷霆.基于FPGA的涡流检测正交信号源的设计方法[J].计算机测量与控制,2008,16(10):1496-1498.

[6] 于淑萍,张幸儿.基于FPGA/MCU多功能信号发生器的设计与实现[J].电力自动化设备,2009,29(12):106-108.