高速PCB设计经验与体会

齐志强

(中国空空导弹研究院河南洛阳471009)

随着数字化技术的飞速发展,高速模数转换器和超大规模集成电路等器件的广泛应用,高速PCB设计已成为数字系统设计中的主流技术,一个高速系统能否正常工作很大程度上取决于PCB的设计。高速PCB设计是一项工程性很强的复杂技术,它不仅要求设计人员具有扎实的电路理论基础,还要有丰富的实践经验。高速PCB设计规则很多,纷繁复杂的设计规则有时还会互相冲突,这就要靠设计人员依据实践经验根据具体情况来选择,初入门者遇到此类问题往往无所适从。笔者依据多年的实践经验,对设计中需要重点注意的设计规则进行了归纳和总结,希望能够对电路设计者有所帮助。

1 叠层设计

PCB设计一开始就需要确定电路板结构及叠层,电路板的尺寸和形状往往是已经确定的,而层数则需根据板上信号工作频率、印制板管脚密度、印制板制造成本、加工周期和可靠性要求等因素综合考虑。高频电路往往布线密度较大,采用多层板是降低干扰的有效手段,合理选择层数十分关键。资料显示,同种材料的4层板比双面板噪声低20 dB[1]。PCB层数与管脚密度的关系可参考表1。

层数确定后,需要进一步安排电源层、地层及信号层的排布,通常在电源层旁边安排一个完整的地层,电源层和地层间形成一个平板电容器,可以滤除300 MHz以上的干扰[2]。不同电源层在空间上要避免重叠,主要是为了减少不同电源之间的干扰,特别是一些电压相差很大的电源之间,电源平面的重叠问题一定要设法避免,难以避免时可考虑中间隔地层。叠层的设计既要考虑电磁兼容性,又要考虑信号是适合走带状线还是微带线,信号线的密度大小和电源种类的多少等问题,图1给出了六层板设计时不同叠层形式与电磁兼容性的优劣关系[3]。

表1 管脚密度与PCB板层数的关系对应表Tab.1 The corresponding between pin density and number of layers

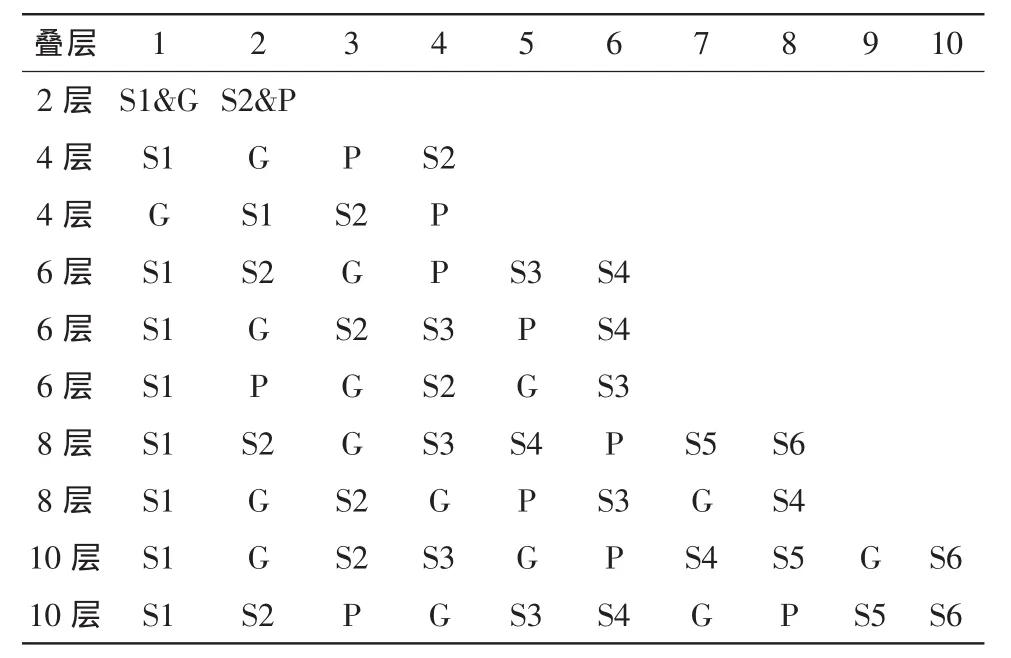

常用的叠层设计布局参考如表2所示。

图1 六层板叠层设计与电磁兼容性Fig.1 Relationship between six panels laminated design and the merits of the electromagnetic compatibiling

表2 叠层设计布局参考Tab.2 Design of nappe for PCB’s Placement

电源层和地层通常需要进行分割,同一平面层内不同信号层划分区域的间距最少要12 mil;电源层与地层之间的电场是变化的,在板的边缘会向外辐射电磁干扰,称为边沿效应。解决的办法是将电源层内缩,使得电场只在接地层的范围内传导。以一个H(电源和地之间的介质厚度)为单位,若内缩20 H则可以将70%的电场限制在接地层边沿内,内缩100 H则可以将98%的电场限制在内[4]。

2 布局

PCB按照电气性能可分为数字电路区、模拟电路区、电源转换区和功率驱动区等,完成同一功能的电路,应尽量靠近放置。数字电路具有较高的噪声容限,其本身抗干扰能力很强,同时又是一种很强的宽带骚扰源,放置时应尽量靠近接插件和电源,远离模拟器件。模拟器件抗干扰能力差,其灵敏度越高,带宽越大,抗干扰度越差,对外围电路的干扰也小,放置时主要考虑自身不被其他器件干扰。

PCB分区完成后,就可以按照主要信号流向放置器件,按照“先大后小,先难后易”的规则布局,电路中主要元器件和重要的单元电路优先布局。对质量大的器件应考虑安装位置和安装强度,发热元器件应均匀分散布局且与温度敏感元件分开放置,功耗大的器件还要考虑散热问题。BGA封装的元器件避免放置于PCB正中央,否则印制板发生形变容易使焊点脱焊,元器件与元器件之间、元器件与定位孔之间要留有适当的空间。每个集成电路块的附近应设置一个高频去耦电容,去耦电容应靠近芯片的电源管脚并使之与电源和地之间形成的回路最短,每个电解电容边上都要加一个小的高频旁路电容。两个滤波电容并联且距离较近时应方向相反放置。

3 接地

PCB设计中接地问题十分重要,理论表明:当干扰信号大于5 MHz时,一定来源于共模干扰,一定与地相关。地线大致分为系统地、机壳地、数字地和模拟地等。地线设计中应注意以下几点[5]:

1)正确选择单点接地和多点接地

信号工作频率小于1 MHz,采用单点接地;工作频率较高时地线阻抗变大,应采用多点接地。电路板上只有1个A/D器件时,采用桥接的接地方法,有多个A/D时一般采用统一地。

2)将数字电路和模拟电路分开

数字电路与模拟电路的地线分开并分别与电源端地线连接,尽量加大模拟电路的接地面积。

3)尽量加粗地线

若接地线细,接地电位将随电流的变化而变化,导致电子设备信号电平不稳,抗噪声性能变坏,地线宽度尽可能达到3 mm。

4)将地线构成闭合环路

将地线构成闭合环路可缩小电位差,明显提高抗噪声能力。对于导通孔密集的区域,要注意避免孔在电源和地层的挖空区域相互连接,形成对平面层的分割,从而破坏平面层的完整性,并进而导致信号线在地层的回路面积增大。

4 布线

布线是PCB设计的主要内容,布线的好坏直接影响到电路功能的实现和电路板性能的优劣。布线需要遵循的规则很多,这里只简要列出:

1)3-W原则:走线间距离间隔必须是单一走线宽度的三倍[6];

2)5/5规则:时钟频率超过5 MHz或上升时间小于5 ns时,需要使用多层板;

3)不能跨越分割间隙布线,否则地电流将会形成一个大的环路,电磁辐射和信号串扰都会急剧增加;

4)相邻层布线要相互垂直,平行容易产生寄生耦合;

5)走线尽量避免产生锐角和直角,以减小信号对外的辐射与耦合;

6)时钟、总线及片选信号要远离I/O线和接插件;

7)对噪声敏感的线不应与大电流,高速开关线平行;

8)高频电路器件引脚之间的引线要尽可能短,走线应尽量少换层;

9)减少高速电路器件引脚间引线的弯折,尽可能采用全直线;

10)对特别重要的信号线或局部单元实施地线包围的措施,对时钟等单元局部进行包地处理将对高速系统非常有益;

11)各类信号线不能形成环路,也不能形成电流环路;

12)I/O驱动电路尽量靠近PCB边缘;

13)时钟产生器尽量靠近使用该时钟的器件,石英晶体振荡器外壳应接地,下面不应走线;

14)为保证可靠性和PCB加工成品率,布线线宽不小于6 mil,线间距不小于6 mil;

15)布线时,尽可能减小环路面积,尽可能减少过孔的数量;

16)电容引线不能太长,尤其是高频旁路电容不能带引线;

17)避免信号返回线路共享共同路径;

18)信号线换层多的区域,需要适当地旁路电容构成较好的电流回路;

19)为避免产生“天线效应”,减少不必要的干扰辐射和接收,严禁出现浮空布线,否则可能带来不可预知的结果;

20)走线需要分枝,尽量控制分枝的长度;

21)尽量为关键信号(如时钟信号、高频信号、敏感信号等)提供专门的布线层,保证其回路面积最小,必要时应采取屏蔽和加大安全间距等方法来保证布线质量;

22)同一网络的布线宽度应保持一致,线宽的变化会造成线路特性阻抗的不均匀,当传输的速度较高时会产生反射,在设计中应该尽量避免这种情况;

23)对于电流强度较大的信号,布线时应适当增加线宽;

24)晶振、变压器、光耦、电源模块下不应有信号线穿过;

25)总的布线长度应尽量短,关键信号线(如高频时钟线,高频信号线)最短,高速线应短且直,关键线应尽量加粗,并在两侧加上保护地;

26)对高频信号设计而言,布线长度不得与其波长成整数倍关系,以免产生谐振现象。

5 其他设计规则

一个好的PCB设计并不只是考虑好布局、布线等与信号质量、电磁兼容等密切相关的地方就可以了,还需要考虑到PCB加工工艺可能带来的问题,焊接和测试问题等。

过孔的孔径与焊盘尺寸应做到合理匹配。两者匹配优选系列如表3所示,表中数据供设计人员参考。BGA处的过孔建议不做开窗,常规可以塞孔的孔径范围0.2~0.5 mm,过孔如果需要开窗上锡,则孔径不要小于0.25 mm,不建议使用盘中孔,过孔打在焊盘上,造成焊盘上不完整,焊料会从导通孔中流出,会造成焊膏量不足,对焊点的连接不可靠。

表3 焊盘孔径尺寸匹配优选表Tab.3 The preferred table of pad pore size matched pad hole guide size

丝印层元器件编号的字体、大小一致,丝印层信息不覆盖焊盘和过孔,极性元器件的丝印层上注明极性,排针等器件标明1号管脚,关键信号应预留测试点,以方便生产和维修检测。

6 结束语

按照本文所述方法设计的高速复杂数模混合电路,采用多个A/D、D/A、FPGA、DSP以及电平变换等器件,实测16比特高速A/D的地噪只有2比特,电磁兼容性也很好,完全满足设计要求。高速PCB设计涉及的知识面很广,设计规则十分繁杂,本文只是根据自身经验,选择要点进行了归纳,希望能够起到抛砖引玉的作用。篇幅所限,不可能面面俱到,更多细节问题,还需要PCB设计者随着实践经验的丰富不断学习和提高。

[1] 周润景,景晓松.Mentor高速电路板设计与仿真[M].北京:电子工业出版社,2008.

[2] 白同云.电磁兼容设计实例精选[M].北京:中国电力出版社,2008.

[3] 江思敏,唐广芝.PCB和电磁兼容设计[M].北京:机械工业出版社,2008.

[4] 周芸,柯敏毅.高速PCB板设计研究[J].通信电源技术,2008,25(2):23-26.ZHOU Yun,KE Min-yi.Research on high speed PCB design[J].Telecom Power Technologies,2008,25(2):23-26.

[5] 于治楼,杜光芹.高速PCB的地线布线设计[J].信息技术与信息化,2009(2):77-79.YU Zhi-lou,DU Guang-qin.The ground layout design of highspeed PCB[J].Information Technology&Informatization,2009(2):77-79.

[6] 乔洪.高速PCB信号完整性分析及应用[D].成都:西南交通大学,2006.