多总线地面测试设备中双SDRAM控制器的设计

刘延飞,杨铁阡,李 琪,倪 亮

(第二炮兵工程学院,西安 710025)

1 引 言

航空航天设备的测试通常根据不同测试对象的特征采用不同的测试总线,因此有必要提出一种多总线地面测试设备的设计方案,而测试设备需要读写速度快、容量大的存储器来存储采集的图像数据和各种总线上传输的数据。在各种随机存储器中,SDRAM价格低、体积小、速度快、容量大、控制相对简单,是比较理想的器件[1],但是SDRAM读写逻辑比较复杂,需要利用现场可编程逻辑器件对其进行控制[2]。另一方面,传统的单片缓存器数据存储量少、读写速度较慢,不能满足目前某型导弹多总线地面测试设备传输数据量大、速度快的要求,为此设计了基于乒乓操作的双SDRAM控制器,用于多总线地面测试设备中的实时图像采集与数据处理。

2 多总线地面测试设备设计思想

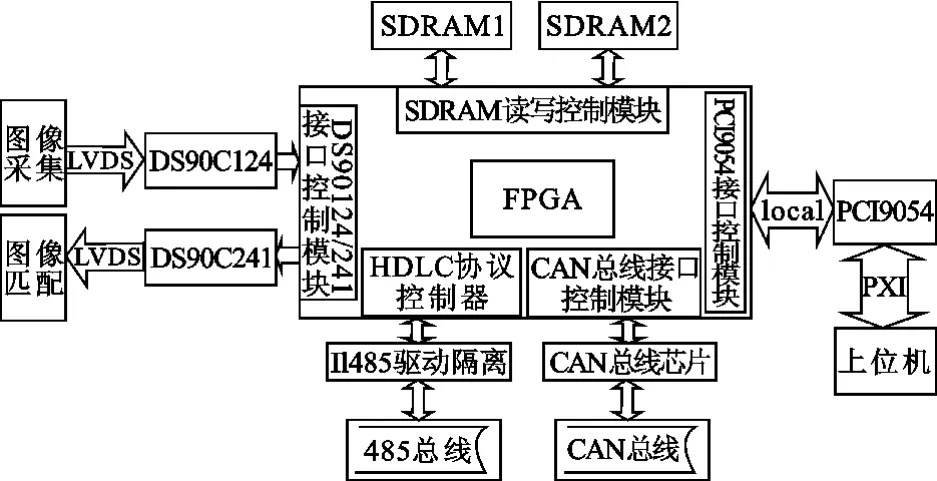

基于FPGA芯片高速、高集成度、编程灵活等优点,多总线地面测试设备以FPGA器件为控制核心,采用硬件描述语言Verilog进行编程设计[3],可以方便地实现数据的不间断采集、存储和显示等功能。其工作原理为:采集数据时,图像发生装置将实时图像数据通过 DS90C124转换、FPGA控制,存储在SDRAM中;数据上传时,通过专用接口芯片PCI9054将SDRAM中存储的数据通过PXI总线传输至上位机,完成图像数据的上传;图像显示时,上位机经PXI总线将采集的图像数据通过PCI9054后输出到SDRAM,FPGA控制SDRAM读数据,通过DS90C241转换,实现图像的显示[4]。上位机也可以通过发送指令,直接将保存在SDRAM中的数据经DS90C241转换后输出显示。利用同步RS485总线进行测试时,上位机向RS485驱动发送一个请求帧,随后转入数据接收等待状态,有同步串行数据到来时,首先完成HDLC协议分析,然后将其转换为16位并行数据由FPGA控制存入SDRAM中,当上位机读取数据时,将SDRAM中暂存的数据发送到上位机进行数据存储。利用CAN总线进行测试时,上位机将采集的图像与预先存储的特征图进行比较,根据对应的误差解算出控制指令,通过CAN总线接口发送给被测对象,同时被测对象将执行机构的相关数据通过CAN总线接口上传至上位机,实现数据的实时处理与显示。其整体设计框图如图1所示。

图1 多总线地面测试设备结构框图Fig.1 Structure of mutibus ground-based test equipment

3 SDRAM控制器方案

SDRAM具有空间存储量大、读写速度快、价格相对便宜的特点,适用于本系统。但其控制逻辑复杂,需要周期性刷新操作、行列管理、不同延时和命令序列等[5]。根据系统对图像存储容量及读写速度要求,本文采用了三星公司的K4S511632B-TC(L)。

SDRAM控制器针对SDRAM的指令操作特点,为SDRAM提供同步命令接口和时序逻辑控制,下面将以ALTERA公司的CycloneⅡ系列芯片中的EP2C70F67218为例,介绍SDRAM控制器的具体设计方法。图2为SDRAM控制器的接口原理图。

图2 SDRAM控制器接口原理图Fig.2 Schematic diagram of interface for SDRAM controller

SDRAM控制器作为顶层模块,由3个主要模块组成:接口控制模块、命令解析模块、数据通路模块[6]。下面将介绍各个模块的功能及Verilog语言实现方法。

3.1 接口控制模块

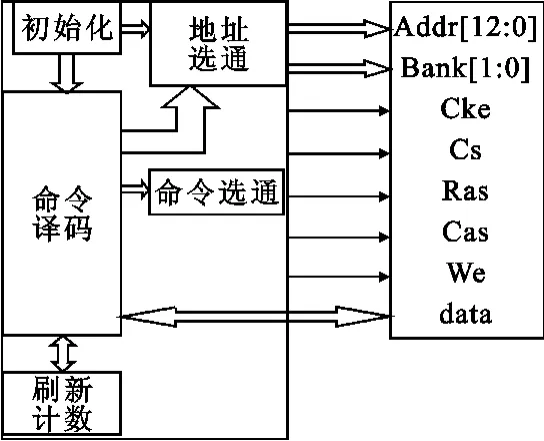

接口控制模块主要实现的功能是将输入的命令变量CMD[2∶0]翻译成接口指令和对刷新计数器的控制指令[7],如图3所示。首先通过状态机来完成对 CMD[2∶0]的解析,根据CMD[2∶0]的值来决定状态的转移,完成对 CMD[2∶0]的解码,实现SDRAM的预充电、刷新、读、写等功能。

图3 接口控制模块Fig.3 Interface controller module

3.2 命令解析模块

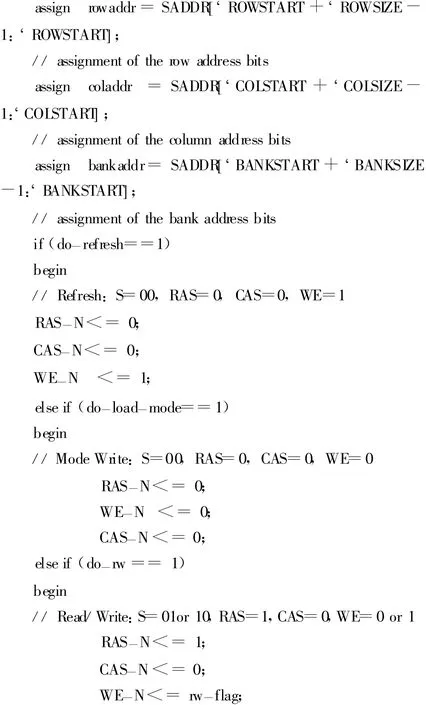

该模块主要实现对输入的指令请求进行仲裁判断,并将仲裁后要执行的指令解码成SDRAM需要的RAS、CAS等信号,从而实现对SDRAM的控制[8],如图4所示。

图4 命令解析模块Fig.4 Command analyzer module

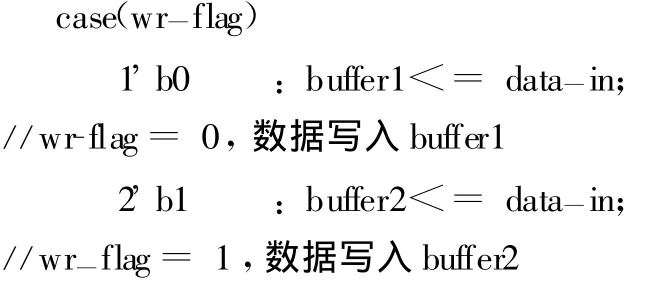

部分代码如下:

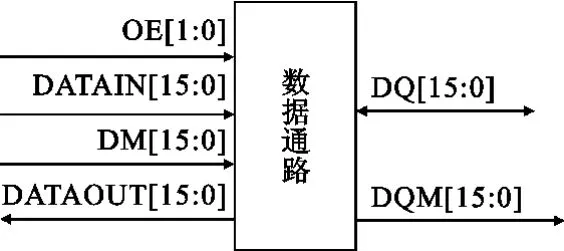

3.3 数据通路模块

数据通路模块主要是在读写命令期间处理数据的路径操作。模块结构图如图5所示。其中DQ是双向数据线,用来传输从SDRAM读出的数据和向SDRAM写入的数据。无论是数据在读出还是写入时,都是在OE为高时有效。DM是由主机输出的数据掩码,通过DQM输出到SDRAM的LDQM和UDQM管脚,进而控制SDRAM I/O缓冲的低字节和高字节[9],实现数据的有效传输。

图5 数据通路模块Fig.5 Data path module

3.4 缓存控制模块与乒乓操作

在本测试设备中,数据是按帧传输的。FPGA把接收到的数据先存储在其外接的SDRAM中,FPGA控制SDRAM再把数据通过PCI9054上传至上位机。如果FPGA外接一片SDRAM会使数据传输效率大打折扣。为了提高传输速度,体现面积换取速度的思想,测试设备数据流传输使用两片SDRAM进行乒乓操作[10],如图6所示。乒乓操作的最大特点是通过“输入数据选择单元”和“输出数据选择单元”按节拍相互配合地切换,将经过缓冲的数据流没有停顿地送到“数据流运算处理模块”进行运算与处理。对于整个控制器而言输入数据流和输出数据流都是连续不断的,很好地实现了数据的无缝缓冲与处理。

图6 乒乓操作工作原理图Fig.6 Schematic diagram of ping-pong operation

其部分代码如下:

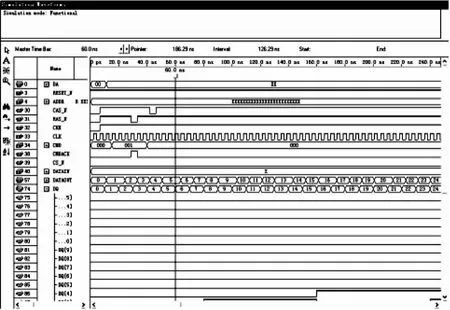

4 SDRAM控制器的FPGA实现

本文设计的SDRAM控制器基于Verilog语言编写程序,所选用的软件为QuartusⅡ8.1,利用软件进行综合优化。代码下载到系统后运行性能良好,能够较好地完成SDRAM与FPGA的数据交换。图7为在Quartus环境下的功能仿真。当CMD[2∶0]为001时开始读取数据总线上的数据,行、列选通信号依次有效,SDRAM内部数据读出至DATAOUT[15∶0]。

图7 读数据时功能仿真Fig.7 Function simulation for reading data

5 总 结

本文结合SDRAM控制指令的特点,详细地介绍了一种基于FPGA的双SDRAM控制器的设计方案。重点研究了SDRAM各个基本操作如初始化、行有效、列读写以及突发操作等等,分析了SDRAM控制器的基本功能以及指令操作特点。经过软件仿真和代码调试,证明本控制器能够应用于多总线地面测试设备中,具有良好的开发利用前景。

[1]Klehn B,Brox M.A Comparison of current SDRAM types:SDR,DDR,and RDRAM[J].Advances in Radio Science,2003(1):265-271.

[2]高子旺,顾美康.一种基于FPGA的低复杂度SDRA M控制器实现方法[J].计算机与数字工程,2010,38(1):194-196.GAO Zi-wang,GU Mei-kang.Low Complexity ImplementationMethod of SDRA M Controller based on FPGA[J].Computer and Digital Engineering,2010,38(1):194-196.(inChinese)

[3]吴继华,王诚.Altera FPGA/CPLD设计(高级篇)[M].北京:人民邮电出版社,2005:80-101.WU Ji-hua,WANG Chen.FPGA/CPLD design for Altera(Advanced Level)[M].Beijing:People′s Posts&Telecommunication Press,2005:80-101.(in Chinese)

[4]朱新平,基于CPLD和SDRAM的视频多功能卡设计[J].电视技术,2009,33(2):223-224.ZHU Xin-ping.Design of Video Multi-function Board Based CPLD and SDRAM[J].Video Engineering,2009,33(2):223-224.(in Chinese)

[5]陈焱辉.嵌入式SDRAM控制器设计研究[D].西安:西安电子科技大学,2009.CHEN Yan-hui.R esearch on the Design of Embedded SDR AM Controller[D].Xi′an:Xidian University,2009.(in Chinese)

[6]孙睿.基于SDRAM基本结构、操作及相关时序参数的研究[J].中国集成电路,2010,129(2):56-60.SUN Rui.A Research of Basic Structure Operations and Relative Timing Parameters of SDRAM[J].China Integrated Circuit,2010,129(2):56-60.(in Chinese)

[7]WANG Xiaohui,ZHAO Yiqiang,XIE Xiaodong,et al.Design and implementation of an efficient SDRAM controller for HDTV decoder[J].High Technology Letters,2007,13(4):1288-1290.

[8]GUO Li,ZHANG Ying,LI Ning,et al.The Feature of DDR SDRAM and the Implementation of DDR SDRAM Controllers via VHDL[J].Journal of China Universities of Posts and Telecommunications,2002,9(1):61-65.

[9]BI Zhankun,HUANG Zhiping,WANG Yueke.Application in high speed signal acquisition of DDR SDRAM MegaCore Controller[C]//Proceedings of the Seventh International Conference on Electronic Measurement and Instruments.[S.l.]:IEEE,2005:362-365.

[10]徐欣,于红旗,易凡,等.基于FPGA的嵌入式系统设计[M].北京:机械工业出版社,2005:79-102.XU Xin,YU Hong-qi,YI Fan,et al.Embedded system design based on FPGA[M].Beijing:China Machine Press,2005:79-102.(in Chinese)