高压ZnO厚膜压敏电阻的制备及导电机理分析

柯 磊, 李 桃

高压ZnO厚膜压敏电阻的制备及导电机理分析

柯 磊1, 李 桃2

通过高能球磨、丝网印刷和低温烧结制备出高压ZnO厚膜压敏电阻,并对厚膜试样进行了电学性能、物相成分和微观形貌的表征。结果表明:厚膜试样电位梯度达到3 159.4V/mm,漏电流为36.4μA,非线性系数为13.1,平均晶粒尺寸为1.29μm。高能球磨和低温烧结使厚膜试样的晶粒尺寸大大减小,有效提高了电位梯度值。分析了厚膜压敏电阻单晶界体系的导电机理,发现预击穿区势垒宽度的增加和单晶界电压的提高对其非线性性能以及压敏电压的提升影响明显,决定了压敏电阻的电学特性。

厚膜压敏电阻;电位梯度;导电机理

ZnO压敏电阻是一种电阻阻值随外加电压变化敏感的陶瓷材料。在一定的电压范围内,其电阻阻值是恒定的,电压、电流和电阻三者间的关系服从欧姆定律,伏安特性是一条直线。当超出该电压范围时,电流随电压的增加而急剧增大,表现出电流、电压之间的非线性关系[1-3]。ZnO压敏电阻的这种电流、电压关系曲线与稳压二极管的反向电流、电压关系曲线类似,所不同的是前者没有极性,双向电流、电压关系曲线反对称,故像2个背靠背的稳压二极管。这一特征使得ZnO压敏电阻既可用于直流电路又可用于交流电路,并且其可适应的电压和电流范围也远比稳压二极管的大,电压可由几伏至几万伏,电流则在微安至数千安之间,其吸收多余能量的容量,最大可达到兆焦耳以上。因此,ZnO压敏电阻是用于抑制瞬间高压、吸收浪涌电能的理想器件,可以广泛应用于各类电力设备和电子系统中[4-7]。

随着现代化技术的高速发展,以集成电路器件为核心的各类通讯、测量设备已广泛应用于航天、电力等行业,包含的范围越来越广,渗透到现代生活的各个领域。这类电子设备的元器件集成度要求高,同时对外界的干扰尤为敏感,对过电压的耐受能力又十分有限,故ZnO压敏电阻理所当然成为这类元器件的过压保护材料。但是,传统的片式ZnO压敏电阻体积较大,在多数场合不适合进行表面安装,迫切需要向新型的小体积膜式转变,以满足电子产品的微小、轻量型发展。用于高压稳压和过压保护的ZnO厚膜压敏电阻因其具有体积小、压敏电压高等优点越来越受到人们的关注,成为新型电子产品高压保护的首选材料[8-10]。

本文采用高能球磨、丝网印刷和低温烧结的方法制备高压ZnO厚膜压敏电阻,并对获得的试样进行电学性能、微观成分和形貌的表征。同时,就厚膜压敏电阻的非线性性质进行建模,分析其导电机理。

1 实验方法

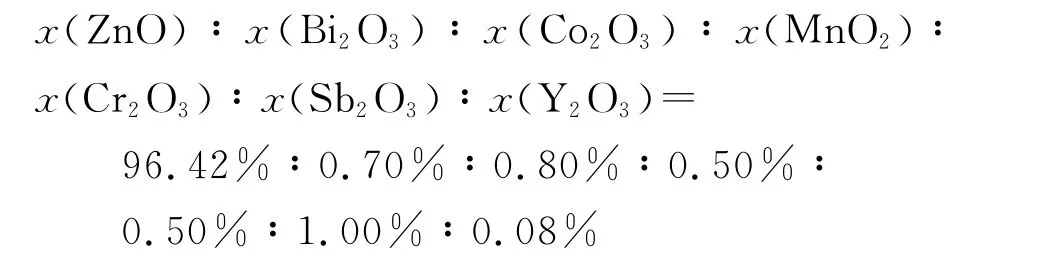

采用传统的ZnO压敏电阻粉体配方,添加稀土金属氧化物Y2O3,按照摩尔浓度比

称量配置混合粉体。将混合粉体中加入适量无水乙醇,在行星式高能球磨机中湿磨5h,球料体积比为20∶1,球磨转速为500r/min。湿磨后的混合粉体经烘干后,再在相同的球磨条件下干磨1h,得到混合均匀的干燥粉体待用。

将乙基纤维素溶于松油醇配制成质量分数为5%的有机载体,称量上述得到的干燥粉体,按

m(干燥粉体)∶m(有机载体)=4∶1

加入到有机载体中并调浆,得到具有一定黏度的压敏电阻浆料。以Al2O3陶瓷片为基底,丝网印刷商购的导电银浆置于基底上并烘干,形成底电极;采用30μm的丝网网板,将配制好的压敏电阻浆料分多次印刷于底电极上并烘干,形成厚膜压敏层;在厚膜压敏层上再次印刷导电银浆并烘干,形成顶电极。

将刷制完成的厚膜材料放入数控电阻炉中,以5℃/min的速率缓慢升温至725℃,保温0.5h后随炉降温至室温,得到烧结成型的厚膜材料。为了进行电学性能测试,在厚膜材料的上下电极层端面上,用商购的常温快干导电银胶粘制电极引出线,得到最终试样ZnO厚膜压敏电阻,并对其进行性能表征。

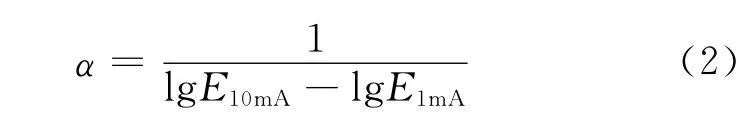

(1)利用CJ1001型压敏电阻直流参数仪测量厚膜试样的电位梯度E1mA、非线性系数α和漏电流IL等电学参数。

式中,U1mA为1.0mA/cm2电流密度下测得的试样击穿电压;d为试样的厚度。

式中,E10mA为10mA/cm2电流密度下得到的试样的电位梯度。

IL为0.75 U1mA的电压下测得通过试样的电流。

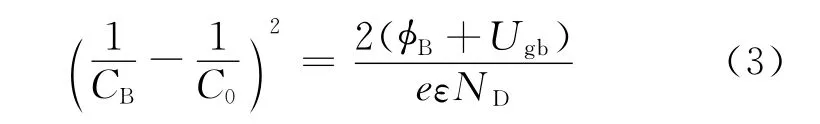

(2)利用HP4284A型精密阻抗分析仪测试厚膜试样的介电性能,并通过式(3)计算出试样的势垒高度φB、耗尽层宽度t、施主浓度ND和界面态密度NS等微观参数。和ZnO在700~750℃可以有液相生成[11],所以在这种情况下,烧结温度可以大大降低,低温烧结成为可能。

式中,C0和CB分别为施压前后单个晶界单位面积上的电容;Ugb为单个晶界上施加的电压;ε=8.5ε0为ZnO的电容率。

(3)利用JSM-5610LV型扫描电镜(Scanning Electron Microscopy,SEM)观察厚膜试样的微观形貌,并通过显微数字图像分析系统获得晶粒的平均尺寸。

(4)利用D/max-2550V型X射线衍射仪(X-ray Diffraction,XRD)分析厚膜试样的物相组成。

表1 ZnO厚膜压敏电阻的电学性能及微观参数Tab.1 Electrical parameters of ZnO-based thick film varistors

2 实验结果与讨论

表1列出了ZnO厚膜压敏电阻的电学性能及微观参数。通过高能球磨和低温烧结获得的E1mA达到了3 159.4V/mm,同时IL和α维持在一定的水平,分别为36.4μA和13.1。结合图1所示厚膜试样的微观形貌来看,烧结过后的晶粒尺寸比较一致,分布相对均匀,经显微数字图像分析系统得到晶粒的平均尺寸D为1.29μm。较小的晶粒尺寸使单位厚度内的晶界数量增多,故E1mA值提升。在实验前期的高能球磨期间,磨球、混合粉体的碰撞和冲击产生很大的能量,这部分能量通过磨球传给粉体,使粉体颗粒高度细化。粉体的粒度越小,其表面活性就越高,一定程度上的团聚缩短了原子扩散距离,增加了烧结推动力,导致粉体的烧结性增强、烧结过程加速。同时,ZnO压敏电阻材料的烧结过程是典型的液相烧结,其中引入的部分氧化物粉体在烧结过程中通常可以和ZnO或其他组分一起形成低熔点的化合物,在较低的温度下就开始熔化。例如Bi2O3

图1 ZnO厚膜压敏电阻的SEM照片Fig.1 SEM micrograph of ZnO-based thick film varistors

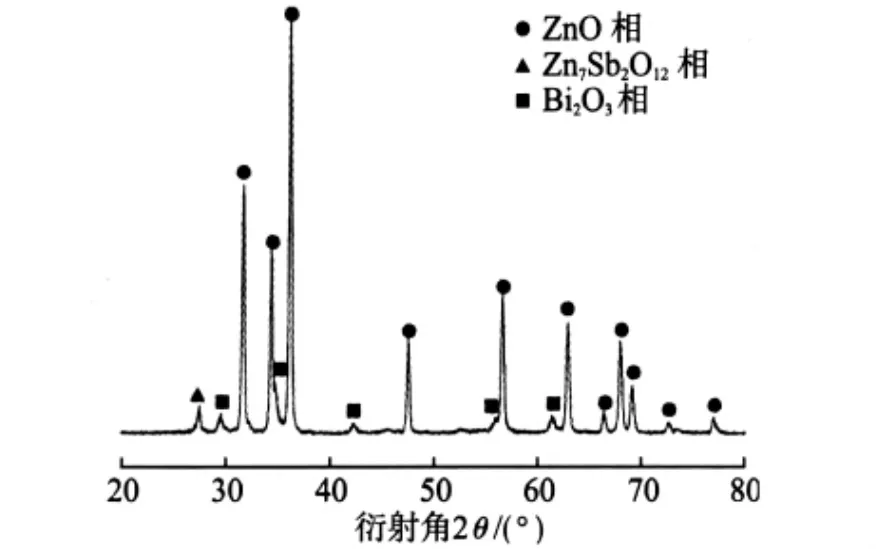

图2为ZnO厚膜试样的XRD谱线。由图2可见,厚膜试样的相组成和传统ZnO压敏电阻一致,ZnO相为主晶相,尖晶石相Zn7Sb2O12、富铋相Bi2O3为次晶相。在ZnO压敏电阻成分中,不连续的Zn7Sb2O12相对各相的分配和抑制晶粒生长具有一定的作用。同时,烧结过程中Bi2O3相以液相的形式存在于多晶界交汇处,直接影响着试样的非线性性质。

图2 ZnO厚膜压敏电阻的XRD谱线Fig.2 XRD data of ZnO-based thick film varistors

图3 ZnO厚膜压敏电阻的晶粒连接模型及其等效电路Fig.3 Microstructural model and equivalent circuit ofZnO-based thick film

实验中还发现,厚膜试样具有高且窄的势垒形状,以及较高的施主浓度和界面态密度。其中,φB为0.81eV,t为10.20nm,如表1所示。一般来说,厚膜试样的微观参数跟制备工艺密切相关,φB,t,ND,NS的大小由晶界的Schottky势垒决定[12]。高且窄的晶界势垒有助于在预击穿区阻碍电子的势垒翻越,在击穿区促使电子的势垒隧穿,可以很好地完成压敏电阻电学性能的线性-非线性转变。

3 导电机理的分析

ZnO厚膜压敏电阻的结构成分复杂,影响其导电性能的因素也比较多,因而基于材料整体的理论模型建立相对困难。为使模拟过程简化,对单个晶界进行建模,以此来模拟单晶界的导电特征。

ZnO厚膜压敏电阻是由ZnO晶粒和分布于其表面的晶界电阻层构成,相邻两个ZnO晶粒通过晶界电阻层连接。按照双Schottky势垒模型的说法[13],晶界两侧分别存在宽度为t的势垒层,故可以将相邻ZnO晶粒的连接近似地看作是由ZnO晶粒和分布于其表面的宽度为t的势垒层组成,模型示意图和等效电路图如图3所示。

将ZnO晶粒和其相连的晶界看作是一个整体,称作单晶界电阻,设其电导率为σc。考虑到在外界施加偏压后,ZnO晶粒t的变化很小,故可近似地认为

tL和tR分别为左右两侧势垒层的宽度。设ZnO晶粒的电导率为σg,势垒层的电导率为σb,则有

如果该独立的单晶界电阻上的外加电压为U,单晶界电阻的压敏电压为Ug时,则有

此时,流经单晶界电阻的电流密度为

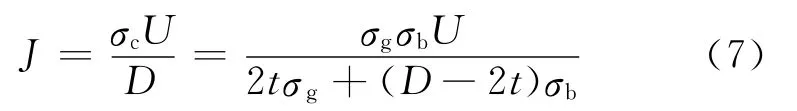

根据一些学 者的研究结果[14-15]可 知,σb的 近似表达式为

式中,σs为单晶界电阻外加零电压时的电导率;s为控制非线性特性的参数;Ug为单晶界电阻的压敏电压,其数值可由电位梯度和晶粒尺寸求得。

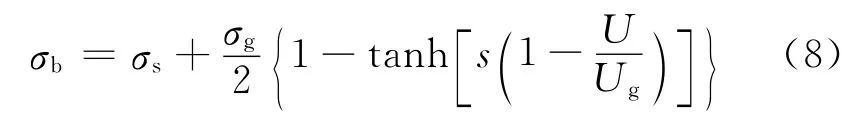

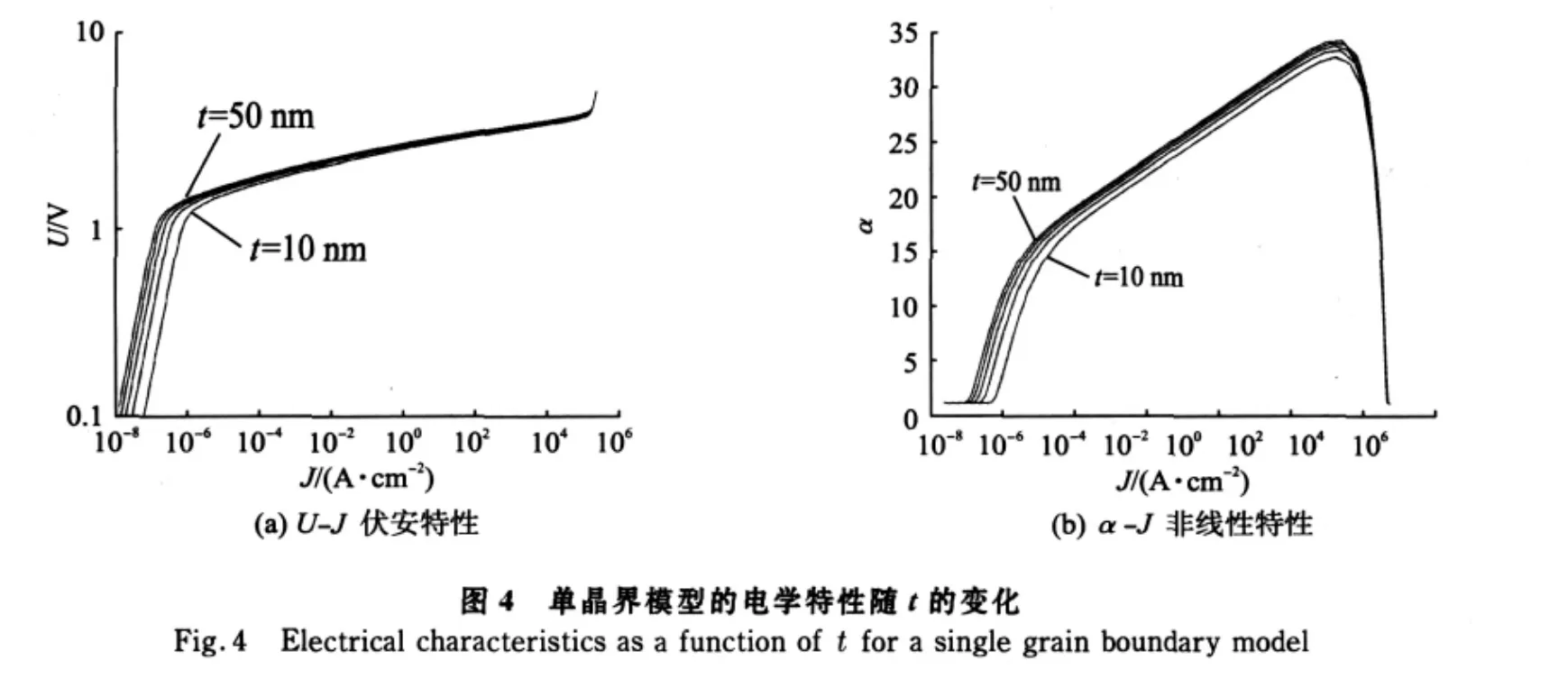

反复的制备实验得到的数据:t在10~50nm,Ug在2.5~4.5V,D 在1.0~1.4μm。在此范围内,将单晶界模型的U-J特性及非线性系数与t,Ug,D的关系模拟后如图4~6所示。

由图4可见,t对预击穿区和击穿区的U-J特性及非线性系数影响较为明显。在预击穿区,随着t的增加,势垒层的宽度加大,电子很难隧穿通过晶界势垒,而是通过热激发方式越过势垒进入晶界,宏观阻性加大,所以U-J曲线向低J方向移动。进入击穿区后,单晶界电阻被迅速击穿,预击穿区时的高阻状态使进入击穿区后的单晶界电阻非线性系数增大,所以高t的单晶界电阻非线性系数要大一些。

由图5可见,Ug对击穿区的U-J特性影响比较大。在击穿区,Ug值大的单晶界电阻拥有较好的晶界性能,故获得的压敏电压值要高一些,U-J特性向高U方向移动较大。

由图6可见,D对单晶界电阻的U-J特性及非线性系数影响较小,这主要是因为晶界在预击穿区和击穿区的作用占主导地位。针对单晶界电阻体系,压敏电压等指标的变化无法从单个晶粒尺寸的变化中得到。

4 结 语

采用高能球磨、丝网印刷和低温烧结的方法制备出高压ZnO厚膜压敏电阻,试样的E1mA值达到3 159.40V/mm,IL和α值分别为36.40μA和13.10。厚膜试样的D为1.29μm,较小的晶粒尺寸是提升其电位梯度值的主要原因。对厚膜压敏电阻的导电机理分析发现,在单晶界体系中,t和Ug对预击穿区和击穿区的电学特性影响明显,较高的t值使单晶界电阻非线性性能增强;较高Ug值的单晶界电阻拥有良好的晶界性能,获得的压敏电压值也较高。

[1]Clarke D R.Varistor ceramics[J].Journal of the American Ceramic Society,1999,82(3):485-502.

[2]Wan S,Lu W,Wang X.Low-temperature sintering and electrical properties of ZnO-Bi2O3-TiO2-Co2O3-MnCO3-based varistor with Bi2O3-B2O3frit for multilayer chip varistor applications[J].Journal of the A-merican Ceramic Society,2010,93(10):3319-3323.

[3]Anas S,Metz R,Sanoj M A,et al.Sintering of surfactant modified ZnO-Bi2O3based varistor nanopowders [J].Ceramics International,2010,36(8):2351-2358.

[4]Cheng Lihong, Li Guorong, Zheng Liaoying,et al.Analysis of high-voltage ZnO varistor prepared from a novel chemically aided method [J].Journal of the American Ceramic Society,2010,93(9):2522-2525.

[5]Takada M,Yoshikado S.Effect of thermal annealing on electrical degradation characteristics of Sb-Bi-Mn-Co-added ZnO varistors[J].Journal of the European Ceramic Society,2010,30(2):531-538.

[6]Nahm C W.The effect of sintering temperature on varistor properties of(Pr,Co,Cr,Y,Al)-doped ZnO ceramics [J].Materials Letters,2008,62(29):4440-4442.

[7]Wang Maohua,Yao Chao,Zhang Nanfa.Degradation characteristics of low-voltage ZnO varistor manufactured by chemical coprecipitation processing[J].Journal of Materials Processing Technology,2008,202(1/3):406-411.

[8]Cho Y S,Hoelzer D T,Schulze W A,et al.Crystallization and microstructural evolution of cordierite-based thick film dielectrics[J].Acta Materialia,1998,46(18):6421-6430.

[9]Arshak K,Gaidan I.Development of a novel gas sensor based on oxide thick films [J].Materials Science and Engineering B,2005,118(1/3):44-49.

[10]Wang Lanyi,Tang Guoyi,Xu Zhengkui.Preparation and electrical properties of multilayer ZnO varistors with water-based tape casting[J].Ceramics International,2009,35(1):487-492.

[11]Ashraf M A,Bhuiyan A H,Hakim M A,et al.Microstructure and electrical properties of Ho2O3doped Bi2O3-based ZnO varistor ceramics [J].Physica B:Condensed Matter,2010,405(17):3770-3774.

[12]Hu Jun,He Jinliang,Long Wangcheng,et al.Temperature dependences of leakage currents of ZnO varistors doped with rare-earth oxides[J].Journal of the American Ceramic Society,2010,93(8):2155-2157.

[13]Liu Jun,He Jinliang,Hu Jun,et al.The dependence of sintering temperature on Schottky barrier and bulk electron traps of ZnO varistors[J].Science China Technological Sciences,2011,54(2):375-378.

[14]南策文.非线性ZnO陶瓷的导电理论(Ⅱ)[J].物理学报,1986,35(5):633-637.

[15]南策文.敏感半导体陶瓷的显微物理模型(Ⅱ)[J].物理学报,1987,36(10):1305-1312.

Preparation of High Voltage ZnO-Based Thick Film Varistors and Conductive Mechanism Analysis

KE Lei1, LI Tao2

(1.Department of Mathematics and Physics,Shanghai Dianji University,Shanghai 200240,China;2.Department of HIS,Shanghai Kingstar Winning Software Co.,Ltd.,Shanghai 200436,China)

High voltage ZnO-based thick film varistors were prepared by high-energy ball milling,screen printing and low-temperature sintering.Electrical properties,phase composition and microstructure of the thick film samples were investigated.Experimental results showed that voltage gradient reached 3 159.4V/mm.Leakage current,nonlinear exponent and average grain size were 36.4μA,13.1,and 1.29μm,respectively.The notable decrease of grain size after high-energy ball milling and low-temperature sintering is the reason of voltage gradient increase.The conductive mechanism of single grain boundary system is analyzed.The increase of barrier width and single grain boundary voltage in the pre-breakdown region can enhance the nonlinear exponent andvoltage gradient,which determines the electrical properties of thick film varistors.

thick film varistors;voltage gradient;conductive mechanism

TM 283

A

2095-0020(2011)03-0157-06

2011-03-14

国家自然科学基金项目资助(10804071);上海市高校选拔培养优秀青年教师科研专项基金项目资助(sdj11010);上海电机学院科研启动经费项目资助(11C409)

柯 磊(1983-),男,讲师,博士,专业方向为纳米复合材料,E-mail:kelei@sdju.edu.cn