基于 MIL-STD-1553B协议的远程终端的 FPGA实现

孙 涛,张华春

(1.中国科学院电子学研究所,北京 100190;2.中国科学院研究生院,北京 100189)

SUN Tao1,2,ZHANGHuachun1*

1.Institute of Electronics,The Chinese Academy of Sciences,Beijing 100190,China;

2.Graduate University,The Chinese Academy of Sciences,Beijing 100189,China

1553B总线协议是由美国军方在上世纪 70年代制定的[1],被广泛应用于航空、航天等实时性和可靠性要求高的军事领域。目前支持该标准的商用芯片有 HOLT公司的 HI-61XX系列,DDC公司的 BU-6517X,BU-615XX系列等,这些芯片都是由美国生产的,价格昂贵。而使用 FPGA设计实现相应的远程终端协议[2],外接收发器完成 1553B远程终端的功能,可以降低成本,简化配置过程,增加使用灵活性。

1 1553B总线及远程终端节点

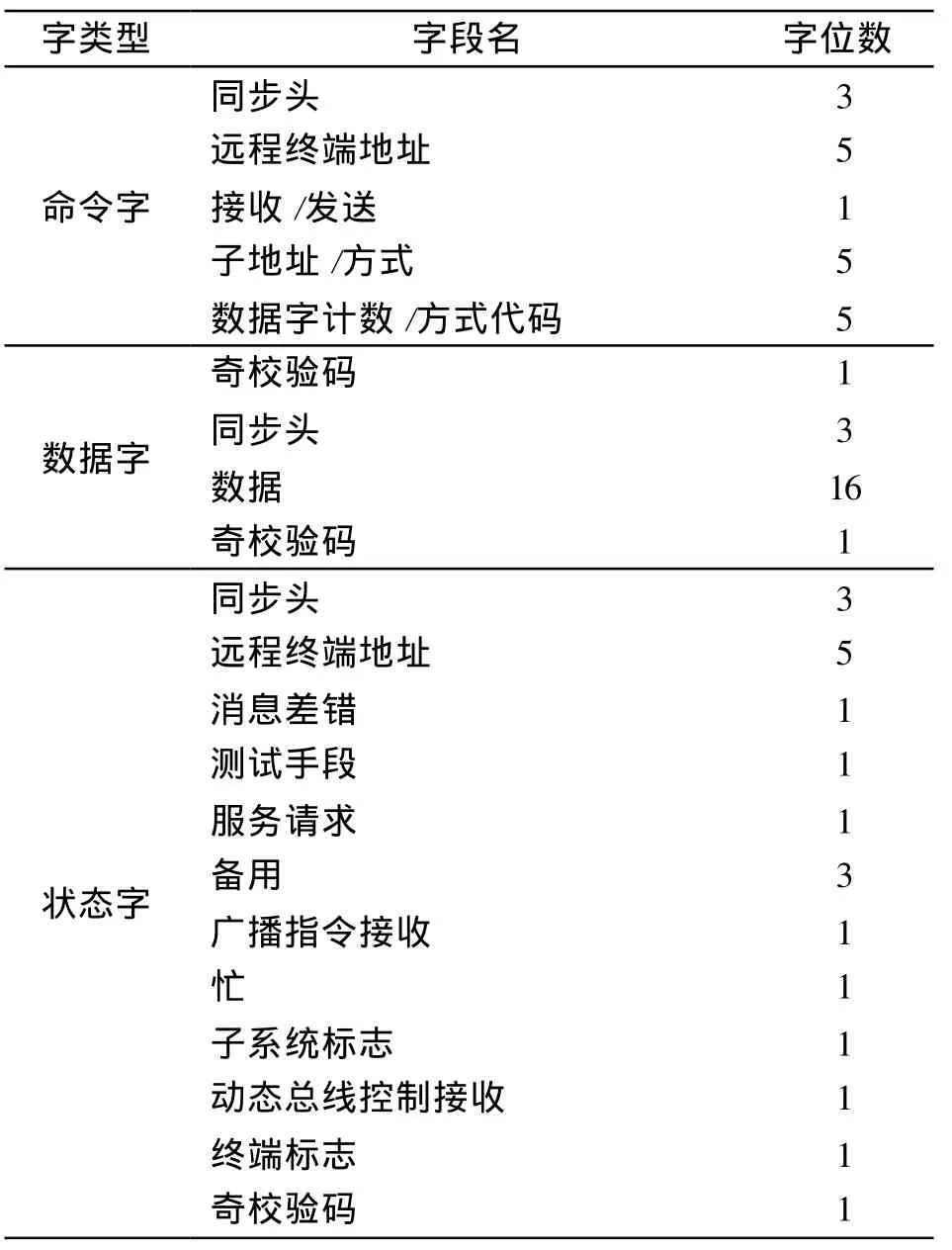

1553B协议采用双向曼彻斯特码,数据在总线上以串行脉冲形式传输,其传输速率为 1 Mbit/s。总线传输的信息字有三种,分别是命令字、数据字和状态字,见表 1。1553B总线上连接的节点类型分为三类:总线控制器(BC)、远程终端(RT)和总线监视器(MT)[3]。

远程终端节点支持的操作包括:①识别总线控制器的命令字是否有效,②对有效的命令字,按有效命令字所规定的方式做出响应并进行操作,③接收发送有效的数据字和状态字,④实现与微处理器之间的信息交换。

表 1 1553B信息字的帧结构

2 远程终端的 FPGA实现

1553B协议远程终端节点的系统结构框图如图1,一端通过接口管理模块与微处理器相连接,一端通过编码器与解码器与总线相连接。位流控制模块负责信息传递和数据交换,实现节点功能。

图 1 系统结构框图

2.1 接口管理模块

该模块主要功能是实现 FPGA模块与微处理器之间的数据交换[4]。由于微处理器总线为 8位,1553B的信息字为 16位,因此该模块需要在读写时实现 8位与 16位间的转换。这就需要通过两次置高地址锁存,读写使能,规定第一次为高 8位,第二次为低 8位。读取时第一次读使能读高 8位,第二次读使能读低 8位。

2.2 寄存器和内存管理模块

为保证可扩展性,寄存器部分预留了 17组寄存器,包括配置寄存器、命令寄存器、中断寄存器等[5]。这些寄存器主要用于状态信息的存储和功能参数的设置,如 RAM的 A/B区域选择,复位,设置 RT地址,产生中断。

内存部分使用一个 16×4 096 bit的双口 RAM,由微处理器和位流控制模块进行时分读写,完成微处理器与 1553B总线间的数据交换。RAM分为A、B两个区域,当前时刻只有一个处于激活状态,主要地址分配见表 2,堆栈用来存放消息描述符,每4个字描述一条消息。RT命令堆栈指针指向当前消息的消息描述符的第一个字。查找表对应的是子地址,存放的是指向数据块的指针。整个查找表包括 32个接收子地址、发送子地址、广播子地址和子地址控制字,其中子地址控制字指定了对应 RT子地址的内存管理和中断机制。数据块用来存放数据字。

表 2 RT内存映射

2.3 编解码器

编码器与解码器相互独立,由时钟管理模块提供时钟,完成同步头检测、时钟对准、曼彻斯特编解码、串并转换和奇偶校验等功能。

解码器的输入是总线信息序列,输出是信息字类型、16位信息字和奇校验结果。解码器时钟频率为 8 MHz,由时钟管理模块对 FPGA时钟分频得到。首先,来自总线的信息序列进入移位寄存器,进行同步头检测。得到一个有效的同步头后,将同步头类型缓存,开始进行曼彻斯特解码。对每位码字采样8次,在曼彻斯特跳变沿处取值,作为解码值,同时每隔 1 000 ns采样一次,与跳变沿处的取值对比,验证是否正确。对解码得到的新序列计算奇校验,将校验结果缓存。最后输出信息字类型、16位信息字和校验结果。

编码器的输入是信息字类型和 16位信息数据,输出是串行编码。命令字解析完毕后,需要回送状态字或发送数据字,这个功能由编码器完成。位流控制模块先把需要发送的信息写入相应的 RAM区,在得到发送命令后,位流控制模块中的状态机每次为编码器输入一个信息字,编码器计算奇校验,生成反相字,完成曼彻斯特编码,根据信息字类型为序列添加同步头,最后按照时钟管理模块提供的2 MHz时钟按位发送,这样就保证了总线上传输速率为 1 Mbit/s。

2.4 位流控制模块

位流控制模块是整个远程终端硬件系统的核心模块,完成状态机的跳转,实现各个逻辑模块间的数据交换。位流控制模块的流程见图 2。

图2 位流控制模块的处理流程

进入数据处理状态后,如果要求远程终端接收数据字,则先从配置寄存器 1的 bit 13得到使用RAM区域 A还是区域 B,假设使用区域 A,则①从RAM中地址为 0x0100的位置读取本条消息的描述符堆栈地址,②从相应查找表地址中读取子地址控制字,判断相应 RT子地址的 RAM管理和中断机制,③从相应查找表地址中读取数据块地址,④描述符堆栈的四个字由下向上一次写入当前命令字、数据块地址、时间标记字和块状态字,⑤在堆栈指针位置写入本条消息堆栈描述符的地址,⑥向数据块中写入接收到的数据字,⑦数据字全部接收完毕后,返回相应状态字⑧产生中断,通知微处理器数据接收完毕。如果命令字要求远程终端发送数据,则执行③后,在相应位置写入状态字,从数据块地址中读取数据字,置发送使能,通过编码器发送要求个数的数据字。不同状态对 RAM区域的访问如图3所示。广播处理状态与数据收发类似,不做状态字回复。方式代码处理状态,根据 1553B总线标准对不同的方式代码进行相关的位操作。

1553B协议字为 16 bit,堆栈大小为 256 K,描述一条消息需要 4个字,因此 RAM区最多可缓存 32条消息。对于每条消息,又对应着 32个子地址,可以存储 32个数据字。微处理器对 FPGA进行初始配置时[6],先将数据块地址,子地址控制字等信息写入相应的查找表固定地址内,当接收到命令字后,按命令字要求,将接收到的数据按对应子地址控制字要求的模式写入相应子地址的数据块中,或者从相应的子地址数据块中读取数据发送到总线上。

当检测出同步头 111 000时,则说明检测到了一个命令字,通过命令字解析,得到节点标识符 RT_ID、接收发送标识符 T/R、子地址(方式代码)SUB_ADDR和数据字个数(方式代码数据)DW_NUM。首先由 RT地址识别子模块验证 RT_ID,如果是11111,则进入广播处理状态;如果与节点 id相同,则判断子地址,若子地址是 00000或 11111,则是方式代码,进入方式代码处理状态;若子地址在 00000与 11111之间,则是数据传递,进入数据处理状态。

图 3 RT内存的管理

3 综合仿真

本文采用 Xilinx公司的 Spartan3E系列XC3S500E芯片[7],设计过程采用 Verilog HDL硬件描述语言[8],并在 Xilinx ISE9.2平台上完成整体模块的设计、综合,用 Modelsim SE 6.5完成仿真。

图 4 接收数据过程仿真图

图 4是对 RT接收数据的仿真结果:微处理器初始化堆栈指针和子地址查找表。clk为 16MHz的时钟,rx为总线上的数据,tx为 RT响应的状态字。接收完毕后,FGPA向微处理器发出中断信号,微处理器读取中断寄存器的信息后,从 RAM中以堆栈指针为起点读取数据,得到接收的两个数据字是 0x1234和 0x5678,结果表明接收正确。图 5是对 RT回送数据的仿真结果,表明 RT对命令字做出正确响应。

图 5 发送数据过程仿真图

4 总结

本文阐述了一种基于 FPGA的 MIL-STD-1553B协议远程终端的设计方法。通过微处理器的配置,本模块可以方便的实现 1553B总线网络中远程终端节点的主要功能,发送接收数据,广播以及方式代码等,有成本低、使用方便等优点。设计中预留了寄存器结构,可以将其他功能扩展到模块上,从而实现较完整的支持 1553B总线协议的硬件模块。

[1] CONDOE ENGINEERING INC.Mil-Std-1553 Tutorial[S].Santa Barbara,CA93103,2004.

[2] 张羽,胡玉贵,殷奎喜等.基于 FPGA的多串口扩展实现[J].电子器件,2009,32(1):233-236.

[3] 张传武,黄勤珍.Mil-Std-1553总线协议分析[J].西南民族大学学报自然科学版,2007,33(2):381-383.

[4] 罗一峰,蔡嵩.基于 1553B总线的接口设计与实现[J].现代电子技术,2006,29(2):71-73,76.

[5]ACE/Mini-ACE Series BC/RT/MT Advanced Communication Engine Integrated 1553 Terminal User's Guide[S].Data Device Corporation.1999.

[6] 欧伟明.基于 FPGA和 MCU的 200通道 A/D转换器的设计[J].电子器件,2007,30(4):1234-1238.

[7] 田耕,徐文波.Xilinx FPGA开发使用教程[M].清华大学出版社,2008,11.

[8] 夏宇闻.Verilog数字系统设计教程(第 2版)[M].北京:北京航空航天大学出版社,2008,1.