组合逻辑电路中竞争冒险的虚拟仿真实验设计

胡伟

(湖南第一师范学院,湖南 长沙 410205)

组合逻辑电路中竞争冒险的虚拟仿真实验设计

胡伟

(湖南第一师范学院,湖南 长沙 410205)

竞争冒险现象是组合逻辑电路工作状态转换过程中经常出现的现象,而实验检测法是最为可靠的竞争冒险检测方法,通过以Multisim软件为平台进行虚拟的仿真实验,可以形象生动地展示竞争冒险现象及其消除方法。

组合逻辑电路;竞争冒险;Multisim;虚拟仿真

1.组合逻辑电路中的竞争冒险

1.1 组合逻辑电路中竞争冒险

我们在进行逻辑电路的设计和制作时,常常出现设计上没有原理性错误,但实际构成的电路输出端却出现违背稳态下逻辑关系的尖峰脉冲,这是由于在进行逻辑设计时都是将构成逻辑的元件作为理想的元件进行设计的。但在实际中所有的逻辑门都存在传输延迟,且不同通路上门的级数也不同,所有的信号从输入到稳定也需要一定的上升时间和下降时间。因此,在组合逻辑电路的输出波形中就出现了违反原设计的尖脉冲波形的现象,即竞争冒险。

在组合逻辑电路中,如果由于竞争冒险而产生干扰脉冲,势必会对敏感负载产生不良影响,甚至导致误操作,如干扰脉冲可以使寄存器产生误操作,丢失储存的数据,还可以使计数器产生错误计数等等。竞争冒险有可能引起控制对象的误动作,导致系统瘫痪,造成事故,所以必须采取措施予以消除。

1.2 组合逻辑电路中竞争冒险的检测方法

1.2.1 逻辑函数法

1.2.2 逐级真值表法

若是单输入变量的较大规模电路,最直观的方法就是逐级列出电路的真值表,并找出哪些门的输入信号会发生竞争。然后判断是否会在电路的输出端产生干扰脉冲。这种方法虽然简单,但局限性太大,因为多数情况下都有两个以上输入变量同时改变状态的可能性。如果输入变量的数目很多,就更难于从逻辑函数式上简单地找出所有产生竞争冒险现象的情况。

1.2.3 卡诺图法

在组合逻辑电路的输入变量为多个变量的情况下,可以利用卡诺图来判断当两个以上的变量同时改变状态时,电路是否存在竞争冒险现象。把逻辑函数化为最小项之和形式,然后得到该逻辑函数的卡诺图。若在卡诺图中存在两个相切但不相交的圈(可以是“1”构成的圈,也可以是“0”构成的圈),则会产生竞争冒险现象[1]。

1.2.4逻辑模拟法

若输入变量较多,电路规模较大,人工进行分析非常复杂,可以采取计算机辅助分析的方法(CAA)。即通过编写程序代码,在计算机上运行数字电路的模拟程序,以实现在计算机上数字电路运行的模拟,迅速地判断出电路是否会出现竞争冒险现象而输出尖峰脉冲。

1.2.5 实验观察法

将组合逻辑电路输入端的信号应包含的所有可能的输入状态的变化都输入到示波器,用示波器来观察电路的输出端是否存在因竞争冒险现象而产生的尖峰脉冲。

以上几种方法虽然提供了检查各种电路竞争冒险的途径,但即使使用计算机辅助分析手段检查过的电路,往往还需要经过实验的方法检验,才能最终确定电路是否存在竞争冒险现象。因为在用计算机软件模拟数字电路时,只能采用标准化的典型参数,有时还要做一些近似,得到的模拟结果有时和实际电路的工作状态会有差异。因此,只有实验检查的结果才能得出最终的结论,但是真正的实验观察法所需实验设备较多,操作相对比较繁琐,我们可以Multisim为平台,方便灵活地进行虚拟仿真实验,可以更好地检测到冒险竞争现象,同时,也有利于教师进行形象生动地课堂教学活动,帮助学生将理论与实际联系起来。

2.Multisim虚拟仿真软件特点

Multisim仿真软件是一种专门用于电子电路设计与仿真的EDA工具软件,它改变了以往以变量估算和电路实验为基础的电路设计方法,能完成从电路的仿真设计到电路版图生成的全过程,从而为电子系统的设计、电子产品的开发和电子系统工程提供了一种全新的手段和便捷的途径。与其他EDA软件相比,Multisim仿真软件具有如下特点[2]:

(一)Multisim具有直观友好的仿真界面,将电路原理图的创建、电路的仿真分析和分析结果的输出都集成在一起,采用直观的图形界面创建电路,在计算机屏幕上模仿真实实验室的工作台,绘制电路图需要的元器件、电路仿真需要的测试仪器均可直接从屏幕上选取,整个操作界面就像一个实验工作台,与实际操作近乎相同。无论是对工程设计的模拟还是对现场的检测都体现出了强大的功能。

(二)Multisim拥有庞大的元器件库(如信号源、电路基本元器件、模拟集成电路、数字集成电路、指示部件、控制部件等)和大量的仿真测试仪表(如示波器、万用表、瓦特计、扫描仪、失真仪、网络分析仪、逻辑转换仪、字信号发生器等),另外,Multisim 10还增加一些3D虚拟原件,可组成三维立体仿真电路,不仅可以进行分析研究,而且这些仪器仪表的外观和使用与真实仪器极为相似,可以方便地用于教学演示。

(三)Multisim具有完备的分析手段。可对模拟、数字和射频电路进行各种分析,包括直流工作点分析、交流分析、瞬态分析、傅里叶分析、噪声分析、失真分析、参数扫描分析、温度扫描分析、零极点分析、传输函数分析、灵敏度分析、最坏情况分析、蒙特卡罗分析、直流扫描分析、批处理分析、用户定义分析、噪声图形分析和射频分析等17种仿真分析方法,基本上能满足一般电子电路的分析设计要求。

(四)Multisim具有超强的仿真能力。支持模拟电路、数字电路、模拟/数字混合电路以及射频电路的设计仿真。既可以分别对模拟电子系统和数字电子系统进行仿真,也可以对数字电路和模拟电路混合在一起的电子系统进行仿真分析。Multisim 10还引入了单片机仿真内容,支持汇编语言和C语言,使得虚拟仿真显得更加灵活实用。

3.基于Multisim 10的竞争冒险虚拟仿真实验

在数字电路中竞争冒险对数字电路有诸多的危害,那么我们可以通过以下几种方法消除竞争冒险。

3.1 修改逻辑设计消除法的虚拟仿真实验

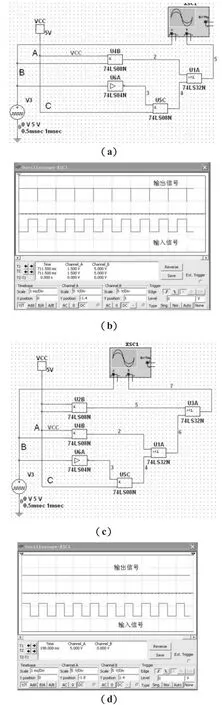

在图1a中,根据组合逻辑电路输出F=AB+BC,由于A=C=1,则F=B+B=1,即无论输入信号如何变化,输出F应恒为高电平。但是通过虚拟仿真实验可以发现,在输入信号的下降沿,电路有负的窄脉冲输出,此为竞争冒险现象,如图1b所示。我们可以通过增加冗余项AC,将其函数修改为F=AB+BC+AC,如图1c所示。同样,在A=C=1的情况下,无论信号如何变化,输出始终保持为高电平,并且通过实验可以观察到,经过增加冗余项,改变逻辑设计后的输出已经没有窄脉冲了,而是恒定的电平,如图1d所示[3]。

图1 修改逻辑设计消除法的虚拟仿真实验

用增加多余项的方法修改逻辑设计,可以消除一些竞争冒险现象,但是,这种方法的适用范围是有限的,修改后的电路有可能会出现新的冒险竞争现象。

3.2 引入脉冲消除法的虚拟仿真实验

引入脉冲可以分为引入封锁脉冲和引入选通脉冲两种方式。引入封锁脉冲是通过在门电路的输入端加一封锁脉冲,要求封锁脉冲与输入信号的状态转换同步,且封锁脉冲的宽度大于或等于电路从一个稳定状态到另一个稳定所需要的时间。那么,在信号状态转换的时间内,将可能产生尖峰脉冲输出的门封锁,电路的输出就不会出现竞争冒险现象。而引入选通脉冲,则是在电路的输入端引入一个取样脉冲,由于取样脉冲的作用时间取在电路达到新的稳定状态之后,使电路的输出端不会出现尖峰脉冲。在此,我们通过Multisim仿真通过引入封锁脉冲来消除竞争冒险现象。

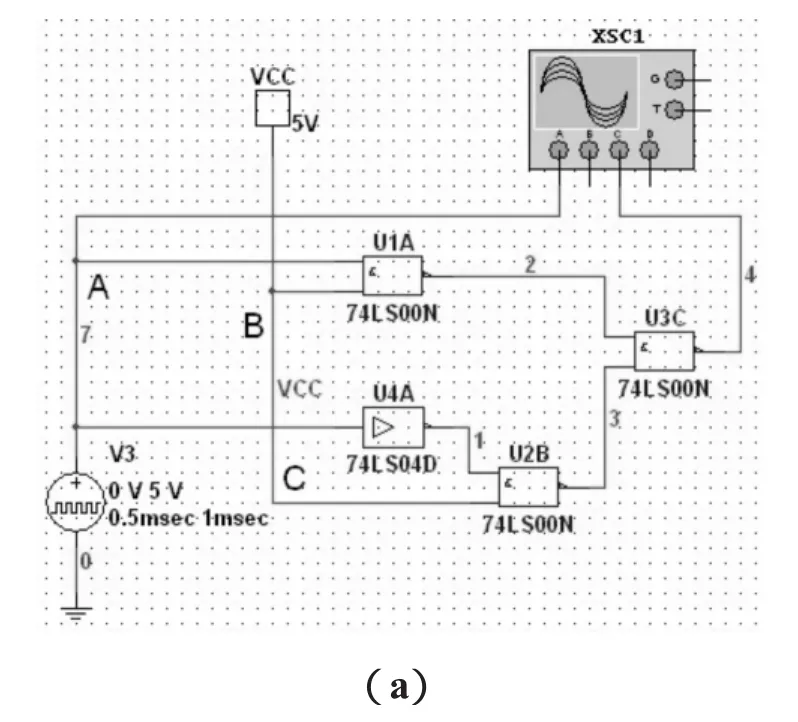

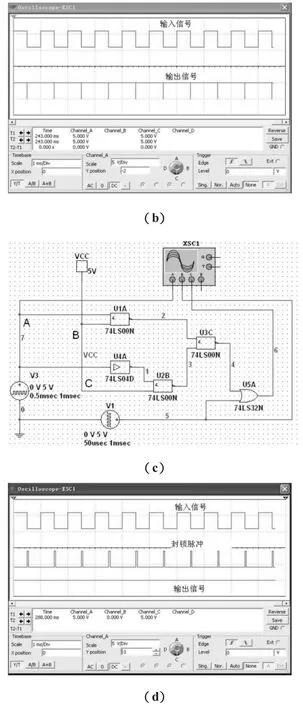

如图2a组合逻辑电路,逻辑函数F=AB·AC,由于B=C=1,所以F=A·A=1,说明输出端的电平应恒为1,保持高电平。通过虚拟实验观察,发现输出信号有窄负脉冲,如图2b所示,说明有竞争冒险现象,我们可通过图2c中的方式引入封锁脉冲来消除。通过图2b可以观察到竞争冒险现象是出现在信号脉冲源V3变化的负边沿时刻,若在此时刻的或门的一输入端输入高电平,那无论此时或门的另外一输入端(即图2a原输出端)为何值,输出端都为高电平,这就完成了此时刻对输出的封锁,即使有竞争现象也能保证在最终的输出端维持高电平。因此,在虚拟实验中,我们在图2c中加入了封锁脉冲源V1,该脉冲源仅在信号脉冲源V3的负边沿时刻(即出现竞争时刻)的前后短时间内产生窄脉冲来封锁或门,使最终输出维持在高电平,从而达到消除竞争冒险的效果,实验结果如图2d所示。

图2 引入脉冲消除法的虚拟仿真实验

通过引入脉冲消除竞争冒险的方法简单易行,而且不需要增加电路元件,但选通信号的作用时间和极性等一定要合适,若时间过长,会影响到电路的非竞争冒险时间段正常输出而产生错误的结果。

另外,对于速度较慢的组合逻辑电路,由于竞争冒险而产生的尖峰脉冲一般情况下很窄,所以可采用在电路输出端并联电容的方法消除尖峰脉冲,并用门电路的输出端电阻和电容构成低通滤波器,对很窄的尖峰脉冲能起到平波的作用,消除干扰脉冲。虽然此方法简单易行,但增加了输出电压波形的上升时间和下降时间,是波形变坏,接入电容具体值较难确定,要通过实验来测试[4]。

4.结束语

利用软件Multisim构建虚拟仿真模拟实验平台,可让学生模拟操作使用。该实验不但简单易行,具有交互性、可操作性,真实感与实际的仪器基本相同,元件选择范围广泛,数修改方便。通过该实验不但能够清晰地观察到实际实验中难以观察到的竞争冒险现象,而且可以方便地通过实验方法消除竞争冒险现象,理论联系实际,能极大地提高教学效果。也为真实的实验打下基础,避免实际操作中元件的损耗,使电路调试快捷方便,减少仪器设备的损坏,提高了教学质量[5]。

[1]张京英.组合逻辑电路中的竞争冒险现象的判断和消除 [J].青海师范大学学报:自然科学版,2003,(2):43-44.

[2]黄培根,任清褒.Multisim 10计算机虚拟仿真实验室[M].北京:电子工业出版社,2008.

[3]从宏寿,李绍铭.电子设计自动化——Multisim在电子电路与单片机中的应用[M].北京:清华大学出版社,2008.

[4]阎石.数字电子技术基础(第四版)[M].北京:高等教育出版社,1998.

[5]田野,孙宏宁,祖大鹏.基于Multismi V7平台的组合逻辑电路中竞争冒险的分析[J].哈尔滨师范大学自然科学学报,2004,(4).

Design of Virtual Simulation for Race and Hazard in Combinational Logic Circuit

HU Wei

(Hunan First Normal University,Changsha,Hunan 410205)

Race and hazard is a common phenomenon in the working state transition process of combinational logic circuit.The method of experiment examination is the most reliable one.By virtual simulation based on Multisim,the race and hazard phenomenon and elimination are displayed vividly.

combinational logic circuit;race and hazard;Multisim;virtual simulation

TN791

A

1674-831X(2010)05-0152-05

2010-08-20

湖南第一师范学院院级课题(XYS09N06)

胡 伟(1978- ),男,湖南浏阳人,湖南第一师范学院讲师,硕士。

[责任编辑:葛春蕃]