CPLD测试方法研究

于明

(集成电路测试技术研究中心 BJAST 北京自动测试技术研究所)

0 引言

CPLD(Complex Programmable Logic Device)是一种可编程器件,它的出现使得新产品的开发周期大大缩短,开发成本得到节省。随着CPLD被广泛应用到各个领域,对其准确性和可靠性的要求也变得越来越高。所以,对CPLD器件故障的检测和诊断方法技术的研究就显得尤为重要。本文正是针对上述问题,以Altra MAX7000系列EMP7064SLC84-10为主要的研究对象,在详细研究器件内部结构的基础上,基于“分治”的基本思路对CPLD的测试理论和方法做探索性研究。

本文的研究基于集成电路测试系统BC3192V50环境下进行。在该系统所提供的资源范围内进行的CPLD测试开发和测试方法研究工作。BC3192V50测试系统是由北京自动测试技术研究所研制开发的,基于当前国际先进VXI总线的数模混合集成电路测试系统 。适于大容量、多管脚的可编程芯片测试。

本文主要目的是通过基于BC3192V50测试系统,对CPLD器件的测试方法测试模型进行研究。在同一个操作流程中完成对CPLD芯片的多次“配置一测试”过程,减少操作环节,提高CPLD芯片的测试效率。其核心问题是建立什么样的测试模型以达到故障的高覆盖率,以及针对模型施加什么样的激励可以使故障激活,并且便于在输出端观察结果。测试模型最少化,测试向量高效化是主要目标。最终提出分块测试模型,并给出相应优化测试向量,以在测试系统上实施测试。

1 Altra MAX7000系列CPLD的主要特点

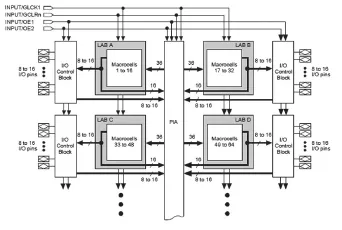

MAX7000系列体系架构(见图1)包括如下的组成部分:逻辑阵列块(Logic array blocks),宏单元(Macrocells), 扩展乘积项 (Expander product terms),可编程互联阵列(Programmable interconnect array),I/0控制块(I/O control blocks)。

图1 MAX7000系列的体系架构

MAX7000构架当中包含有4个专用的输入管脚,可以用来作为普通的输入管脚,或者作为每一个I/O管脚的高速、全局控制信号(时钟,清零和2个输出使能)。MAX7000系列器件是基于高性能逻辑阵列模块LAB (Logic Array Blocks——逻辑阵列块)连接的体系架构。LABs由16个宏单元阵列组成,多个LABs通过PIA(Programmable Interconnect Array——可编程互联陈列)互相连接。所有的专用输入、I/O管脚和宏单元都与PIA这个全局总线相连接。

MAX7000系列,布线资源简单,且在测试其他资源中重复用到,本文以宏单元,触发器,I/O资源测试为主要研究对象。

2 有关PLA的研究

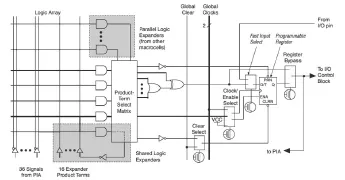

PLA结构(见图2)类似于CPLD宏单元中与或阵列, 有关CPLD的研究多集中在早期对于PLA的研究上 。通过增加外围电路,建立可测性结构,并施加相应的测试向量来进行PLA的故障检测。

图2 PLA结构

虽然这样的设计理论是可行的,但对实际CPLD器件,其操作和控制很困难。实际器件的与或阵列是混合在宏单元中的重要组成部分,技术上还不可能去控制阵列中的一个节点。要进而对某一个节点加载外围电路做到对节点的控制和检测,在硬件或是软件上都是很难实现的。其次,这些可测性的讨论大都需要引入外围电路作为可测性控制。但是,外引电路会破坏器件本身的结构,占用器件的资源,并且附加而成的电路势必会影响器件原有的时间特性而产生多余的延时。对于应用型测试,不方便介入器件内部改变其结构,因此以建立适当故障模型为研究核心。为此,下面根据器件实际结构提出故障模型,建立新的诊断方法,完成测试过程。

3 宏单元测试模型的建立及测试向量优化

可以发现除去扩展乘积项,一个宏单元包含5个乘积项。而对应单一宏单元有且只有一个输出,所以乘积项数量与输出是5:1的关系。以此建立宏单元故障模型更符合实际结构。关于输出:一个宏单元只有一个输出,并且此输出是由所在与或阵列唯一产生。所以,如果输出分配到这个宏单元当中,那么就可将测试限定在了此宏单元里。其他宏单元与或阵列不会控制到此时宏单元的输出。也就是说,如果用到宏单元A的输出,那么动用的与或阵列资源也一定在宏单元A中。

图3

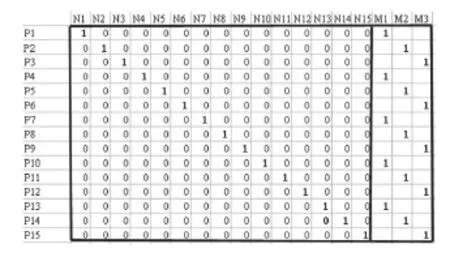

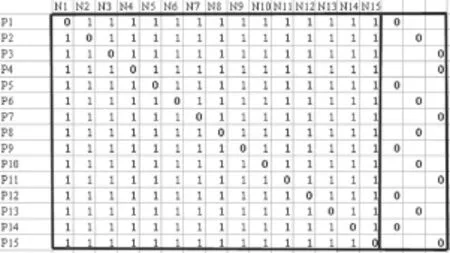

基于此,给出宏单元阵列测试简化故障模型。以15输入15乘积线3输出模型(i15pp15_A模型)为例,

如图4,(其中N为输入,P为乘积项,M为输出)

图4 i15p15o3_A模型

左侧为与阵列,右侧为或阵列。1 表示配置正有效,0表示配置反有效 空表示无节点。

当施加与P1乘积项配置相同的测试向量10000 00000 00000,以及施加与P2乘积项配置相同的测试向量01000 00000 00000 可以从M1输出端检测出输入端故障,P1/P2两乘积项之间的桥接故障,在两乘积线上的固定通断故障,以及与M1相连的或阵列出现故障的情况。

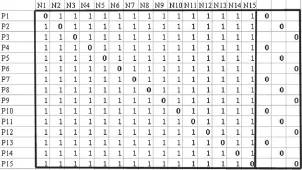

因为P1,P4,P7,P10,P13的故障表达都要在同一时刻通过M1表示,所以他们之间的桥接在I15p15o3_A模型下不能判定。如:在P1与P4因桥接配置完全互换的情况下,没有向量可以判断这类错误。在M1端的输出与无故障情况下相同。同理,P2,P5,P8,P11,P14的此类故障,P3,P6,P9,P12,P15的此类故障,都为i15p15o3_A模型的故障模型失效点,无法通过施加任何向量来判断。基于此,设计建立于I15p15o3_A模型之上的失效故障补充模型。图5为I15p15o3_~A模型。

图5 I15p15o3_~A模型:

在此模型中,A模型那些被屏蔽的故障被去除。比如对于M1, P1,P4,P7,P10,P13桥接的故障得到解决。P1 P4之间的桥接故障仅通过测试向量1000 0000 0000 000 和 0001 0000 0000 000就可以从M1端判别出来。同理其它。虽然补充的模型又引入了其它的故障失效,却已经完成了对模型A的补充,使得模型得到完满测试。

考虑与阵列对角线上点的判断还有图6,图7表示的相反配置情况:

图6 I15p15i3_B模型:

图7 I15p15i3_~B模型:

我们采用的是1-Walking测试向量,以便完成对模型的全面测试。但是对于补充模型,只需要给出判定之前失效点的测试向量就可以,不必再完整施加一遍测试向量。

4 测试向量优化

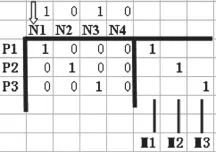

从上面的模型中可以发现,测试两两之间的故障,需要两个测试向量综合判断才能达到完整测试。现在寻求测试向量简化的方法。简单模型情况--相邻故障如图8所示。

图8 相邻故障

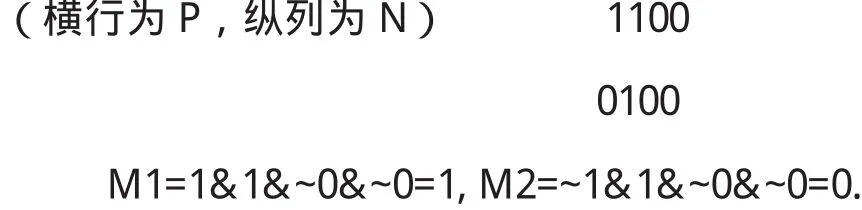

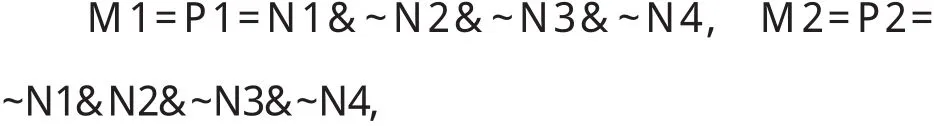

首先表示出阵列的逻辑表达式:M1=P1=N1&~N2&~N3&~N4, M2=P2=~N1&N2&~N3&~N4,

当施加如图8的测试向量的时候,

在无故障的情况下:

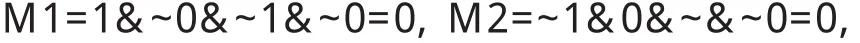

M 1=1&~1&~0&~0=1&0&1&1=0 M2=~1&1&~0&~0=0.

当故障表现为P1→P2(配置P2的节点由于故障也会表现在P1上)时:乘积线上的故障模型变为:

当故障表现为P2→P1时:乘积线上的故障模型变为:1000

两种故障模型在这样的测试向量下表现出来的现象是不同的,且都和无故障模型下的结构不同。由此可以看出通过一个测试向量,就能根据M1,M2的输出情况检测出相邻乘积项故障情况。

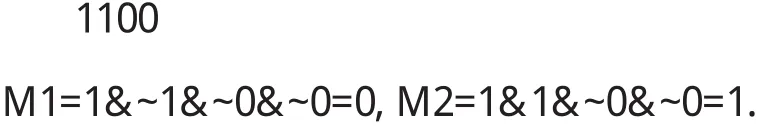

简单模型情况—间隔故障 如图9所示。

图9 间隔故障

阵列的逻辑表达式:

当给入如图的测试向量时,

在无故障的情况下:

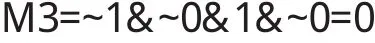

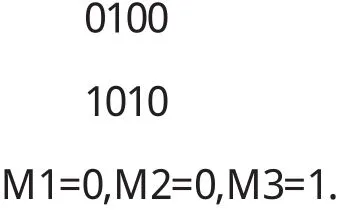

当故障表现为P1→P3时:乘积线上的故障模型变为:1010

当故障表现为P3→P1时:乘积线上的故障模型变为:1000

由此可以看出通过一个测试向量,就能根据M1,M2的输出情况检测出间隔的乘积项故障情况。

对比前面的方法,如果完成上面模型的测试,用1-Walking则需要两个向量分别对模型施加,才能判断P1和P3的故障情况。分别是1000和 0010 。

(1000 能判断P1→P3的情况,0010能判断P3→P1的情况)。因此,我们可以发现双1步进测试向量比单一步进测试向量具有更高的测试效率,可以在一个测试向量的情况下诊断出两两之间的故障。因此对于输入,我们采取的是测试向量1100,0110 ,0011,1010,1001, 0101 用这样双 1 步进的测试向量来代替单1步进的测试向量能把测试效率提高一倍。

EPM7064的64个I/O 除了4个配置的管脚以外,一共有60个普通I/O。如果是10个输出,按照前面建立故障模型的原则——输出与乘积项1/5,且考虑输入与乘积项相等,那么这个模型就需要50个输入。受可利用管脚资源的限制,如果建立的模型继续增大,器件的管脚已经不能够满足模型需要的数量。所以为了最大化模型规模以减少配置次数,采用i50p50o10故障模型对与或阵列测试。针对这部分,一共需要4个配置模型。分别是上文提到的A模型,~A模型,B模型,~B模型。那么一共需要配置4×(60/10)=24次来完整的测试宏单元阵列部分的逻辑资源。以用到所有的输出,覆盖所有的宏单元测试。输入在测试中会被重复用到。

5 触发器及I/O测试

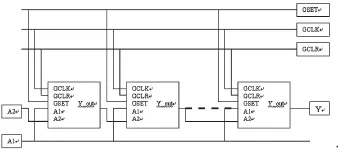

根据EPM7064SLC84-10,建立与触发器结构相适应的电路模型。从宏单元结构可以看到,一个触发器是针对一个宏单元唯一的。GSET,A1,A2为来自于宏单元的信号,GCLK,GCLR是全局控制信号。在EPM7064中有很多相同结构,为了能尽量用少的配置次数完成对触发器结构的测试,把触发器资源串成链表形式。框架如图10表示。

图10 电路模型框架图

中间虚线部分代表省略若干个模块。输入波形,以观察仿真输出结果并与实际测试结果进行比较,做出故障判断。

I/O资源测试:因为I/O为双向管脚,因此配置74LS244总线收发器到器件中,以检测器件管脚双向工作的能力。配置时要达到对所有I/O的覆盖,完成对所有I/O管脚测试。

6 系统实现

根据给出测试图形和测试向量,对CPLD进行设计编译和输入,应用Altera公司的Quartus CAD环境生成所要的配置文件。由于该文件的内容随编程信息变化而不同,另外,配置数据比较长,按字节配置需要大量向量。因此,采用手工编制配置向量显得很不且实际,必须采用自动生成的配置数据的方法,在生成后再加载给CPLD器件。测试系统正是完成了编程器的作用,配置的设计码流变为了测试系统可以识别的文本文件,通过这个文本文件在测试系统上的运行,完成对器件的配置。

图11 基于测试系统的一般过程

7 结束语

本文主要基于测试系统BC3192V50给出了CPLD的一般测试过程及过程分析。采取“分治”的测试方法,针对器件各资源部分,建立不同故障模型,并通过测试系统对器件配置。进而依据模型建立起优化的测试向量,使得CPLD器件得到合理测试。

[1](冯建科,张文生,郭士瑞.VXI数模混合信号集成电路测试系统[J],电子测量与仪器学报,2005,19(2):52-57.

[2]R. Rajsuman.A New Testing Method for EEPLA[J].IEEE Trans. on CAD, Vol. 13, No. 7,

[3]A Munshi, F. Meyer, F. Lombardi.A New Method for Testing EEPLA’s[J].Proc. IEEE International. on Defect and Fault Tolerance in.

[4]C. Stroud, J. Bailey, J. Emmert.A New Method for Testing Re-Programmable Programmable Logic Arrays”, to be published J. Electronic Testing: Theory and Application, 2000.