基于FPGA的高速大容量异步FIFO的实现

滕明晖 , 杨瑞峰

(中北大学信息与通信工程学院 山西省太原市学院路3号 030051)

0 引言

此设计运用在测试光纤陀螺仪的数据采集中。光纤陀螺是基于Sagnac效应的新型全固态光学陀螺,与传统的机械陀螺相比,它具有耐冲击、抗加速运动、寿命长、分辨率高、动态范围宽、启动时间极短等突出优点,已成为新一代捷联式惯性导航系统中理想的惯性器件。在测试光纤陀螺要采集大量的数据采集,所以需要大容量的数据缓冲。

本文设计出一种采用 SDRAM作为FIFO缓冲,利用FPGA实现控制的高速大容量的异步FIFO是必要的。该方法具有成本低通用性好的特点。

1 高速大容量异步FIFO控制器的设计

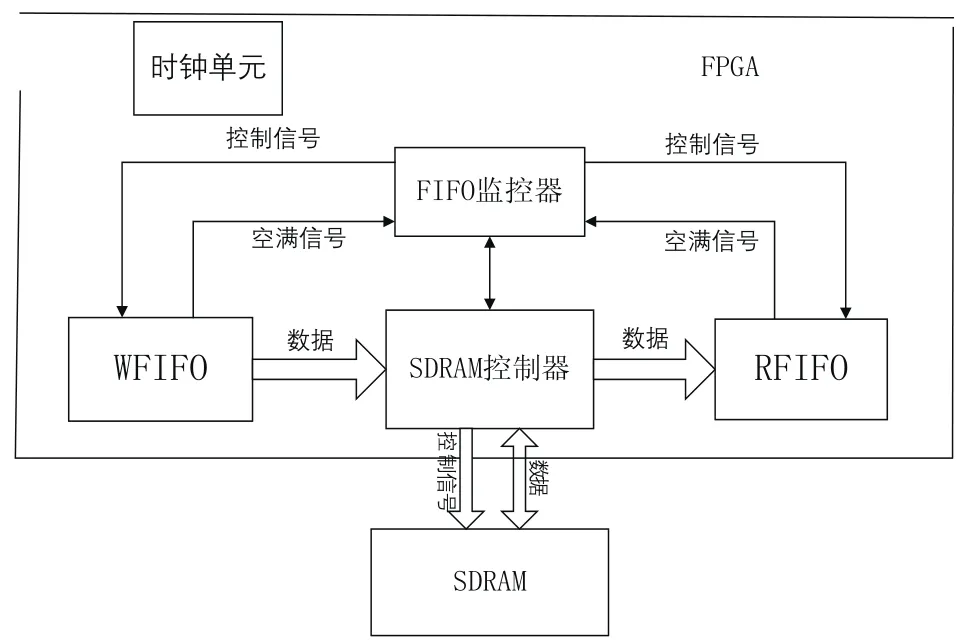

如图1 所示,在FPGA里实现的功能模块有FIFO监控器和SDRAM控制器。FPGA外部时钟采用PCI总线的33MHz,FPGA内部时钟采用锁相环4倍频后产生。两者属于不同时钟域,需要用缓冲器作为输入输出数据的缓存,WFIFO用作向SDRAM写数据,RFIFO用作向SDRAM读数据。

FIFO监控器负责控制WFIFO和RFIFO。当SDRAM控制器处在写命令是,如果WFIFO空,FIFO监控器禁止WFIFO向SDRAM写入数据。当SDRAM控制器处在读命令时,如果RFIFO满,FIFO监控器禁止RFIFO向SDRAM读数据。

图1 高速大容量异步FIFO控制器的设计框图

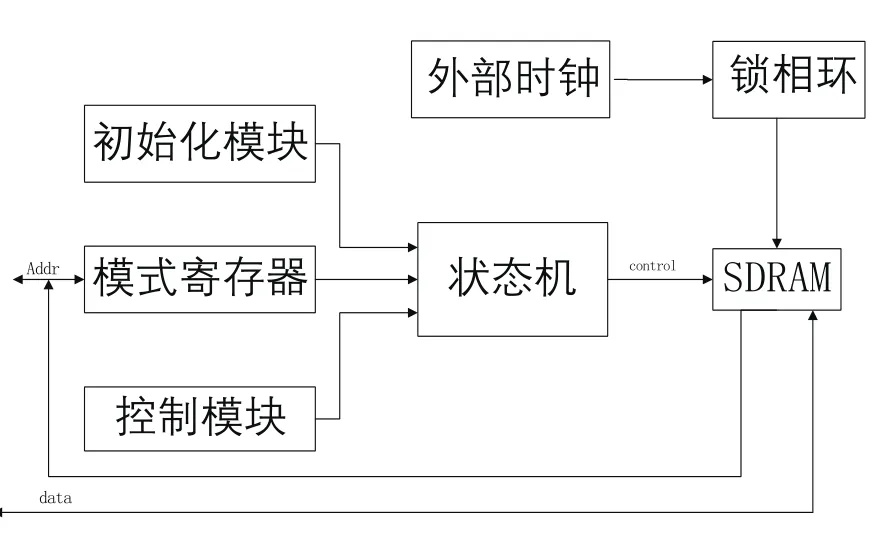

SDRAM控制器包括初始化模块、模式寄存器、控制模块和状态机(如图2所示)SDRAM的接口设计是极其关键的,可根据SDRAM内部操作状态之间的联系,通过状态机来实现接口设计。初始化模块负责SDRAM的初始化,在上电和始终稳定后等待100ms,至少执行一条空操作,然后对所有页执行预充电操作,使所有页处于空闲状态,接着向各页发出两条刷新操作指令,最后发出一个模式寄存器转载命令,使SDRAM有确定的转台进行读写操作。模式寄存器可根据要求对SDRAM在读写操作的工作状态。模式寄存器M0~M2用于规定突发长度,可以为1、2、4、8。M3用于规定突发类型,当M3=0时,突发类型是连续的,当M3=1时,突发类型是交错的。M4~M6用于规定CAS延迟的时钟周期数,可以分为1,2,3。

M7~M8用于规定运行模式。M9用于规定械突发模式,当M9=0时,按实际编程的突发长度存取,当M9=1时,按单个存取单元写入,但可按实际编程的突发长度读出。

状态机有两个作用,一是对各模块发出的命令进行仲裁,使其能够在适当的时间作出适当的操作。二是协调各模块的时序关系。

图2 SDRAM控制器的设计框图

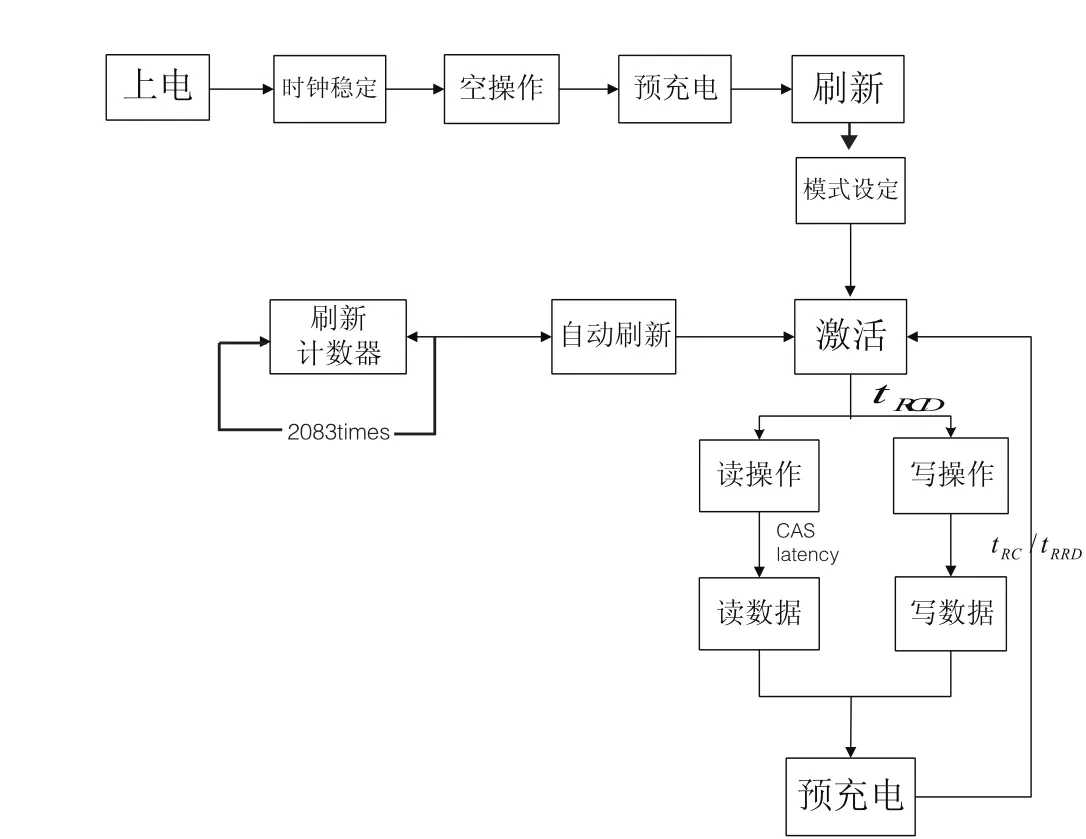

状态机的状态转移如图3所示。

图3 SDRAM的状态转移图

在模式设定之后,BANK和行地址选中需要访问数据所在的具体BANK块和行,状态机对这一行发出激活命令,从激活到读写操作需要经过一个tRCD 的延时。在执行读写操作时,只要状态机通过读写命令选中数据所在行的列地址,就能达到读写具体存储单元的目的。状态机对SDRAM 发出一个读命令后,需要等待一个CAS latency,然后才能读数据;而写操作是实时的,不需要延时,状态机在发出写命令后,就可以对SDRAM进行写操作。SDRAM同时只允许一行地址激活,因此在完成某BAN K/ ROW 的读写操作后,对该BAN K/ ROW进行预充电,然后才能激活下一个BAN K/ ROW。从预充电成功到下一次激活命令成功,如果是在同一个BAN K块,则需要延时tRC,如果是不同的BANK块,则需要延时tRRD。

SDRAM要求在64ms之内对4096行进行刷新,也就是每15.625s对一行进行刷新。FPGA的内部时钟是采用锁相环4倍频后产生,即132MHZ,7.5ns的周期。所以,刷新计数器计到2083时,对SDRAM发出刷新请求才能保证不丢失数据,在设计中将自动刷新设为优先请求,当自动刷新和其他请求同时出现时,状态机仲裁自动刷新优先执行。

2 WFIFO和RFIFO的实现

在设计中需要两个小容量的FIFO来完成跨时钟域通信。采用Altera开发工具Quartus II中内带的基本宏模块来完成。Altera的基本宏模块都是针对其实现的目标期间进行优化过的模块,它们运用在具体的Altera器件的设计中,往往可以使用户的设计性能更高,使用资源更少。

Altera的FIFO基本宏模块可以实现单时钟FIFO(SCFIFO)和双时钟(DCFIFO).SCFIFO就是读写数据均用一个时钟信号。DCFIFO就是读写数据采用不同的时钟。在设计中采用读写不同的时钟,所以采用DCFIFO。如图4是所示的FIFO模型。

图4 WFIFO和RFIFO模型

3 实验与结论

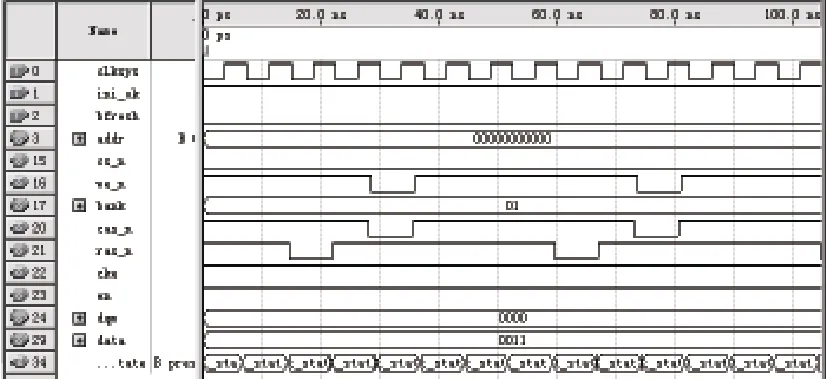

设计采用Altera公司的quartusII进行编程和仿真,编程采用VHDL语言。通过程序调试得到了理想的效果。如图5所示是SDRAM控制器写数据的结果仿真图。

图5 SDRAM控制器写数据的结果仿真图

图5中输入/输出信号如下:

clksys: 系统时钟信号,即电路的工作频率;ini_ok: 初始化是否完成信号,在ini_ok为高时此模块方可工作;

bfresh:刷新请求信号;

cs_n :片选信号,为低电平时逻辑Bank表示选通;

we_n : 写使能信号,低电平为写有效,高电平读有效;

cas_n : 列选通信号;

ras_n : 行选通信号;

cke : 时钟使能信号,本模块此信号一直为高电平有效状态;

en : 读写控制信号,控制sn245和hcun模块,使两个模块分开工作;

addr(10:0): 存储器11位地址线;

bank(1:0) : Bank选择模块;

dqm (3:0) : 数据掩码信号,低电平时数据进行传输;

data(3:0) : 4位数据线 ;

在收到ini_ok=‘1’的信号后,状态机开始工作并进入idle状态,idle状态对SDRAM执行一个空操作,即对存储器发出一个延迟等待的命令。idle状态后进入rowin状态,在rowin状态中同时执行逻辑Bank选择和行有效命令,在rowin状态后是一个延迟等待状态nop1,此状态保证rowin状态的命令完整执行,同时在nop状态将要写入SDRAM的数据送至data引脚。在colin状态执行列有效和写命令,为保证数据的充分写入,在colin状态后是两个延迟等待状态nop2、nop3。在nop3状态判断是否有刷新请求,如果有刷新请求则进入刷新状态bfresh,否则回到idle状态继续执行写过程。如图5所示,这样的状态设计,满足了对SDRAM写数据的时序要求。

对硬件电路进行了调试。再将VHDL程序烧写到FPGA里以后,能够成功测试到SDRAM上的时钟、时钟使能、行选通、列选通、写使能信号,同时能够检测到SDRAM数据端上的数据是程序写入的数字,同时在FIFO的数据端也能检测到这个数字。

[1]王诚,吴继华,范丽珍,薛宁,薛小刚.Altera FPGA/CPLD设计(基础篇)[M].北京:人民邮电出版社,2010:120-132.

[2]郑亚民,董晓周.可编程逻辑器件开发软件Quartus II[M].北京:国防工业出版社,2006:105-109.

[3]陈耀和.VHDL语言设计技术[M].北京:电子工业出版社,2004:100-103.

[4]SCFIFO and DCFIFO Megafunctions User Guider.Altera.2010.

[5]徐欣,周舟,李楠,孙兆林.基于DDR2 SDRAM的高速大容量异步FIFO的设计与实现[J].中国测试,2009,35(6):34-37.

[6]Synchronous DRAM.MICRON.2000.

[7]张奇山,刘安芝,刘希顺.基于FPGA的FIFO设计和应用[J].现代电子技术,2009(1):50-52.

[8]高子旺 顾美康.一种基于FPGA的低复杂度SDRAM控制器实现方法[J].计算机与数字工程,2009(1):194-196.