基于FPGA的高精度时频测量设计与实现

杨丰 , 吉祥

(1 95147部队自动化站,广东 514593;2 93579部队机务大队)

0 引言

对于数字信号的时间和频率测量有很广泛的应用,提高测量精度的方法主要是提高测量时钟,如提高测量时钟一倍的时候就可以提高测量精度一倍,但是很多情况下,器件运行的时钟是受限的,所以测量的精度也会受限[1]。

FPGA具有高速、并行处理的优点,很多FPGA都提供了多个内部的锁相环,每个锁相环可以产生多个不同频率和相位的频率;相对于DSP和ARM等其他数字处理芯片,在频率和相位的控制上具有优势[2]。同时,FPGA是并行处理器件,可以采用多个时钟同时进行测量而互不影响[3-4]。FPGA的这些特点可以很好的被应用于数字信号的时间和频率测量。

1 FPGA高精度时频测量方法设计与实现

该方法主要是在FPGA内部运行时钟受限的情况下,通过对FPGA内部锁相环(PLL)的设置,利用该PLL产生多个相同频率、不同相位的时钟,然后采用所产生的多个时钟对输入的数字信号并行同时进行测量,利用各时钟所测的结果,相应处理后可以获得比FPGA运行时钟高出数倍的测量精度。

1.1 多相位时钟的产生

不同系列的FPGA有不同的锁相环的数量和功能,以EP2C50F484C6为例来描叙锁相环的设置方法[4],该芯片有4个锁相环,每个锁相环可以输出3个时钟信号,这里以设置两个输出时钟为例来说明,具体的设置步骤为:

设置输出的“C0”时钟的频率和相位,由于当时钟速率超过160MHz的时候,该FPGA对编程的要求很高,否则由于FPGA内部时延,可能造成时序错误。为了避免时序错误,如外部输入频率为10MHz时,可以设置“C0”时钟的频率为10倍频100MHz,“C0”时钟的“clock phase shift”为 90°。

设置输出的“C1”时钟的频率和相位,可以设置“C1”时钟的频率也为10倍频100MHz,和“C0”时钟的区别是“C1”时钟的“clock phase shift”设置为 180°。

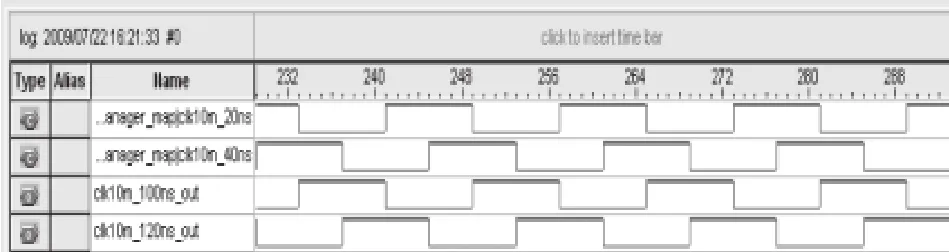

这样产生的两个时钟频率相同,相位相差90°,由于FPGA的锁相环不支持180°以上的相移,所以用锁相环无法直接产生270°和360°相移的时钟。可以采用“C0”时钟和“C1”时钟的分别取反获得270°和360°相移的时钟。这样就产生了4个相位偏差为90°的100MHz的时钟信号,这4个时钟具有一个时钟周期内的连续相位,图1为Quartus II 软件信号采集工具SignalTap 所采的4个相位偏差为90°的100MHz的时钟信号。

图1 多个同频相移时钟的产生

1.2 时频测量的FPGA实现

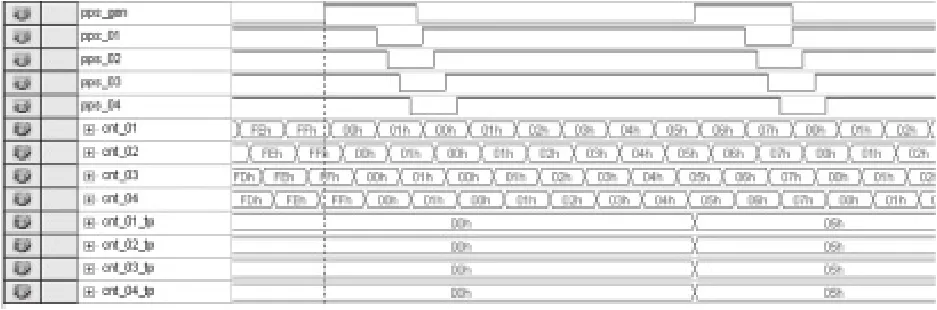

以对一个信号的宽度的测量来说明多相位测量的原理,如图所示“pps_gen”为一个脉冲信号,需要测试两个脉冲上升沿之间的宽度。具体测量的步骤如下所示。

分别用4个不同相位的时钟对“pps_gen”提取上升沿,然后取反产生图2中的“pps_01”、“pps_02”“pps_03” “pps_04”4个计数使能。

对4个计数使能分别用相对应的4个不同相位的时钟进行计数,计数值如图2中cnt_01,cnt_02,cnt_03,cnt_04。

在“pps_gen”第二个上升沿的时候异步提取计数值,4个计数值如图2中cnt_01_tp,cnt_02_tp,cnt_03_tp,cnt_04_tp。

对提取的计数值求平均;由于提取上升沿的时候会有一个时钟的延时,两次提取上升沿需要将平均值加2,同时由于计数值是从0开始的,所以实际的值还需要再加1,如图2所示的计数平均值为5的时候,测量的时宽为8个测量时钟。

图2 测试过程采集的数据

2 测试结果

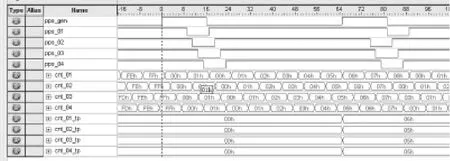

如图3所示,“pps_gen”的上升沿间距为8.125个时钟宽度时,测量值为(6+5+5+5)/4+3=8.25个时钟宽度;图4所示,“pps_gen”的上升沿间距为8.25个时钟宽度时,测量值为(6+5+5+5)/4+3=8.25个时钟宽度。表1为实测数据,测量的精度达到0.25个时钟,比直接用该时钟测量的精度提高了4倍;统计的平均误差为0.10个测量时钟。

图3 “pps_gen”的上升沿间距为8.125个时钟宽度时的测试数据

图4 “pps_gen”的上升沿间距为8.25个时钟宽度时的测试数据

表1 不同输入信号宽度时的测试数据

3 设计中需要注意的问题

(1)避免毛刺现象

为了避免毛刺现象的出现,FPGA运行的时钟不能太高;同时在编程的时候尽量用时钟同步的方式处理信号[5],上面的测量例程中,除了提取测量值用pps_gen的上升沿异步提取外,计数器的计数都用的是时钟同步计数[6]。

(2)FPGA多个锁相环的利用

很多FPGA都提供多个锁相环功能,如果能够利用多个锁相环产生更多的时钟进行测量,可以更好地提高精度,但是需要注意下面的问题,首先是两个锁相环不能用同一个管脚的输入时钟,需要用通用IO输出FPGA后再输入FPGA的时钟管脚作为第二个锁相环的输入;第二是内部锁相环不能级联(也就是说不能用第一个锁相环的输出作为第二个锁相环的输入),第三是需要很好地测量两个锁相环的相位差,以保证不同锁相环产生的时钟的相位连续性。

由于FPGA具有多个内部锁相环,可以产生多个同频、相移的时钟;同时FPGA可以并行处理,这样就可以采用同频、相移的多个时钟分别对输入信号进行测量就能够得到相当于数倍测量时钟的测量结果,使得测量精度提高数倍。如果采用ALTERA stratixII系列的FPGA[7-8],一个锁相环可以产生5个不同相移的时钟,再利用取反所产生的时钟,可以使得测量精度提高10倍,比如,FPGA采用100MHz的最高时钟,对时间间隔的测量精度为10ns,当采用多相时钟后,测量精度可以达到1ns,提高了一个数量级。和其他测量方法比,该方法属于实测数据,更为可靠;实现也更为简单。

{1} 李虎成.基于FPGA的频率周期及相位差测量的多功能计数器的实现[J].电子测试,2009(1):44-47.

{2} 钱时祥, 江炜宁, 周增建.一种基于DSP的高精度频率测量方法[J].电测与仪表, 2009,46(4):17-20.

{3} 褚振勇,翁木云.FPGA设计及应用[M].西安:西安电子科技大学出版社,2003: 45-51.

{4} Altera Corporation.Cyclone II device handbook, http://www.altera.com.cn/support /devices/cyclone 2/dev-cyclone 2.html.2007: 185-201.

{5} 夏文鹤,青小渠,刘莉.基于多路移相时钟的瞬时测频模块设计[J].电子测试,2008(6):69-73.

{6} 陈志刚.VHDL语言在电路设计中的优化[J].电子测试,2008(9): 75-77.

{7} Altera Corporation.Stratix II device handbook, http://www.altera.com.cn/support/devices/stratix2/dev- Stratix 2.html.2007: 75-88.

{8} 谢登科,徐端颐.基于数字移相的高精度脉宽测量系统及其FPGA实现[J].电子技术应用, 2004(1): 27-29.