冗余金属对互连线电容特性的影响

杨 飞, 何晓雄, 陈 岚

(1.合肥工业大学 电子科学与应用物理学院,安徽合肥 230009;2.中国科学院 微电子研究所,北京 100029)

0 引 言

随着超大规模集成电路(VLSI)沿着摩尔定律的不断发展,集成电路的集成度高达数亿元器件/片[1]。为降低RC延迟,IC结构采用了立体化和布线多层化[2]。多层立体结构及纳米级特征尺寸对材料表面平坦化提出了极高的要求,如果平坦化效果不好,则随着层数的增加,表面的不平坦度累积效果显著[3]。到目前为止,唯一能实现全局平坦化的关键工艺技术是化学机械研磨(Chemical Mechanical Polishing,简称 CMP)技术[4-6]。在CMP过程中,金属密度的不均匀导致金属厚度的起伏,产生碟形、磨损,因此需要进行冗余金属填充来调节金属的密度,使其达到一致,以此来改善金属表面的平坦性,但另一方面,冗余金属的填充会增加互连电容,带来信号延迟以及功耗增加等一些问题[7,8]。

目前,对于冗余金属填充的研究结果有以下几个方面:

(1)在低频情况下,冗余金属对电容的影响可以忽略,但是在高频情况下,尤其当频率超过50 GHz的时候,电容会有比较明显的增加[9]。

(2)冗余金属离信号线越远,对电容的影响就越小,相反,对信号线电容的影响则越大。因此,增加距离可以有效地降低冗余金属的影响[10]。

(3)冗余金属的尺寸越大,互连线之间的相互影响也越大,相似地,冗余金属与互连线的距离越小,它们之间的互相影响就会越强[11]。

(4)对于填充浮空冗余金属行数和列数:当行数确定时,列数越多,耦合电容越小;当列数确定时,行数越少,耦合电容越小。

目前,国内外学者对于冗余金属与信号线的对应边长、冗余金属之间的距离以及冗余金属交错排列时对互连线间耦合电容影响方面的研究较少,因此本文主要考虑以上3个方面对互连线间耦合电容的影响。通过实验可以得出:在面积一定的条件下,冗余金属与互连线的对应边长越长,与互连线的距离越远,垂直于信号线方向的冗余金属的个数越多,冗余金属对互连线耦合电容的影响就越小。

1 提取工具的选择

当今主流的深受广大设计公司和集成电路制造厂商接受的2.5D寄生提取工具,如Synopsys公司的StarRCXT工具和MentorGraphic公司的Calibre系列工具,在提取门级和晶体管级寄生参数上,速度和精度都很出色,作为最后交给集成电路制造厂商数据的确认工具应用广泛,逐步成为业界标准,特别对缩短新型芯片从构想到流片的时间做出了特殊贡献。如利用这些工具在提取50万门级全芯片的寄生参数时,所耗时间很短,只相当于Synopsys公司RaphaelXT全3D仿真工具提取几十条金属(其中有浮空金属)的时间。RaphaelXT耗时长,因为考虑到了3D的版图和浮空金属的影响。当今考虑浮空金属对耦合电容影响的快速提取方法仍为研究热点,由于对提取时间的限制,2.5D寄生参数提取工具对浮空金属的计算结果难以达到准确,特别是对应特殊图形冗余金属时,其提取的耦合电容会出现显著偏差,所以在研究重点为浮空冗余金属时,参数提取工具最好选用为 3D仿真工具,如 Raphael和QuickCap。

2 实验方案和结果分析

在本文中,使用Synopsys的电容提取工具Raphael进行电容的提取,Raphael中的 RC3使用有限差分方法,可以得出三维的电容、电场、电压、电流密度和热分布,模型精确,所提取的结果也被看作准确值。在实际的冗余金属填充中,一般要使密度达到某一定值,即总密度达到某一定值,因此设定如下实验方案。

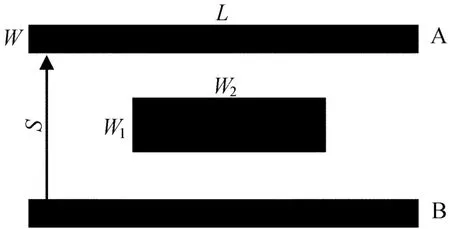

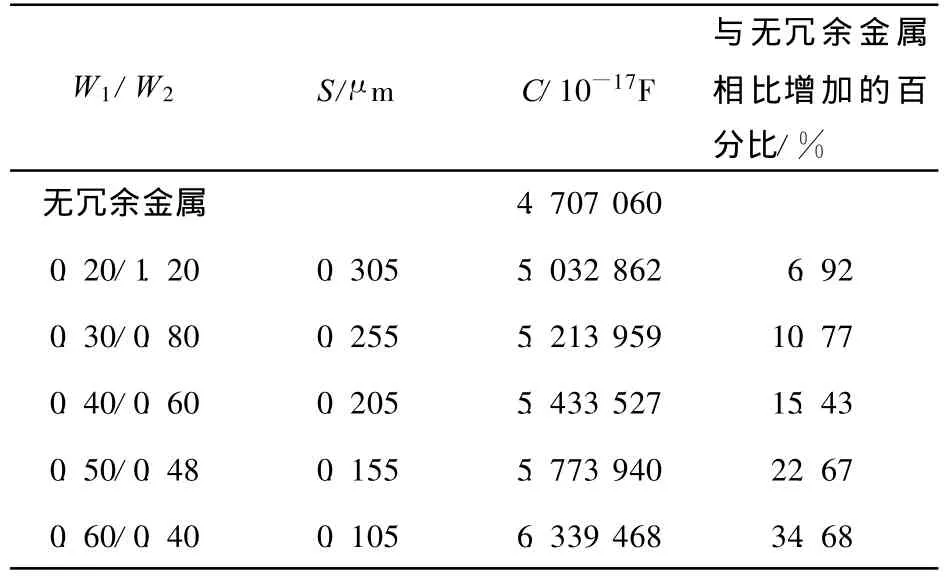

方案 1:设定信号线A与B的宽W=0.09μm,长 L=1.5μm,信号线之间的距离 S=0.81μm,冗余金属的尺寸为 W1=0.2 μ m,W2=1.2 μ m,如图1所示。保持面积一定,只改变冗余金属的宽长比(W1/W2),分别为 0.30/0.80、0.40/0.60 、0.50/0.48 、0.60/0.40 。

图1 冗余金属尺寸示意

A与B之间的耦合电容(一),见表1所列。

表1 A与B之间的耦合电容(一)

从表1中可以发现,当冗余金属的面积保持一定的情况下,改变了冗余金属的宽长比,即改变了冗余金属与信号线之间的距离,使冗余金属与信号线A和B之间的距离越来越小,会引起A与B的耦合电容的巨大变化,且变化幅度越来越大,变化越来越快,最大的变化幅度已超过30%。因此,在本实验的条件下,进行冗余金属填充后密度为28%,在进行冗余金属填充时,应使冗余金属与信号线之间的距离不小于0.255 μ m,这样可以使冗余金属对信号线之间耦合电容的影响控制在10%以内。

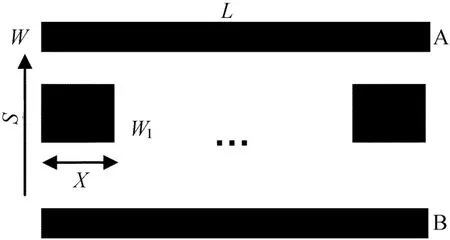

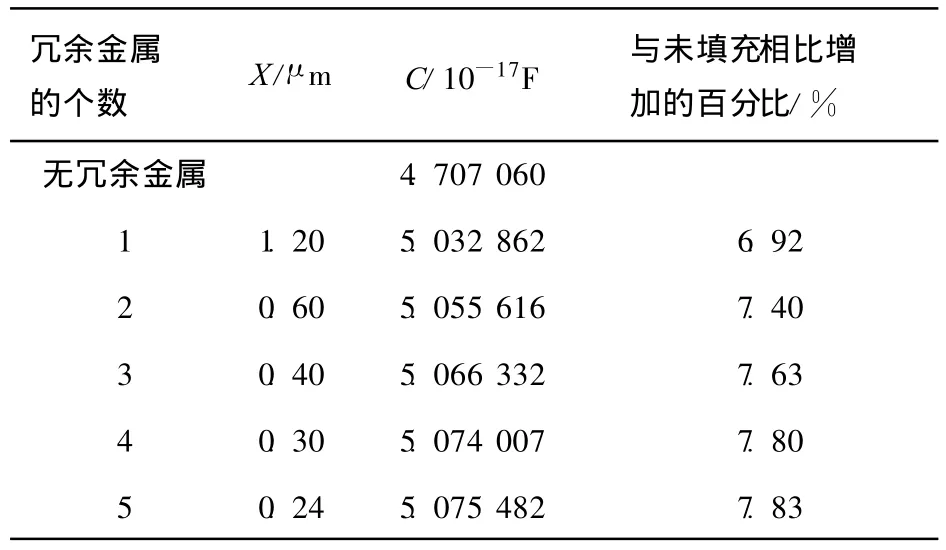

方案 2:设定信号线A与B的宽W=0.09μm,长L=1.5μm,信号线之间的距离为0.81μm,将尺寸为0.20μm/1.20μm的冗余金属左右平分为 2份、3份、4份和 5份,如图2所示。

类似地,将宽长比为0.30/0.80、0.40/0.60、0.50/0.48以及0.60/0.40的冗余金属分别平均分为2份、3份、4份和5份,并分别进行信号线之间耦合电容的提取,可得到如图3a和图3b所示的数据。

图2 冗余金属分为 N份

图3 A与B之间的耦合电容

从图3a可以看出,在面积一定的前提下,改变了冗余金属的宽长比,即改变冗余金属与信号线之间的距离,会引起A与B的耦合电容的巨大变化,且变化幅度越来越大,变化越来越快,最大的变化幅度已接近60%。

从图3b可以看出,保持冗余金属与信号线之间的距离不变,冗余金属的总面积不变,只改变冗余金属的数目,将冗余金属左右平分,同样会引起信号线A与B的耦合电容发生变化,但与改变冗余金属的宽长比的结果相比,A与B的耦合电容的增加趋势明显减缓,且最大的增加幅度不超过30%。

因此可以得出结论:在冗余金属的总面积保持不变,冗余金属与信号线之间的距离一定的情况下,对于信号线之间耦合电容的影响,冗余金属与信号线之间的距离因素要比冗余金属的数目因素的影响大。因此在实际应用中,应优先考虑冗余金属与信号线之间的距离这个因素,然后再考虑冗余金属的数目的影响,在必要时可以适当地牺牲数目这个因素。

A与B之间的耦合电容(二),见表2所列。

表2 A与B之间的耦合电容(二)

从表2可以看出,当冗余金属与信号线A和B之间的距离和对应边长均不改变,只改变冗余金属的个数,将冗余金属左右进行平分,A与B之间的耦合电容也是在不断增加,当冗余金属的个数为5时,信号线之间的耦合电容比没有冗余金属时增加幅度已超过7%。因此,在本实验的条件下需要进行冗余金属填充时,当冗余金属的其它条件固定的时候,应使冗余金属的个数为1,这样可以使冗余金属对信号线之间耦合电容的影响最小,也就是说,在平行于信号线的方向上,使冗余金属的个数最少。

方案 3:设定信号线A与B的宽W=0.1μm,长L=1.5μm,信号线之间的距离为1.5μm,冗余金属的宽长比为0.1/0.3,改变冗余金属的摆放方式,使冗余金属的长短边分别对应信号线,在长短边分别对应信号线的时候,冗余金属与信号线之间的距离一定,且冗余金属在不同摆放方式时均匀摆放,如图4所示。

图4 长边、短边对应信号线和信号线之间的耦合电容

从图4可以看出,当其它条件均不改变,仅改变冗余金属与信号线对应方式时,长边对应信号线时信号线之间耦合电容比短边对应信号线时要小5.25%,虽然短边对应信号线时,冗余金属与信号线之间对应边长减小,但同时冗余金属之间的相互距离也减小,这说明在对耦合电容的影响因素中,距离比相互之间的对应边长的影响要大,因此在实际的填充时,应优先考虑冗余金属与信号线以及冗余金属之间的距离这个因素,然后再考虑相互之间的对应边长。

3 结 论

(1)当冗余金属的面积一定的时候,应使冗余金属与信号线的对应边长尽量长,而使冗余金属与信号线之间的距离尽量远。

(2)冗余金属的总面积保持不变,冗余金属与信号线之间的距离一定的情况下,应使冗余金属的数目最少。

(3)在实际的冗余金属填充时,应优先考虑距离这个因素,必要时可以适当牺牲冗余金属与信号线之间的对应边长。

[1]Kahng A B.Design challenges at 65 nm and beyond[C]//Design,Automation&Test in Europe Conf and Exhibition,2007:1-2.

[2]Steigerwald J M,Murarka S P,Gutmann R J.Chemical mechanical planarization of microelectronic materials[M].New York:Wiley,1997:5-7.

[3]Lee K Y,Wang T C,Chao K Y.Post-routing redundant via insertion and line end extension with via density consideration[C]//P roc of ICCAD,2006:633-640.

[4]刘玉岭,檀柏梅,张楷亮.超大规模集成电路衬底材料性能及加工测试技术工程[M].北京:冶金工业出版社,2002:65-66.

[5]刘玉岭,檀柏梅,张楷亮.微电子技术工程:材料、工艺与测试[M].北京:电子工业出版社,2004:125.

[6]Kahng A B,Samadi K,Sharma P.Study of floating fill impact on interconnect capacitance[C]//7th International Symposium on Quality Electronic Design,2006:691-696.>

[7]Tichy J,Levert J A,Shan L,et al.Contact mechanics and lubrication hydrodynamics of chemical mechanical polishing[J].Journal of the Electrochemical Society,1999,146(4):1523-1528.

[8]Tsuchiya A,Onodera H.Effect of dummy fills on high-frequency characteristics of on-chip interconnects[C]//IEEE Workshop on Signal Propagation on Interconnects,2006:275-278.

[9]Kima Y,Petranovicb D,Sylvestera D.Simple and accurate models for capacitance increment due to metal fill insertion[C]//ASP-DAC'07 Proceeding s of the 2007 Asia and South Pacific Desig n Automation Conference,2007:456-461.

[10]王沛东,郭 炜,谢 憬.集成电路设计中利用填充金属优化压降的方法[J].电子技术,2008,(6):31-34.

[11]He Lei,Kahng A B,Tam K H,et al.Variability-driven considerations in the design of integ rated-circuit global interconnects[C]//Proc Int VLSI/ULSI Multilevel Interconnection Conf,2004:214-221.