机载高分辨率遥感图像实时压缩系统研究

王庆元 王 琨 武文波

(北京空间机电研究所,北京 100076)

1 引言

随着可见光和红外传感器技术的不断发展,机载遥感成像的分辨率日益提高,从而导致图像数据量急剧增加,必须通过压缩技术才能解决图像数据的有效存储问题。为了满足用户及时获取和分析图像数据的要求,对机载遥感成像实时压缩处理能力也提出了越来越高的要求。受机载应用环境的限制,机载图像实时压缩系统也必须符合体积小、功耗低的要求。本文对主要的5种图像压缩系统架构进行了分析比较,并针对机载环境的需要提出了一种高分辨率遥感图像实时压缩系统。在该系统中,实现了JPEG-LS无损和近无损图像压缩算法,在系统工作50MHz时钟下,其对图像压缩能力超过个人计算机(Personal Computer,PC)CPU为Pentium4,主频为1.8GHz的处理能力。

目前,图像压缩系统主要包括以下5种主要架构:

(1)基于高性能通用处理器的图像压缩系统

大家最为熟悉且经常使用的是PC机和工作站。目前,Pentium 4处理器的主频已经超过3GHz,它拥有丰富的高速缓存资源,在芯片组的配合下可以连接400MHz以上的双数据速率(Double Date Rate,DDR)内存和大容量硬盘等外设。其主频高、拥有的资源丰富,综合处理能力较强,算法适应性非常强。目前,通用处理器内部也增加了适应图像压缩的相关部件和指令,非常适合对海量的、实时性要求不高和人机交互频繁的图像处理。缺点是PC机和工作站是通用处理器,并不是专门针对图像处理而设计的,其体系结构并不能完全满足图像压缩的需要,而且体积庞大,功耗高达几十瓦,因此,使用时需要散热片和风扇降温。另外,由于PC机和工作站的主频较高,这对其电气特性和时序配合要求非常严格,在温度变化剧烈的或者有强烈振动和冲击环境中,容易导致电气特性和时序配合错误,不能满足机载环境中可靠性工作的要求。

(2)基于专用集成电路(Application Specific Integrated Circuit,ASIC)压缩芯片的图像压缩系统

最为常用的专用ASIC芯片是基于联合图像专家小组(Joint Photographic ExpertsGroup,JPEG)压缩算法的。具有代表性的是美国Analog Devices公司生产的JPEG 2000压缩芯片ADV212,该芯片不仅可以处理静态图像,而且仅仅联用两片芯片就可以实时压缩高清晰电视信号。由于专用ASIC芯片是针对某种图像压缩标准专门设计的,其处理能力强,执行效率高,功耗也非常低,但其缺点是该类芯片是针对特定算法和限定图像格式设计的,并且其接口也是固定的,而在实际机载环境中对图像压缩需求不仅千变万化,而且图像的输入和输出格式也各式各样,使用专用ASIC芯片的压缩系统适应性较差。

(3)基于嵌入式处理器的图像压缩系统

以ARM和Xscale为代表的嵌入式处理器,它们已经在高档掌上电脑(Personal Digital Assistant,PDA)和智能手机上得到广泛使用,用于处理图像、视频等多媒体信息。由于这类处理器属于精简指令集计算机(Reduced Instruction Set Computer,RISC)体系结构,指令精简,加上独到的设计,从而保证其非常低的功耗。缺点是内部资源有限,并行处理单元少,能完成小图像的压缩处理,但对于高分辨率图像实时压缩任务则无法胜任。

(4)基于数字信号处理器(Digital Signal Processor,DSP)的图像压缩系统

目前,最先进的面向图像和视频处理的DSP,如TI公司生产的720MHz的TMS320DM642,其计算能力高达5 760×106指令/s。TI公司的开发环境CCS(Code Composer Studio)中的C编译器功能很强,经过C编译器编译后的程序的执行效率最高可相当于汇编语言的70%~80%。DSP一般适合对基于离散余弦变换(Discrete Cosine Transform,DCT)和霍夫曼编码的图像和视频进行处理,但不适合处理基于像素的无损压缩、基于大的图像块的小波变换、位平面预测和算术编码。DSP内部的运算单元不多于8个,在实际使用中,还往往会对算法进行大量的调整和优化,最终同时工作的单元也仅有2~3个,效果很不理想。对外接口也只有面向存储器的EMIF(External Memory Interface)接口和串行低速的多通道缓冲串口(Multi-channel Buffered Serial Port,McBSP),能接收图像数据的通道数目也会受到限制。在实际开发中,导致DSP效率不高的原因之一是在数据接收和预处理上的效率较低。另外,主频过高也是影响它在机载环境中工作可靠性的因素之一。

(5)基于现场可编程门阵列(Field Programmable Gate Array,FPGA)的图像压缩系统

目前,最先进的FPGA门数高达上千万,还嵌有多个DSP或ARM或PowerPC嵌入式处理器,支持最新的高速串行总线(如PCI express、Rapid I/O等),芯片内部可以设计多个并行处理子系统,每个子系统又可以拥有多个运算单元。使用FPGA进行图像压缩,其处理速度和功耗方面都仅次于ASIC芯片。缺点是设计难度较大,要充分考虑时序配合、功耗和电磁干扰(Electromagnetic Interference,EMI)等问题,逻辑仿真和调试工具与PC机环境中的软件调试工具相比功能也弱得多。但是随着电子电路日趋模块化和标准化,很多公司研制出了独立于硬件的IP核(Intellectual Property core是指用于产品应用专用集成电路或者可编程逻辑器件的逻辑块或数据块),而且电子设计自动化(Eletronic Design Automation,EDA)工具功能也日益强大,因此,在单片FPGA上实现复杂的图像压缩系统越来越普遍。

基于FPGA的图像压缩系统具有如下特点:

1)在单片FPGA上可以汇集多种图像压缩算法,能更好地适应不同的压缩需要,且算法还可以进行在线修改;

2)FPGA内部有大量的寄存器、丰富的存储资源和高速的全局时钟以及互连路径,能实现更多的独立运算单元,执行并行度更高,可以提供更为强大的图像处理能力;

3)接口非常丰富,通过并行接口可以非常方便地与DDR、同步动态随机存储器(Synchronous Dynamic Random AccessMemory,SDRAM)和先进先出存储器(First-In First-Out,FIFO)互连,也可以提供低电压差分信号(Low Voltage Differentail Signal,LVDS)等串行接口与其它元件或系统互连,以IP核实现PCIexpress等总线接口与主机交互数据,还可以提供更多输入输出通路,同时处理多路图像数据流;

4)可以嵌入图像压缩的各个功能IP核,如量化IP核和霍夫曼编码IP核等;

5)可以把图像系统的主要部分集成到单片FPGA,从而减少印刷电路板(Printed Circuit Board,PCB)板面尺寸和布线数,使用FPGA还可以实现工作时钟较低,而图像压缩的速度、品质与高性能CPU和DSP压缩速度相当,且功耗更低。

相比其它4种压缩系统,基于FPGA的图像压缩系统具有功耗低、体系小,图像压缩处理能力强,算法的实现和更新灵活等诸多优点。因此,本文基于FPGA来设计和实现机载高分辨率图像压缩系统。

2 硬件平台的总体结构

本文研究面向高分辨率图像的实时压缩系统,该系统既要满足当前图像压缩算法要求和外接端口的需要,又要预留出充足的逻辑资源和端口扩展能力以适应未来发展的要求,同时还要考虑到系统本身的性价比。

本文提出的面向高分辨率图像实时压缩系统的硬件平台总体结构如图1所示。该平台的逻辑控制和图像数据处理由XILINX公司生产的高性能片FPGA XC2V1500负责完成,它通过2个物理上相互独立的单向FIFO与PCI9054进行双向数据交互,使用PCI9054实现与外设部件互连(Peripheral Component Interconnect,PCI)总线的通信功能,压缩后的数据可以通过PCI总线传输到固态硬盘(固盘)上存储,也可接收固盘通过PCI总线传输的图像数据到FPGA进行处理。该系统以16路并行LVDS差分输入接收图像数据,经压缩编码后的数据通过4路LVDS差分方式输出。

该系统的核心是XC2V1500芯片,它具有很多先进的特性和丰富的内部资源,如:系统门数达150万门,内部时钟高达420MHz,支持19种单端和6种差分I/O信号标准,支持高达840Mbit/s共模驱动的LVDS I/O、总线LVDS和电流驱动的LDT I/O,最大可用I/O数为392。因此,使用XC2V1500作为压缩算法和接口逻辑的载体,既满足了现在的需要,又能保障平台的扩展能力。

该平台的Compact PCI接口可以满足与其它功能模块进行数据通信的要求。Compact PCI接口的电气性质符合32位的33MHz的PCI总线标准。图像数据输入采用是符合EIA-422/485标准的8位并行差分通道,该接口适合高速远距离连接,而且是差分输入,抗干扰能力强,适合在机载环境中应用。压缩数据可以通过高速的串行LVDS总线输出到机载数传设备。

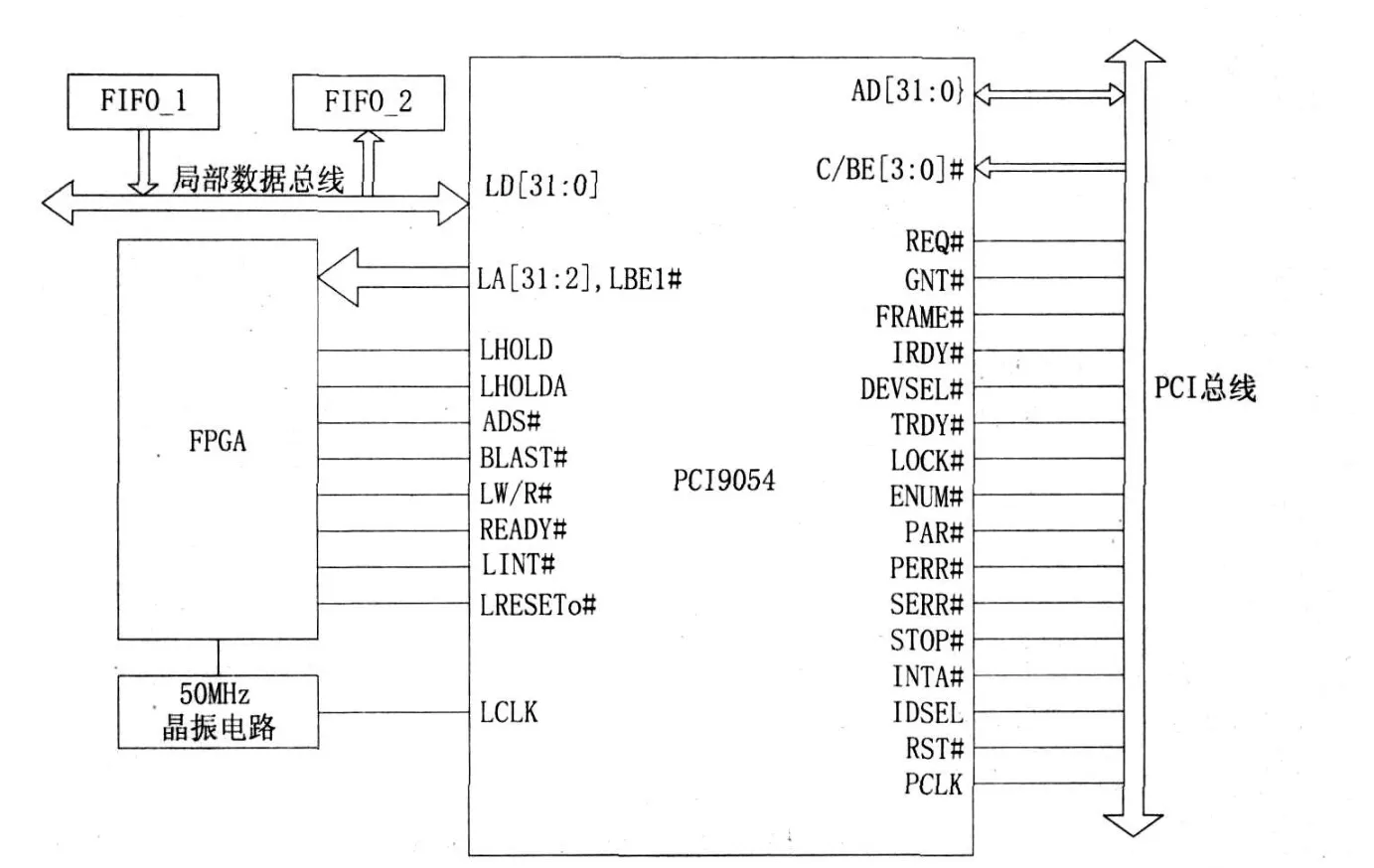

PCI总线接口采用PLX公司生产的高性能PCI9054,它符合PCI2.2标准的32位的33MHz总线接口芯片,支持3.3V和5V的PCI总线[1]。PCI9054的PCI总线端可以和整个系统PCI总线通信,平台可以直接和PCI9054的局部总线端进行通信,本文通过2个单向传输的高速同步FIFO组成一个逻辑地址空间实现与PCI9054的局部总线端相连。PCI9054的局部总线由32位地址线、32位数据线和若干控制信号组成,局部总线的工作时钟最高为50MHz。PCI9054具有直接存储器访问(Direct Memory Access,DMA)、主控(initiator)和从属(slave)等3种工作方式。在DMA方式下,PCI9054是PCI总线和局部总线的主控器,当主机端或板卡的CPU启动DMA时,PCI9054独立完成传输过程,这样可使PCI总线实际传输速率接近100Mbyte/s峰值速度。具体PCI和局部总线接口逻辑图如图2所示。

图1 高分辨率图像实时压缩的硬件平台总体结构

图2 PCI9054实现的PCI和局部总线接口逻辑图

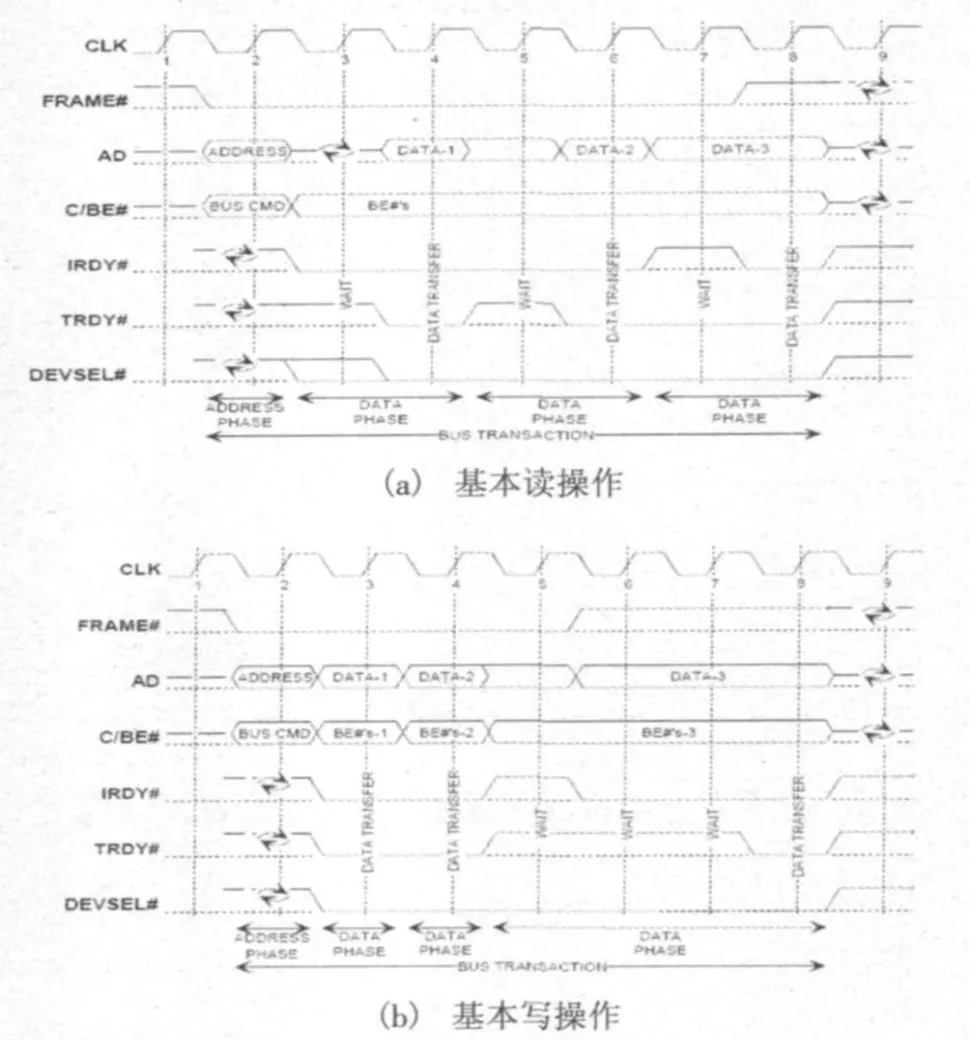

在PCI总线接口端,PCI9054通过REQ#信号有效请求使用PCI总线,PCI总线的主控设备收到REQ#信号后,发出GNT#信号有效放弃控制权,并将控制权交给PCI9054。FRAME#有效表示一次总线传输的开始,IRDY#有效表示主设备已经准备好,TRDY#有效表示从设备可以完成数据传输,DEVSEL#有效表示总线的从设备已经选中[2]。PCI总线的基本读写时序如图3所示。图3中FRAME#是低电平有效的帧周期信号,并由当前主设备驱动;AD是地址数据多路复用信号线;C/BE#是总线命令和字节使能多路复用信号线。

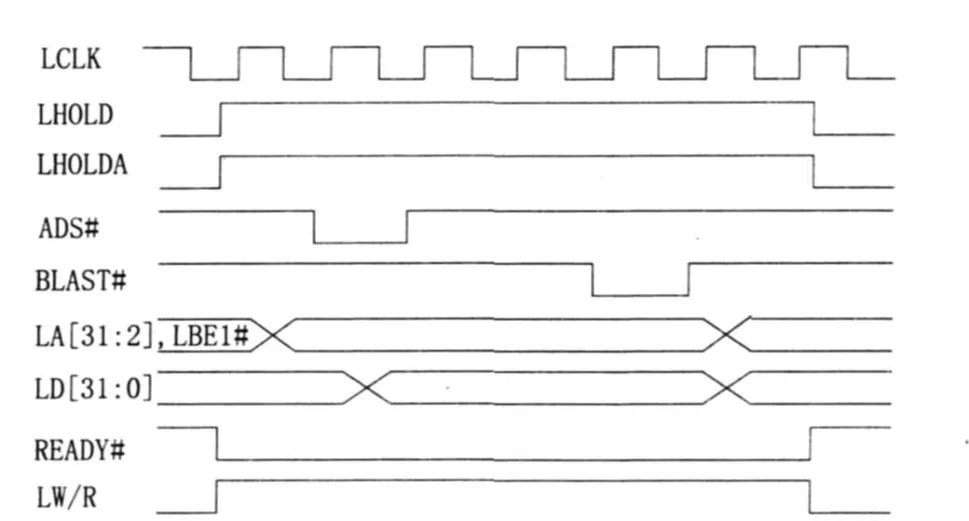

图4是局部总线的写操作时序关系图。在局部总线端,PCI9054通过LHOLD信号有效请求使用局部总线,局部总线的主控设备收到LHOLD信号后,发出LHOLDA信号有效放弃控制权,并将控制权交给PCI9054,在本文介绍的平台中PCI9054一直是局部总线的主控器,故LHOLD和LHOLDA在FPGA内部互连。

PCI9054有C,J,M三种局部总线接口方式,分别用来实现与i960,PowerPC和FPGA处理器的无缝交互。本平台中PCI9054将与FPGA连接,于是通过将PCI9054的管脚mode1和mode2拉低的方式将PCI9054设置为C接口方式,并且将局部总线也设置成地址线和数据线不复用方式。通过将PCI9054的管脚bigendian设置为低,使得局部总线为小印地安字节(先发送低字节再发送高字节的)顺序简化和FIFO的互连。通过表1配置PCI9054相应的寄存器使得局部总线为32位数据线,burst猝发传输方式可以使得PCI的传输能力发挥更为充分。LAS0BA和LAS0RR分别用于配置局部地址空间0的起始地址和空间大小。

图3 PCI总线基本读写操作时序图

图4 局部总线写操作时序关系图

表1 9054寄存器配置

由于Linux操作系统具有开源、可以根据实际需要合理裁减,以及较高的实时响应能力等特点,嵌入式系统普遍选择Linux作为其操作系统。Linux操作系统可以将硬件设备看成特殊的文件,设备文件不占用文件系统的数据空间,仅仅作为设备驱动的访问入口点。访问设备与普通文件操作一样,使用open和release打开和关闭设备文件,write和read访问硬件设备。另外,在Linux操作系统下,可以选择在配置和编译内核时将驱动程序加入,也可选择编译成可动态加载的模块,我们选择了后者保持内核的稳定性和系统的灵活性,用insmod和rmmod命令进行加载和卸载模块。驱动程序具体步骤可以参阅文献[3]。一般设计者往往只注意到DMA独立与CPU进行传输,而且速度非常快,但是忽视了每次DMA配置所花费的时间(大约为0.5ms),在连续数据传输情况下,DMA配置耗费的时间就会严重影响PCI传输能力的发挥。PCI9054提供了2个独立的DMA通道,这样就可以利用一个DMA通道的传输时配置另外一个DMA通道,从而使PCI实际传输数据能力超过82Mbyte/s。表2是进行DMA传输时有关的寄存器设置情况。

表2 DMA传输时相应寄存器设置(x取0或1)

3 基于FPGA的无损和近无损压缩算法的设计和实现

3.1 适应JPEG-LS简单有效的位率控制策略和抗误码设计

JPEG-LS是静态图像的无损和近无损压缩国际标准[4-5]。JPEG-LS算法的核心是HP实验室提出的低复杂度无损图像压缩(LOw COmplexity LOssless COmpression for Images,LOCO-I)算法[6]。JPEG-LS算法框图如图5所示。

图5 JPEG-LS算法框图

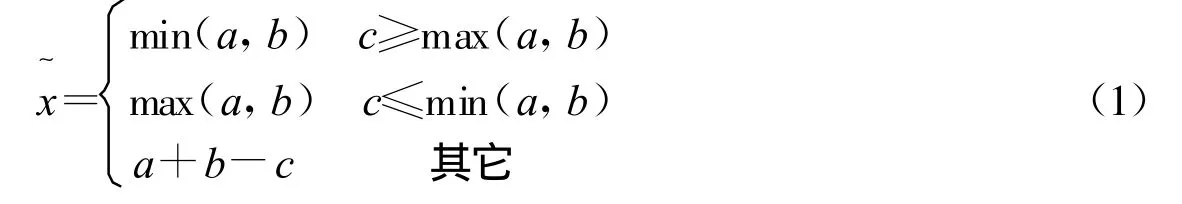

JPEG-LS使用a,b,c和d位置的像素值,利用下面的公式进行一个简单的垂直和水平的检测计算就得到x处像素的预测值 (x,a,b,c和d既代表其位置又表示所在处的像素值)。

根据式(1)可以得到x的实际值和预测值的残差值。残差值的概率分布统计意义上符合几何分布,而Golomb码对于几何分布是最优的编码方法。通过式(2)~(4)可计算得到g1、g2、g3这3个梯度,由这3个梯度值确定对x编码的上下文。

在具体实现时由于整数值的约束和上下文预测的偏差导致存在偏离,实际编码的是经过修正的残差值。

对于像素值都一样的低熵区域,由于Golomb码至少是一个二进位,对这些区域编码会造成较大的编码冗余,所以引入了游程编码。JPEG-LS通过改变量化值near来实现近无损图像压缩。

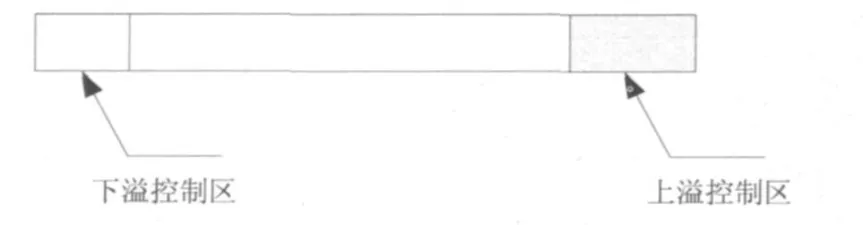

JPEG-LS输出缓冲区如图6所示。因为该平台压缩速度大于图像数据的输入速度,所以在输入缓冲区不存在溢出问题,而在LVDS输出端,为了在恒定的带宽下使图像质量尽量好,同时确保不发生上溢和下溢现象,需要合理的位率控制策略来实现图像质量和缓冲区充满度的平衡。因此,我们设计了如下位率控制策略(α为输出缓冲区的充满度;q是量化步长,其中qinit是初始量化步长;near是当前量化值;near-new是调整后的量化值;β1,β2是防止下溢的调整因子,β1<β2;β3,β4是防止上溢的调整因子,β3<β4:

图6 输出缓冲区示意图

1)初始化:near=qinit。

2)如果40%<α<60%时,near=qinit。

3)防止下溢:

当 α<30%时,near-new=near-β1q;当 α<15%时,near-new=near-β2q。

4)防止上溢:

当 α>70%时,near-new=near+β3q;当 α>85%时,near-new=near+β4q。

通过LVDS输出的数据是通过机上的无线数据传设备传到地面接收站的,由于无线信道的误码率比较高,需要采取一定抗误码措施。以n行图像数据作为一个条带,在条带间插入再同步码,各个条带编码是独立的,这样可以使误码的影响限制在每个条带之间,实际使用上对图像的峰值信噪比(Peak Signal-to-Noise Ratio,PSNR)值影响也很小(小于1dB)。

3.2 JPEG-LS算法的工程实现

在FPGA上高效实现JPEG-LS算法必须充分提高算法各环节的并行和流水。主要的并行和流水操作包括:

1)图像数据输入和压缩输出的并行执行;

2)各条带编码操作的并行执行;

3)条带内预测和熵编码的流水执行。

在FPGA实现压缩算法时,采用同步时序设计,通过适当划分各个模块,使其规模控制在5 000门以内,对关键时钟和重要的信号建立合适的时间约束。在状态机设计用格雷码表示各个状态,消除状态转换中可能出现的毛刺。

在FPGA中实现了作为输入缓冲的双端口RAM、JPEG-LS算法及控制局部总线、读写FIFO、自检等时序逻辑,共使用了57万系统门,约占系统总门数的38%,其中双端口RAM占80%以上,如果实现EZW和SPIHT等更为复杂的图像算法,双端口RAM这部分资源可以复用。

4 试验结果

本文对压缩系统中PCI总线传输能力进行了测试。试验条件是:压缩系统的主时钟频率为50MHz,完成32位数据连续传输任务。数据经过FIFO,通过PCI9054写到主板内存,并从主板内存写到FPGA进行2个方向的DMA不间断传输,用于对PCI总线实际传输速率进行测试。试验结果表明,PCI有效数据传输速度稳定在82Mbit/s以上,验证了硬件设计、驱动程序和双DMA传输实现的有效性。然后,模拟每行3 200像素、行频1 200行/s和每行4 800像素、行频1 600行/s,对这2种机载遥感图像线扫格式进行了图像压缩和传输测试。测试结果表明,2种情况都能实时完成压缩,而且图像品质比较恒定。表3是实际图像压缩的PSNR(BPP(bits per pixel)表示每个像元所占的平均位数)。

表3 两幅遥感图像压缩的PSNR值

图7是2幅遥感图像有损压缩后恢复图像,从中可以看出恢复图像的细节和轮廓都保持得非常清晰,主观视觉效果较好。

图7 有损压缩恢复图像

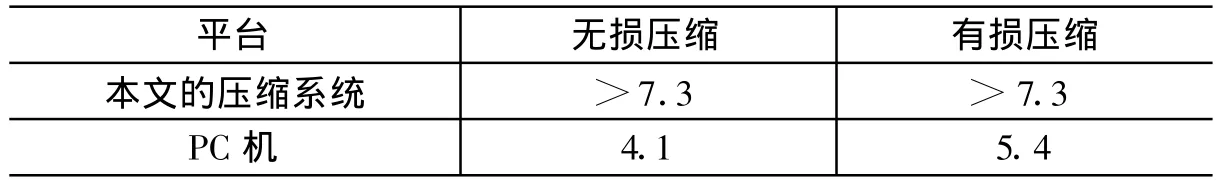

表4是本硬件平台压缩能力与CPU为Pentium4,主频为1.8GHz,内存为512Mbyte DDR 266的PC机压缩速度的比较。

表4 本文的压缩系统与PC机压缩速度比较 Mbit/s

5 结束语

该系统能提供16个并行差分输入通道和4个LVDS输出通道,既满足了目前的实际需求,也为以后处理数据量更大、分辨率更高的图像压缩提供了可能。作为压缩和逻辑控制中心的FPGA也具有丰富的存储资源,为开发更先进的算法(如EZW、SPIHT)提供了条件。目前,本平台实现了比较简单的位率控制方法和防止误码扩散的措施,研究者还可进一步研究,建立更为合理的率失真模型,通过模型又可以更好地调节图像编码输出,进而取得更好得图像压缩效果。研究容错恢复算法,保护重要的头信息和对图像影响最关键的参数,能在解码端恢复出原始数据,从而得到更好的图像品质。

[1]PLX Technology,Inc.PCI9054 DATA BOOK[M].2000.

[2]PCI SIG.PCI Local Bus Specification Revision 2.1[S].1995.

[3]Rubini A,Corbet J.Linux Device Drivers[M].2nd ed,USA:O'Reilly,2001.

[4]Weinberger M J,Seroussi G,Sapiro G.The LOCO-I Lossless Image Algorithm:Principles and Standardization Into JPEG-LS[J].IEEE Trans Image Processing,2000,9(8):1309-1324.

[5]ITU.ISO/IEC 14495-1.Information Technology-Lossless and Near-Lossless Compression of Continuous-Tone Still Images[S].1999.

[6]Weinberger M J,Seroussi G,Sapiro G.LOCO-I:A Low Complexity,Context-based,Lossless Image Compression Algorithm[C].1996 Data Compression Conference,1996:140-149.