基于FPGA的多路视频合成系统的设计

陈文辉,覃永新,黄庆南

(广西工学院 电子信息与控制工程系,柳州 545006)

0 引言

多路视频处理技术是视频监控领域的重要组成部分,其中多路视频合成系统在安防、指挥、航空等监控系统中获得广泛应用。多路视频合成系统就是将多路视频的每一个全画面按照一定比例缩小后合成为一路视频信号,然后在高分辨率的显示设备上以全屏或多窗口模式显示[1]。视频信号处理系统对信号处理速度的要求甚严,以往常使用的专用DSP芯片虽然满足了速度要求,但开发周期较长,产品的调试、修改及升级比较困难,成本较高。FPGA(Field Programmable Gate Array,现场可编程门阵列)器件具有并行处理速度高、集成度高、功耗低、设计灵活等特点,且有快速高效的开发平台,可加快开发周期等优势,使之成为设计高速视频信号处理器件的首选。

文中介绍了一种基于FPGA的多路视频合成系统,该系统接收16路由CCD摄像头采集的模拟视频信号,通过视频解码芯片转换为PAL制式的数字视频信号,FPGA对其进行抽取和帧合成等数据格式转换,再通过视频编码芯片的数模转换送入VGA显示器,可显示1、4、9、16路分割画面,并通过按键轮流切换视频画面。

1 多路视频合成系统的组成结构

系统以FPGA为核心,与视频解码模块、视频编码芯片和SRAM等外围器件一起构成整个多路视频合成处理系统[2]。FPGA芯片选用ALTERA公司的EP2C15AF484C8;视频解码芯片选用SAA7113H作为视频模数转换器件;视频编码芯片选用SAA7121作为数模转换器件;片外存储器SRAM采用IS61LV51216。系统的组成框图如图1所示,其中FPGA内部的设计主要包括按键控制单元、数据采集及提取单元、帧合成处理单元和帧存控制单元。

图1 多路视频合成系统组成框图

图1中的视频输入0~15是来自16路CCD摄像头的模拟视频输入信号,每路经由SAA7113H转换成PAL制式ITU656 YUV 4:2:2格式的8位VPO数据。上电后,FPGA首先通过IIC总线对视频解码器SAA7113H进行配置,接收16路VPO信号进行混合处理,根据最终显示窗口与原始图像大小的比例将其进行有效数据的抽取,并按照帧合成原理写入片外存储器中,组成一帧图像的数据,数据存储地址与屏幕中的像素地址一一对应,写满一帧后读出,格式再生后送入视频编码器SAA7121还原成模拟信号送显示器输出。

2 基于FPGA的多路视频合成系统的设计

图2给出了多路视频合成系统的内部结构图。

图2 视频合成系统的内部结构图

2.1 按键控制单元KEYS_CTL

按键控制单元用以控制画面分割数目的选择和视频通道的轮切。其中按键N1~N4分别选择画面分割数为1、4、9、16,按键NEXT是下一视频通道的切换键。START键按下后,默认全屏显示通道0的画面,输出Y[15..0]为0001H,之后每次按下NEXT键时Y[15..0]循环左移,切换到下一路视频数据;N2、N3、N4键按下时,处理过程与此类似。

2.2 数据采集及提取单元ACQ

数据采集及提取单元接收16路视频解码芯片SAA7113H输出的VPO信号并提取其中有效像素数据。SAA7113H除了输出数字视频信号VPO[7..0],还有相应的同步信号:行有效信号RTS0、奇偶场标识信号RTS1等。其中RTS0的上升沿表示有效行到来,RTS1的高电平表示奇场,低电平表示偶场[2]。

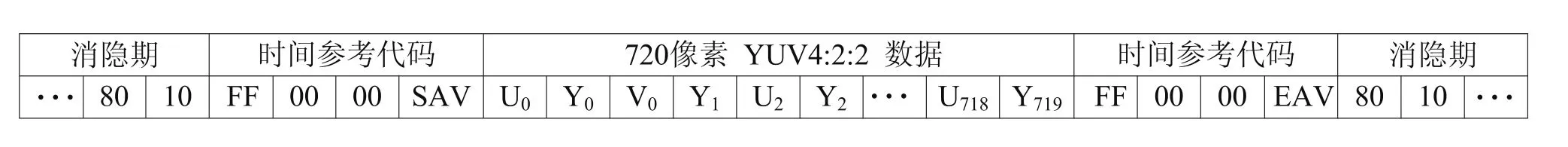

SAA7113H输出PAL制式的ITU656标准YUV(4:2:2)格式数据[2],其中Y表示亮度信号,而UV表示色差信号,像素时钟为27MHz。信号扫描方式为隔行扫描,帧率为25帧/秒,每帧图像分为奇偶两场,每帧像素为864×625,其中有效像素为720×576。SAA7113H输出的一行视频数据格式如图3所示,每行有1728字节,其中有效数据1440字节,对应720个有效像素,可以看成每一个像素由两个连续的字节表示。

数据采集及提取单元由16个数据采集通道构成,每一通道接收一片SAA7113H的行有效信号RTS0、像素时钟信号SYS_CLK和8位视频数据VPO[7..0],根据每一路的输出允许信号Y[15..0]和画面数目按键N1~N4,输出16路经过了抽取的有效数据VPO_OUT,共128位;以及表示16路视频通道的有效数据信号L[15..0]。

数据采集过程:根据视频数据流的时间参考代码SAV来获取有效数据的起始时刻。在一帧完整的视频数据中,第一场有效数据阶段的SAV为“8XH”,而消隐阶段的时间参考代码中的SAV为”AXH”。通过判断行有效信号RTS0为1时,分析出数据流中的“80 10 FF 00 00 SAV”定时参考代码后,启动计数模为1440的计数器,当计数值为40时置信号L为 1 ,标志一行有效数据的开始,同时为之后的数据处理提供同步信号;当计数值为1320时置L为0,从而结束一行有效数据的采集,在这个时间段内就可以截取行中1280个字节的有效像素数据[2]。

数据提取过程:当按键N1有效时不抽取数据,按照系统时钟将1280个字节的数据全部送入帧合成单元;当按键N2、N3、N4有效时,每个通道的数据进行1/2、1/3、1/4的抽取,即在每行的L信号为 1的状态下分别产生占空比为1/2、1/3和1/4的脉冲作为输出的选通信号,就有对应的视频数据流输出,然后在帧合成单元的控制下写入缓存。视频数据进行抽取的示意图如图4所示,经过抽取后每个视频通道的数据每行640B;类似地,9画面对应每行数据426B,16画面对应每行320B。

图3 ITU一行视频数据格式

图4 数据进行1/2、1/3、1/4、抽取示意图

2.3 帧合成单元

系统将视频画面分为i的2次幂个子块,每个子块按4:3的比例显示一个视频画面。帧合成就是将各个视频画面抽取后的数据按照帧格式重新合成一帧视频数据。由于每一通道的视频数据流以及行场同步信号各自独立,帧合成单元必须控制各个通道的压缩视频数据在数据缓存中的读写时间,以解决数据的同步问题;同时将各路数据顺序写入帧存储器中对应的分区中,从而合并为一帧完整的视频图像数据。根据视频合成的要求,4画面的每个图像大小为320×240像素,9画面为213×160像素,16画面为160×120像素。

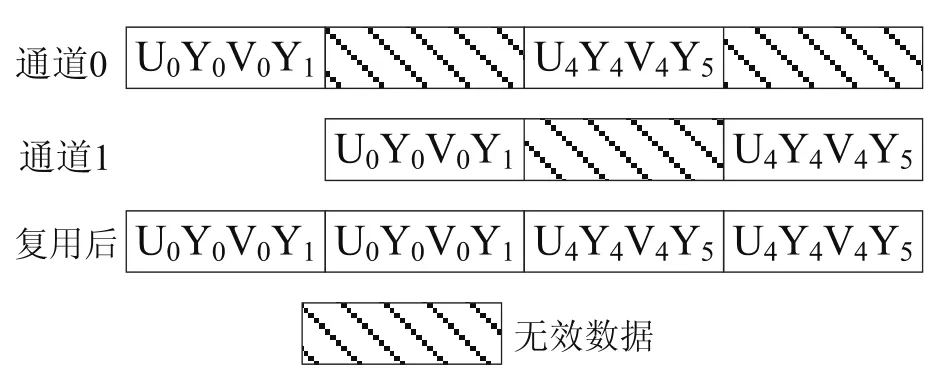

使用的帧合成技术时涉及到行内数据的时分复用过程,即利用每一行经过抽取后的数据之间的空隙来“加入”另一视频通道的数据,从而将2、3或4路信号合为一路视频数据流。图5中是四画面帧合成示意图,通道0和通道1的数据流经过有效抽取后,分别得到占空比为1/2的数据流,控制两个视频通道的数据的读取时间,使得通道1的数据滞后于通道0的数据4个时钟周期输出,则通道1的数据正好处于通道0的无效数据期,这两个通道的数据相互交错,就可以得到一行复合视频数据流U0Y0V0Y1U0Y0V0Y1U4Y4V4Y5U4Y4V4Y5…,此复合视频行包含2个视频通道的320个双字节,共为640个双字节。完成行内数据的时分复用后,选择合适的复合视频行存储在片外SRAM中就可以构成完整的一帧数据。为了均匀地抽取每个画面的视频行,须考虑奇偶场的因素,利用奇偶场标识端RTS1。在每个视频通道选择进行复合的视频行的行序号符合以下规则:

图5 四画面帧合成示意图

设画面分割数为i2,在每一场进行i分之一行的抽取:当i为奇数时,在RTS1=1时从行0开始抽取,RTS1=0时从行1开始抽取;当i为偶数时,每个视频画面只需要在RTS1=1时(奇场)抽取视频行,4画面时全取,为240行;16画面时1/2抽取,为120行。则在视频编码芯片输出一帧数据的期间,就可以得到合成画面的全部视频通道数据。根据以上原理设计帧合成单元,其内部结构图如图6所示,主要由缓冲存储单元STR_FIFO、读允许单元FIFO_RD、写地址产生单元WR_ADD和数据选择器SELECTOR组成。

图6 帧合成单元内部结构图

2.3.1 缓冲存储单元STR_FIFO

缓冲存储单元由16个双端口先进先出器件LPM_FIFO_DP并联构成,用于缓存每个视频通道经过有效抽取的视频数据。LPM_FIFO_DP的参数定制为:写数据位宽=8;读数据位宽=16;数据深度=2048;写时钟采用系统像素时钟SYS_CLK,读时钟采用像素时钟的二分频信号CLK2;写允许信号端连接数据采集单元输出的数据有效信号L[15..0],读允许信号端连接读FIFO单元输出的信号RD[15..0]。

2.3.2 读FIFO单元FIFO_RD

读FIFO单元负责在每一视频通道的一行的有效视频数据写入各自的缓冲FIFO后,通过判断数据有效信号L[15..0]和通道选通端Y[15..0],输出对16个FIFO的读允许信号RDOUT[15..0],从而实现一行数据的时分复用。工作过程是:通过判断数组Y[15..0]中的高电平位,将输出的端口分为i组,每组输出i个高电平选通脉冲组合,每个脉冲相隔2个时钟信号CLK2,持续时间为640个CLK2,然后下一组端口依次输出这样的脉冲组合,作为每个FIFO的读允许信号。如:当四画面分割时,若Y=000FH,L=000FH,则选中通道3~0,表示是这四个视频通道的画面进行帧合成,且其数据已经开始写入这一组的4个缓存FIFO,则可以在RDOUT的最低4位RDOUT[3..0]顺序输出脉冲信号去读取这4个FIFO。

2.3.3 WR_ADD单元

写地址单元的任务是依据缓冲FIFO输出的有效数据,产生对应的存储地址,从而保证数据能够正确写入与显示屏上的位置相对应的片外SRAM中的存储单元。按照分割画面的分区规则,将SRAM的存储空间也划分为i的2次幂个分区,其存储地址由高位的列地址和低位的行地址组成。行地址10位,表示一行中前640个单元用于暂存视频数据;列地址9位,表示可以暂存480行的数据;剩余的单元空闲。写地址单元WR_ADD根据画面分割信号EN[3..0],在16个通道的行有效信号L[15..0]有效后,输出对应于不同分割要求的写SRAM地址。根据显示器显示界面的空间位置来产生写地址。当画面分割数i为偶数时,设通道序号为j,则写地址的行地址=M+P*j(M=(0,1,……,640/i-1)),而列地址则是逐一增加。

2.3.4 数据选择器SELECTOR

数据选择器的作用是选择进行帧合成的i个视频通道的数据,同时也调整时钟,与写SRAM的地址同步送入帧存控制单元,从而保证帧合成的准确性。

2.4 帧存控制单元STORAGE_CTL

帧存控制单元是FPGA芯片与外设SRAM的接口,从片外SRAM中读取一帧数据,将每行数据都再生插入:有效视频行,插入SAV,EAV和行消隐数据。再生的数据和存储器中的有效数据分时地输出到视频编码芯片,然后输出到显示器。为了实现数据的连续处理,设计中采用了两片SRAM交替工作,一片SRAM写入一帧视频数据时,另一片SRAM读出已经完成帧合成的数据,写满或读空后,交换处理下一帧数据。

3 结论

图7 四画面分割的部分仿真波形

图7给出了四画面分割时的部分仿真波形,EN2=1,VPO0~VPO3表示4个视频通道的输入,DOUT1~DOUT4是表示经过帧合成以后的数据,WRADD表示对应这些数据的写入SRAM的地址信号,DD表示将经过帧合成后的数据流。可以看出,首先通道0和通道1的数据经过缓冲FIFO组,延时几个字节后,以四个CLK为间隔的时差输出,合成为数据DD:D9D8、DBDA、DBDA、DDDC、E1E0……,同时系统输出了写入SRAM的地址(十进制表示):0,1,320,321,2,3……。从仿真波形得出对数据流的帧合成处理是正确的。

任意画面的分割器,只是要改变视频信号的路数,硬件上增减摄像头、视频解码芯片,软件方面,就要根据画面分割要求对每一路视频信号进行适当抽取,然后合成为一帧数据,再经过视频编码芯片输出[3]。

视频信号的处理过程涉及到大量的数据交换,FPGA依赖其强大而灵活的逻辑控制功能和内部先进的快速通道互连,使其以超小的端端延时而在数据处理方面处于优势。系统在QUARTUSⅡ环境下进行综合验证,共使用了1200个LE。将程序下载到FPGA芯片进行仿真验证,实现了系统的功能。

[1] 胡瑶荣.基于FPGA的实时视频采集系统[J].电视技术.2005(2).81-83.

[2] 覃永新,陈文辉,章帆.实时视频数据采集的FPGA实现[J].电子技术应用.2009,31(9):46-48.

[3] 程治国.刘允才.多画面远程监控系统中关键技术的实现[J]. 微型电脑应用.2003,(19):14-16.