一种通用MPSK载波同步方法及其FPGA实现

李湘鲁

(中国工程物理研究院电子工程研究所,四川绵阳621900)

0 引言

载波恢复是数字通信调制解调器中一个关键组成部分,特别是在有大范围载波频率偏差的数据传输系统中,更需要有频率跟踪控制环路辅助载波相位跟踪环路。首先提出一种用于MPSK信号的适应大频偏的快速傅里叶变换(FFT)载波频偏估计器结构,无需辅助数据(NDA),能直接检测得到载波频偏绝对值大小。同时给出一种适合MPSK信号的通用锁相环结构。具体介绍FFT载波频偏估计器与通用锁相环在FPGA中的实现过程,并给出硬件实现结果和具体性能。

1 载波同步原理

MPSK(多相移键控)调制信号在无线通信系统中有着广泛的应用,因此研究其载波恢复方法具有普遍的意义。在工程应用中常首先用最大似然频率估计法将绝对频率缩小到一定范围后采用锁相环进行精确载波同步,本文也采用同样的思路。

在信噪比足够高时最大似然频率估计是无偏的,同时也有非线性估计器所共有的门限效应:即在信噪比低于某个门限时,均方估计误差上升很快。而在门限以上,均方估计误差可以达到Cramer-Rao限[1]。最大似然估计的均方误差除了在极靠近边带的地方之外,均与实际频率无关。FFT算法可以看成是最大似然估计的逼近。

假设位定时已知,用于计算的样点从匹配滤波器之后提取,每符号提取一个最佳采样点;匹配滤波器冲激响应满足奈奎斯特无码间串扰采样定理[2]。匹配滤波后的输入信号可以表示为:

式中,P为信号功率;dn为调制数据,Δf为频偏绝对值;Ts为符号周期;φ0为载波初始相位;zn为高斯噪声。

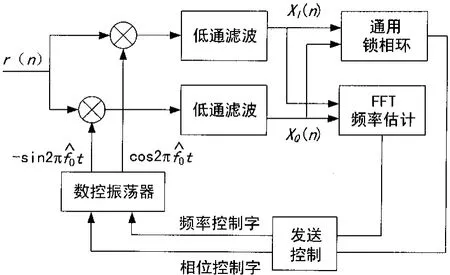

提出的MPSK信号载波同步整体结构如图1所示。

图1 MPSK载波同步结构

图1中,MPSK载波同步结构包括数字下变频、FFT频率估计模块、通用锁相环相位跟踪模块和NCO控制模块等。

FFT频率估计部分首先要将已调制信号叠加在未调载波上的调制相位去除,因此,第1步就要去调制。去调制后要将去调制后的相位映射到同相和正交分量上。将2个分量送入FFT处理器中,选择最大值的位置。最后根据采样频率和FFT计算点数将最大值映射到实际的频率值。

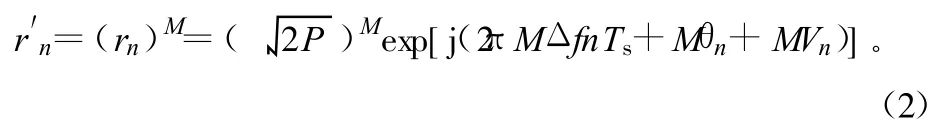

频偏导致未调载波的相位以每符号2πΔfTs速率变化,为了得到频偏估计值就必须去除数据调制的影响以得到未调载波。去调制可以分为DA和NDA两种方法,其中DA方法一般用于有前导码字的系统,NDA方法一般采用模2π/M和M次方法。本文中采用了M次方法,有

式中,θn为调制数据相位;Vn为等效相位噪声。因为 θn为 2π/M的整数倍,将r′n的相位模 2π是不影响相位值运算,可以得到:

将去调制之后的信号送入FFT模块中,再通过搜索FFT输出信号的最大值所在位置即可推算出绝对频偏的大小。

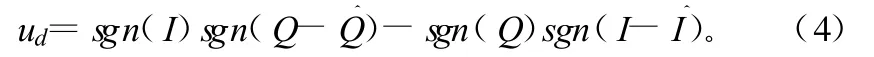

通过FFT频偏估计算法得到频偏估计值并输入数控振荡器(NCO)之后,就可以使用锁相环对载波相位进行精确跟踪以提高解调精度。为适应多种PSK调制体制需求,采用一种通用锁相环对MPSK信号进行相差检测。该通用锁相环鉴相特征函数如下[3]:

可见该锁相环鉴相过程仅需要与非门异或器、加法器和多电平限幅器非常适合FPGA实现。通过对调制样式的选择可以对多电平限幅器进行定义,就可用于对BPSK、QPSK、8PSK等多种调制信号的载波同步。

2 载波同步FPGA实现

通过介绍MPSK信号载波同步原理,下面主要介绍如何通过FPGA来实现载波同步两大主要模块,即FFT频率估计模块与通用锁相环模块。下面以QPSK信号为例进行分析。

2.1 FFT测频模块实现

2.1.1 去调制模块

去调制可以使用2种方法来实现:①通过反正弦求取每个符号的相位值,反正弦函数可通过查表法计算。本方法运算量很小,对硬件要求较低,但是由于反正弦函数在不同的取值范围内,变化速率变化很大,如果查找表的内容采用线性计算方式,那么查找表的尺寸将很大。如果要将查找表的尺寸压缩到可接受的程度,那么其精确度又是不能接受的,故具有一定局限性;②直接采用复数乘法器进行M次方运算将I/Q数据去调制,该方法运算量较大,对硬件要求较高,但精度较高。本文采用第2种方法,复数乘法器可以自己搭建或采用Xilinx公司提供的复数乘法器IP核。

2.1.2 FFT处理模块

FFT处理模块是频率估计模块的核心部件,本文中采用Xilinx公司提供的FFT v5.0 IP核来实现。考虑到硬件实际情况与测频精度要求,确定FFT点数为4 096点,输入输出位数均为16位。为减少对硬核乘法器(DSP 48s)的使用量,FFT IP核设置为Radix-2 Burst I/O模式。为了方便后续对FFT输出信号的最大值所在位置进行搜索,将“Output Ordering”选项设置为“Natural Order”。

2.1.3 搜索最大值与频率映射

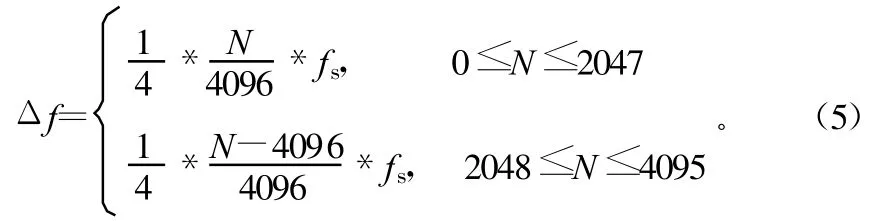

在FFT运算完成之后,就得到4 096组输出信号(实部与虚部)以及对应的INDEX值,将输出信号进行取模运算之后得到FFT运算的绝对值,再通过搜索4 096个绝对值中的最大值就可得到FFT谱线峰值所对应的INDEX值。记该最大INDEX值为N,FFT IP核的采样时钟为fs,可以得到实际频偏计算公式为:

式中,乘以1/4是因为针对QPSK信号做的去调制时引入4倍数关系。

2.2 通用锁相环模块实现

锁相环一般都由鉴相器、环路滤波器与数控振荡器3部分组成。本文中数控振荡器分别为FFT测频模块与锁相环模块共用。主要介绍前2部分实现要点。

其中鉴相器部分实现结构在上面已详细介绍,需要注意的是针对不同的调制体制选取不同电平幅度。环路滤波器的结构已有很多文章详细说明,这里就不赘述。主要工作是设计合理的环路滤波器带宽,本文中的FFT测频模块的频偏估计精度是与采样率挂钩的,以采样率为4倍符号率为例,则估计出的频偏为符号率的千分之一以内。以此为依据,设计捕获能力为符号率的1/1000到1/500的锁相环即可满足要求。

2.3 下变频模块与控制模块

要实现MPSK信号载波同步,下变频模块是不可或缺的。通常下变频模块由混频器、CIC滤波器、半带滤波器和数控振荡器(NCO)等组成。在工程中既可使用FPGA来实现,也可以使用专用DDC芯片,如ISL5416、GC5016等来实现。这里采用FPGA来实现,DDC模块中各个组件的设计实现方法也有较多文章论述,这里不再阐述。

由于FFT测频模块产生的频控字(FW)与通用锁相环模块产生的相控字(PW)均要控制下变频模块中的NCO,如何控制好二者发送顺序就很关键。本文中是通过FFT测频模块检测到输入信号频偏值大于一定门限时就发送频控字,小于门限时发送相控字。还以采样率为4倍符号率为例,检测当输入信号频偏大于1/1000的符号率时就发送频控字,直到检测到频偏小于1/1000的符号率时才发相控字。

3 性能验证与分析

整个MPSK信号载波同步电路主要分为FFT频率估计、通用锁相环、命令字发送控制与数字下变频4个模块:使用ISE开发软件,本电路在Xilinx公司的Virtex4系列芯片的XC4VLX200上实现,对码速率Rb=2 Mbps的QPSK信号在信噪比SNR=5 dB的条件下测量载波频率,FFT模块估计的载波频率值平均误差为0.21%,最大误差为0.35%,具体数据如表1所示。经过测试表明,在信噪比大于2 dB的情况下FFT模块可以正常工作,当信噪比低于2 dB后FFT测频性能很快恶化。

表1 FFT频率频率估计表

本载波同步电路使用Virtex4系列XC4VLX200芯片进行综合,使用了Slice 11020个占全部的6%,硬核乘法器Dsp48s使用24个,RAMB16s资源使用30个占全部8%。整个电路可以工作到128.9MHz。

4 结束语

针对MPSK信号提出一种适合多体制的通用载波同步方案,介绍其主要原理与关键模块设计方法,并利用FPGA开发软件通过硬件加以实现。通过测试,该载波同步电路具有适应较大频偏变化范围、较低信噪比、占用硬件资源较少等良好特性,并已应用于某通用数字解调设备中。

[1]RIFE D,BOOR STYN R.Single-tone Parameter Estimation from Discrete-time Observations[J].IEEE Trans on Information Theory,1974,20(5):591-598.

[2]叶淦华,张邦宁.基于FFT的校频技术及其FPGA实现[J].电子工程师,2007,33(2):31-34.

[3]FILIP M,PANG K H.Simulation of a Universal Base-band Carrier Recovery Loop[J].New Synchronisation Techniques for Radio Systems,IEE Colloquium on,1995(11):51-56.