基于IP核的滤波器复用模块的设计和实现

陈 镜,曹芳菊

(1.中国电子科技集团公司第五十四研究所,河北石家庄050081;2.邢台职业技术学院,河北邢台054035)

0 引言

随着IC技术与工艺技术水平的提高,集成电路规模越来越大,复杂程度越来越高,在一个芯片上已经可以集成一个独立的系统,完成特定的功能。在片上系统设计(SOC)变得异常复杂的今天,基于IP核的设计已成为EDA发展的必然趋势,嵌入式IP核的应用,由于重用设计思想、设计知识,极大地降低了设计成本,缩短了设计周期,成为当今片上系统的重要设计手段。数字处理系统的开发包括建立系统模型、设计仿真实现、验证等,基于FPGA的FIR数字滤波器系统开发也不例外。

1 硬件平台

1.1 FPGA处理芯片

采用的FPGA是ALTERA公司推出采用90 nm工艺的大容量STRATIXⅡEP2S130。该芯片具有以下特点:

①内部集成了多达63个基于乘加运算的数字信号处理(DSP)功能块,可配置成252个18×18乘法器,这些功能块针对高性能DSP应用进行了优化,可以在高达450 MHz频率上运行,结合ALM和内部存储块,能够高效地实现DSP算法;

②内部集成了具有TriMatrix存储结构的嵌入式RAM块,提供了多达6 MB的RAM,可以方便地配置成不同位宽和容量的RAM、双口RAM、FIFO等应用,性能可高达370 MHz;

③具有多达12个锁相环(PLL)和16个独立系统时钟,可以作为中央时钟管理器满足复杂系统时序需求,输出频率可高达1 GHz以支持高速串行接口应用;

④提供多达1 000个以上的用户IO,并支持多种IO标准(如LVTTL,1.8VHSTL,LVDS等),可以方便地配置成多种IO标准的高位宽并行接口和高速串行接口,极大丰富了系统的设计应用方法。

除此之外,开发工具QuartusⅡ提供了丰富的宏库LPM(参数化模块库)和IP Core,能够方便地完成设计输入、综合、仿真,不但提高了系统集成度,减小了体积和成本,同时加强了设计的灵活性。

1.2 FIR IP核宏单元

在数字系统中,滤波器常用于剔除噪声信号或其他无用的交调信号。和IIR滤波器相比,FIR滤波器具有严格线性的相位特性和稳定的滤波特性,因此常用于现代数字信号处理的预处理、频带选择及低通滤波中。FIR IP核可以利用Altera公司提供的QuartusII工具软件生成相应的VHDL文件及功能仿真模型,且有简单明了的操作界面。可以利用FIR IP核的滤波器软件进行滤波器的设计,通过选择设置滤波器的阶数、采样速率、带宽、窗函数类型等完成滤波器的设计,同时也可以进行变采样设置。滤波器设计完成后,实现该滤波器所需要的FPGA各种资源数目就被准确地估算出来了,设计者可以根据资源情况和具体应用对滤波器实现结构、输入通道数、数据存储方式、滤波器系数存储方式等进行合理的配置,以达到资源、性能的最佳分配。

2 FIR数字滤波器模型建立

FIR数字滤波器可以满足滤波器对幅度和相位特性的严格要求,避免模拟滤波器温漂和噪声等问题,具有精确的线性相位、容易用硬件实现和系统稳定等优点。因此,FIR数字滤波器在高保真的信号处理,如电力系统谐波分析、数字音频、图像处理、数据传输、生物医学等领域得到广泛应用。对于N阶FIR滤波器来说,差分方程表达形式为:

这里FIR数字滤波器模型的建立指的是确定FIR滤波器的抽头系数h(k)。

2.1 设计要求及复用参数分配

某项目中需要实现对128通道的数据进行数字滤波,每一路采样率为6.2 MHz,信号带宽为3~20 kHz,60 kHz~2 MHz内存在交调信号和杂散信号,要求在滤除杂散和交调信号的同时完成采样率的转换,并将滤波后的采样率变为50 kHz。

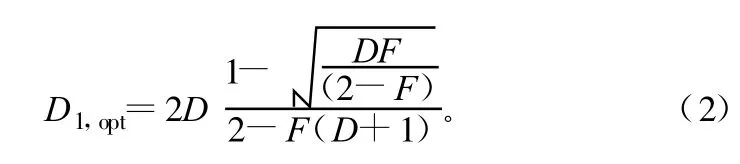

由于采样率需要从6.2 MHz变换到50 kHz,其抽取因子D=124,抽取因子较大,这时抽取器处理有一个重要的特性,即通过多级抽取,可以大大地节省计算量。在本设计中,采用2级滤波抽取,即D1和D2的乘积是所希望的抽取因子,也即D1×D2=D。给定总的抽取因子D以后,D1的合理取值为:

式中,D1,opt为D1的最佳值;F为最后的过渡区宽度除以截至频率,依据所确定的D1,opt可以求出第3个抽取因子为:

经过计算和仿真,本设计中将D1选为31,D2选为4。

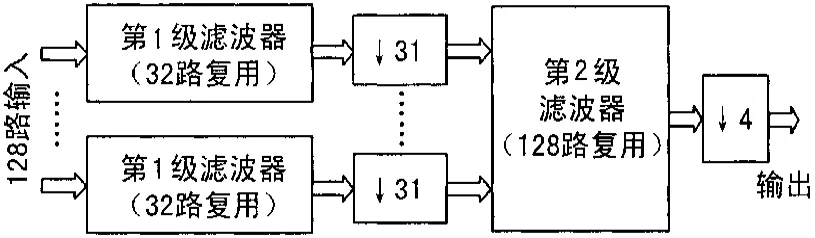

由于共需处理128路的数据,每路采样率为6.2 MHz,设计当中采用滤波器复用方法,每32路数据复用第1级滤波器,处理128路数据共需要第1级滤波器4个,滤波器工作速率为6.2 MHz×32=198.4MHz。第 1级滤波完成后,数据率降为6.2 MHz/31=200 kHz,在第2级滤波器中可以利用一个滤波器复用方式处理所有的128路数据,第2级滤波器的工作速率为200 kHz×128=25.6 MHz。整个的抽取滤波处理原理框图如图1所示。

图1 抽取滤波处理原理

2.2 滤波器参数设计和系数生成

根据项目要求,滤波器1采用hann窗函数形式,设计参数为:采样频率fs=6.2 MHz;截止频率fc=50 kHz。

利用FDATool得到的符合设计要求的滤波器是直接I型120阶对称系数的FIR数字滤波器。滤波器抽头系数保存为fir.coe文件。

滤波器系数如下:

h[0]=h[119]=-0.000001594368138,

h[1]=h[118]=-0.000005646850581,

h[2]=h[117]=-0.000010953703359,

……

h[60]=0.019354838709677。

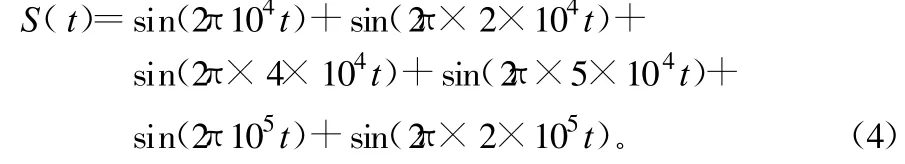

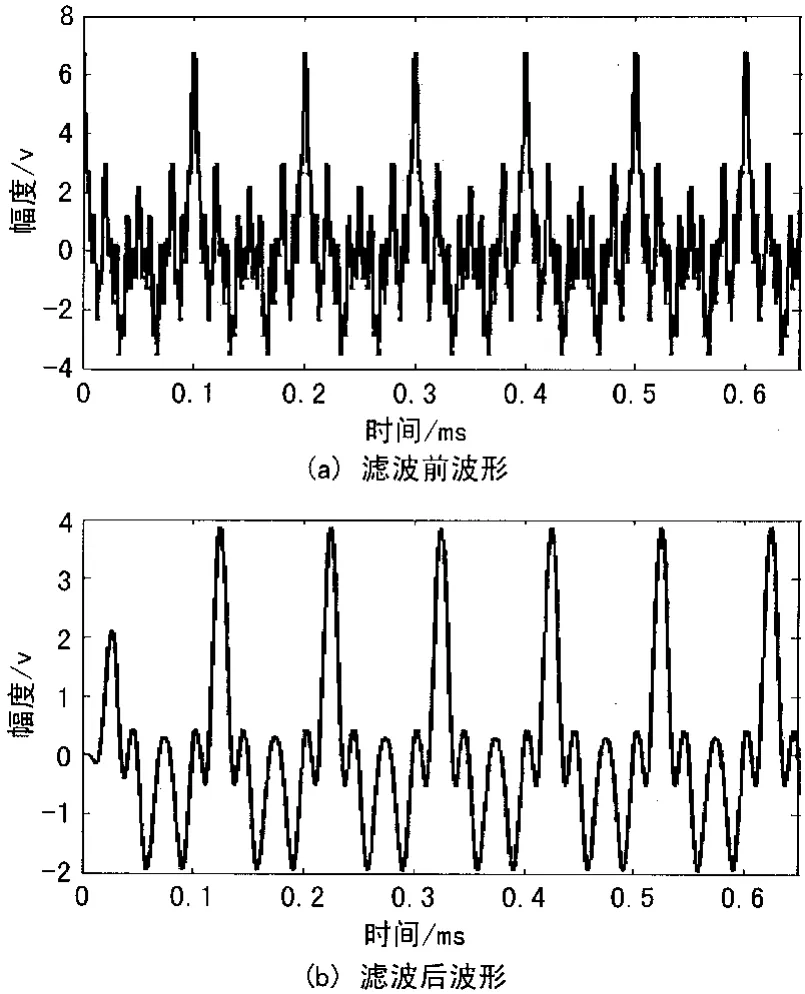

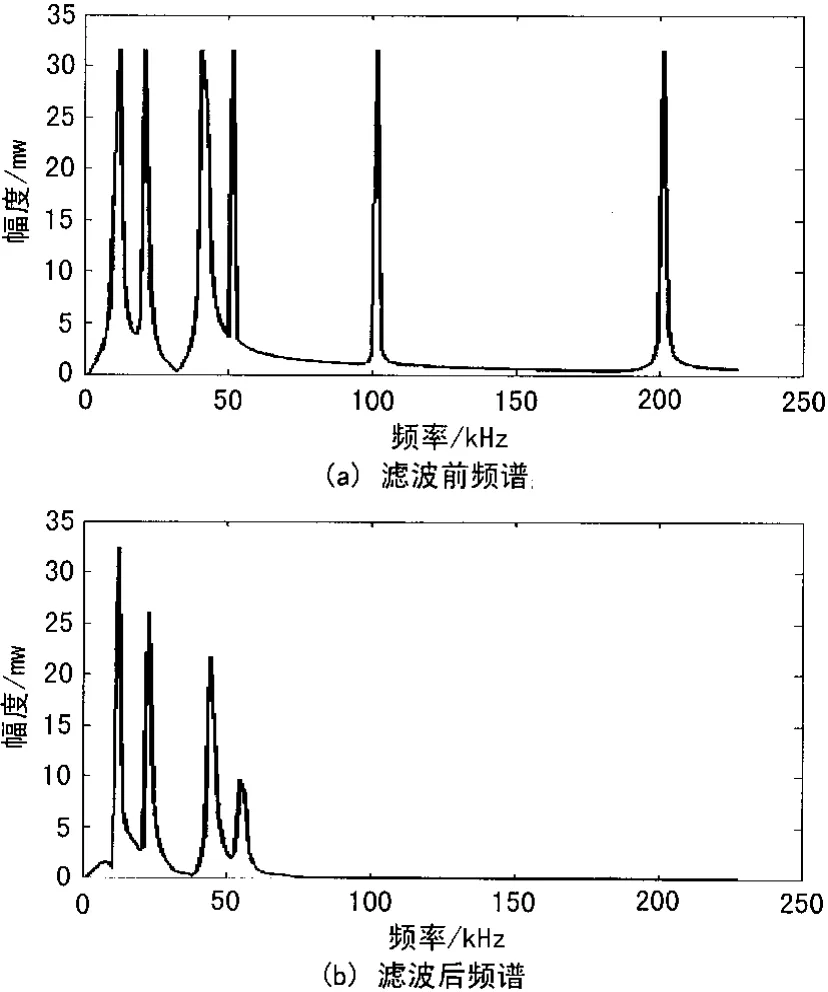

为了验证滤波器的滤波特性,对滤波器进行了仿真。在Simulink环境下将滤波器文件导入Digital Filter Design模块,输入含有混合频谱分量的激励信号s(t),分别察看s(t)和滤波后信号s′(t)的时域波形和频谱。s(t)的数学形式如式(4)。滤波前后的时域波形对比图如图2所示,滤波前后的频谱对比图如图3所示。由图3可以看出,s′(t)波形相比s(t),s′(t)波形含有较少的高频成份。由图3可以看出,高于20 kHz的频率分量开始得到抑制,60 kHz以上的频率分量被完全阻断,此滤波器满足设计要求。

图2 滤波前、后波形

图3 滤波前、后频谱

类似地,滤波器2采用80阶带通滤波器,滤波器2的设计和仿真可以通过同样的方法进行,在此不再赘述。

2.3 滤波器复用设计

利用Altera公司提供的FIR IP核的滤波器软件可以方便地进行多通道滤波器复用配置,通过选择设置滤波器的阶数、采样速率、带宽、窗函数类型、复用通道数等完成滤波器的设计,同时也可以进行变采样设置。设计者可以根据资源情况和具体应用对滤波器实现结构进行合理的配置,以达到资源、性能的最佳分配。

第1级滤波器的各主要参数设置如下:

滤波器类型:低通;

阶数:120阶;

采样频率:6.2 MHz;

截止频率:50 kHz;

窗函数类型:汉宁窗;

抽取因子:31;

输入通道数:32路。

第2级滤波器选用汉宁窗类型的带通滤波器,其各主要参数设置如下:

滤波器类型:带通;

阶数:80阶;

窗函数类型:汉宁窗;

采样频率:200 kHz;

截止频率1:1.6 kHz;

截止频率2:22 kHz;

抽取因子:4;

输入通道数:128路;

根据FIRCompiler软件的实时显示,第1级滤波器所占的资源为:逻辑单元655个,M4K存储单元32个。第 2级滤波器所占的资源为:逻辑单元2 507个,0M4K存储单元88个。

3 滤波器FPGA实现

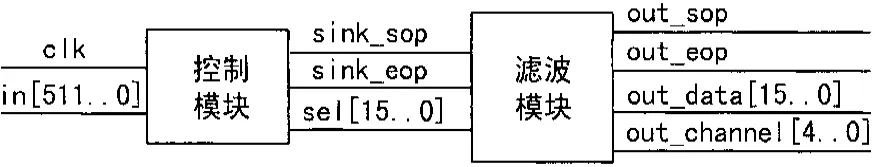

因为第1级滤波器和第2级滤波器的实现方式类似,在此仅以第1个滤波器为例说明具体的实现方式。第1级滤波器的实现原理图如图4所示,图中,滤波模块为采用FIRCompiler IP核例化生成的抽取滤波模块,控制模块为第1级滤波器的控制模块,控制模块接收32路的数据,即共512位的数据,形成滤波模块所需要的输入时序,其中sink-sop信号为数据起始帧标志,sink-eop信号为数据结束帧标志,sel[15..0]为当前输入到滤波模块的有效数据,对于第1级滤波器,因为复用通道数为32路,sinksop信号和sink-eop信号之间共有32个有效数据,每一路数据在sink-sop信号和sink-eop信号之间有一个数据输入到滤波模块。而第1级滤波器的输出时序与输入时序相仿,且有通道标志信号out-chn[4..0]信号输出。

图4 第1级滤波器实现原理

采用的FPGA是ALTERA公司推出采用90nm工艺的大容量STRATIXⅡEP2S130。在Quartus II软件中经过最终的编译后,整个设计占用逻辑资源数43%,占用存储器资源数为36%,经过测试和试验验证,该设计完成了预计的功能,性能稳定可靠。

4 结束语

应用FIR IP核来设计FIR滤波器,由于重用设计思想、设计知识,极大地降低了设计成本,缩短了设计周期,成为当今数字滤波器设计的主要设计手段。FIR IP核中具有多路复用和采样率转换等功能,可以完成多通道、变采样率的复杂设计,介绍的抽取滤波器复用设计就是基于该IP核提供的功能,并通过合理的资源分配和参数设计,完成了128路信号的滤波及抽取,实现了滤波器多路复用和抽取算法设计。提到的关于多路复用和抽取算法的实现方法对相关的滤波器设计实现具有参考借鉴价值。

[1]步衍冰,曾兴雯,梁敏超.基于FPGA的快速匹配滤波器[J].无线电工程,2003,6(33):31-32.

[2]LYONS R G.数字信号处理[M].朱光明,译.北京:机械工业出版社,2006.

[3]任爱锋.基于FPGA的嵌入式系统设计[M].西安:西安电子科技大学出版社,2004.