DVB-C2中高速并行BCH编码器的设计与实现

郑星宇

(珠海广播电视网络传输有限公司,广东 珠海 519002)

1 引言

DVB-C2是第二代DVB有线电视传输系统,采用最新的调制和编码技术,其性能非常接近理论的香农(Shannon)极限。在相同条件下DVB-C2比DVB-C提高了30%的频谱效率。关闭模拟电视后,对于优化的光纤同轴电缆混合网(HFC),其下行容量可增加60%以上,能为高清电视、交互电视及其他新的广播电视业务应用提供更大的信道容量。

DVB-C2与DVB-C的一个主要差别在于:DVB-C采用里德所罗门(RS)信道编码技术,而DVB-C2采用低密度奇偶校验码 (LDPC)+BCH码的前向纠错信道编码技术。BCH码[1]是循环码的子类,在短、中码长情况下的性能接近理论最佳值。BCH编译码电路比较简单,易于工程实现,在实际中应用广泛。DVB-C2标准[2]就采用了BCH外码和LDPC内码相结合的前向纠错技术,以提高传输的可靠性。

并行方式能极大提高编码速度,在同等数据吞吐量的条件下能有效降低对系统工作频率的要求。并行编码一直是信道差错控制领域的研究热点。借鉴循环冗余校验(CRC)的并行算法[3],可以实现BCH并行编码,以便优化DVB-C2调制器的基带处理。

2 串行编码算法

对于q进制BCH系统码,假设其码字、信息、校验向量分别是 c,m 和 d,它们的长度分别是 n,k 和 r(r=n-k)。信息向量m=[mk-1mk-2… m0]可视为k-1阶多项式m(x)的系数

BCH编码的一般过程如下:1)信息多项式m(x)乘以 xr得到 xrm(x);2)用 xrm(x)除以生成多项式 g(x),余式即为校验多项式d(x);3)拼接多项式即可得到码字多项式 c(x)=xrm(x)+d(x)。

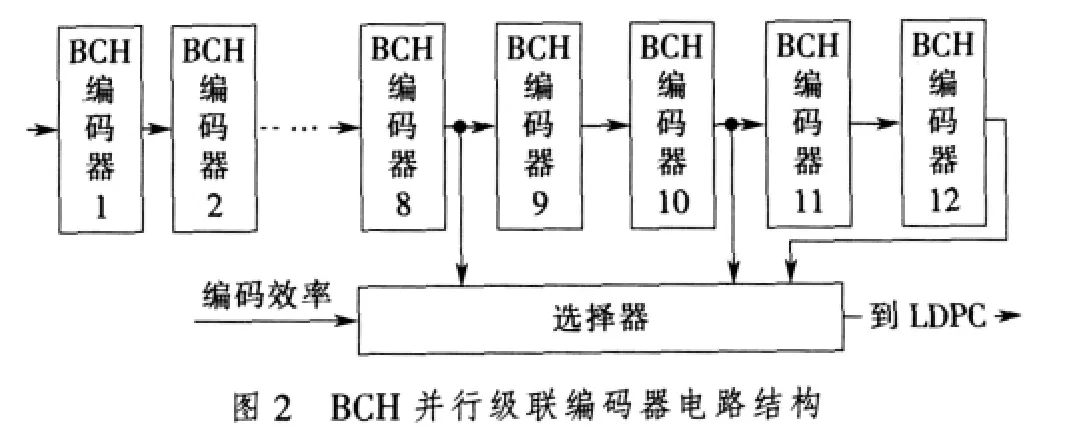

BCH串行编码器可采用线性反馈移位寄存器(LFSR)实现,如图1所示。LFSR初始化为0,起初两个开关都打向下方。每个时钟节拍输入1个信息码元,LFSR循环移位1次,输出的是信息码元。当信息码元输入完毕后,寄存器存储的就是校验向量,两个开关都打向上方。此后,每个时钟节拍输出1个校验码元。

3 并行编码算法

既然CRC和BCH码同为循环码的子类,那么完全可以采用并行CRC的原理[4]进行BCH并行编码。

对于图1所示结构,在编码过程中,每隔1个时钟节拍,移位寄存器存储的校验向量变化一次。令t时刻的校验向量为 d(t)=[dr-1dr-2… d0],下一时刻校验向量变为

在式(2)中,Ir-1是r-1阶单位矩阵,g是生成向量,g=[g0g1… gr-1]。

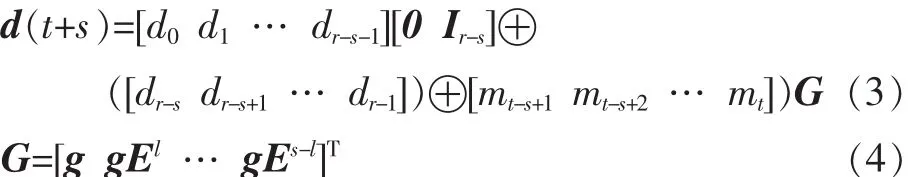

可以证明,t+s(s≤r)时刻的校验向量变为

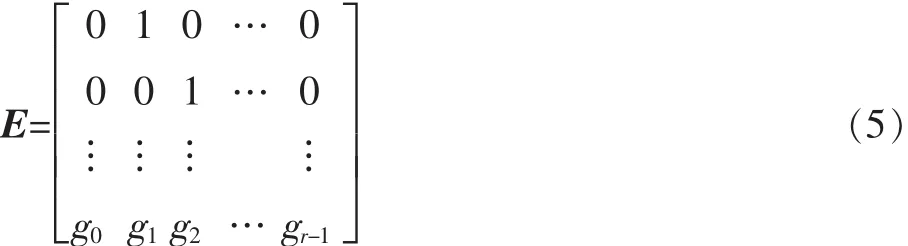

式中,Ei是如下矩阵E的i次幂

4 并行编码器的设计

DVB-C2标准的FEC技术采用了多级BCH外码,最多12级,每级均纠错1 bit。标准给出了12级BCH码的生成多项式,它们的阶次相同,但系数互不相同。BCH码的级数取决于LDPC内码的速率。以正常的FEC帧(帧长64800 bit)为例,不同码率的LDPC码要求BCH码具有不同的纠错能力v,v=8 bit,10 bit或12 bit,它们使用12级BCH编码的前v级。

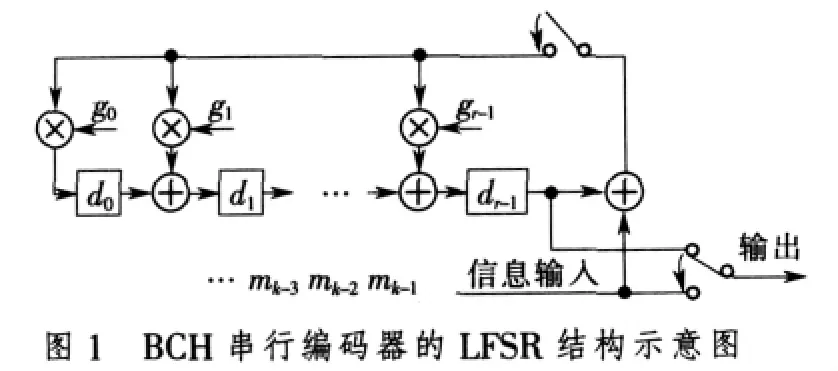

对于正常FEC帧的第1级BCH码,它的生成多项式是 g1(x)=1+x2+x3+x5+x16,r=16。 假设每次编码 8 bit,即s=8,s 同理,能够得到第2~12级BCH编码器的现态与次态的转移公式。 根据码率不同,BCH编码器级联数量不同,具体对应关系如表1所示。 得到各级BCH编码器的现态与次态的转移公式后,就可以用硬件实现BCH编码器。根据表1,设计电路结构如图2所示。 表1 BCH编码器级联数与码率对应关系表 选择器根据后级LDPC编码效率对输出进行选通,完成BCH编码后,数据送后续LDPC编码模块完成内码编码。 在设计中,采用Altera公司Cyclone III系列EP3C55型号的现场可编程门阵列(FPGA)作为实现BCH编码器的硬件平台,硬件描述语言采用Verilog,在Quartus 9.0软件环境下编译并进行数据仿真。数据仿真结果与理论计算结果一致,表明设计正确无误。 EP3C55 FPGA共有55856个逻辑单元,实验设计的8位12级并行BCH编码器使用了419个逻辑单元,未用到存储器,整体资源消耗<1%。 设计的8位并行BCH编码器的最高工作频率可达250 MHz,当工作频率是96 MHz时,数据吞吐率为768 Mbit/s,能够满足DVB-C2标准的指标要求。 [1]王新梅,肖国镇.纠错码——原理与方法[M].修订版.西安:西安电子科技大学出版社,2001. [2]ETSI ES 201980 V2.3.1,Digital video broadcasting (DVB); frame structure channel coding and modulation for a second generation digital transmission system for cable systems (DVB-C2)[S].2009. [3]黄维超,刘桥,黄初华.基于Verilog的CRC并行实现[J].微计算机信息,2009,25(30):112-113. [4]GIUSEPPE C,GIUSEPPE P,MARCO R.Parallel CRC realization[J].IEEE Trans.Computers,2003,52(10):1312-1319.

5 硬件实现