原子层沉积技术发展现状

(本刊编辑部)

随着半导体工艺技术持续推进,芯片尺寸及线宽的不断缩小、功能的提升成为半导体制造业者技术的关键,其中对于薄膜工艺的厚度均匀性及质量的要求日渐升高。传统的CVD沉积技术,已很难有效地精确控制薄膜特性及满足日益严苛的工艺技术要求。

原子层沉积技术 (Atomic Layer Deposition;ALD),最初称为原子层外延(Atomic Layer Epitaxy,ALE),也称为原子层化学气相沉积 (Atomic Layer Chem ical Vapor Deposition,ALCVD)。它是利用反应气体与基板之间的气-固相反应,来完成工艺的需求,由于可完成精度较高的工艺,因此被视为先进半导体工艺技术的发展关键环节之一。

原子层沉积最初是在20世纪70年代由芬兰科学家提出并用于多晶荧光材料ZnS:Mn以及非晶Al2O3绝缘膜的研制,这些材料是用于平板显示器。这主要是由于微电子和深亚微米芯片技术的发展要求器件和材料的尺寸不断降低,而器件中的高宽比不断增加,这样所使用材料的厚度降低至几个纳米数量级。因此原子层沉积技术的优势就体现出来,如单原子层逐次沉积,沉积层极均匀的厚度和优异的一致性等就体现出来。

1 原子层沉积原理

原子层沉积是一种可以将物质以单原子膜形式一层一层的镀在基底表面的方法。原子层沉积与普通的化学沉积有相似之处。但在原子层沉积过程中,新一层原子膜的化学反应是直接与之前一层相关联的,这种方式使每次反应只沉积一层原子。

原子层淀积(ALD)是超越CVD的技术,它是当需要精确控制沉积厚度、台阶覆盖和保形性时应选用的新技术。在ALD进行薄膜生长时,将适当的前驱反应气体以脉冲方式通入反应器中,随后再通入惰性气体进行清洗,对随后的每一沉积层都重复这样的程序。ALD沉积的关键要素是它在沉积过程中具有自限制特性,能在非常宽的工艺窗口中一个单层、一个单层地重复生长,所生长的薄膜没有针孔、均匀、且对薄膜图形的保形性极好。

原子层沉积是通过将气相前驱体脉冲交替地通入反应器并在沉积基体上化学吸附并反应,形成沉积膜的一种方法。当前躯体达到沉积基体表面,它们会在其表面化学吸附并发生表面反应。在前驱体脉冲之间需要用惰性气体对原子层沉积反应器进行清洗。由此可知沉积反应前驱体物质能否在被沉积材料表面化学吸附是实现原子层沉积的关键。气相物质在基体材料的表面吸附特征可以看出,任何气相物质在材料表面都可以进行物理吸附,但是要实现在材料表面的化学吸附必须具有一定的活化能,因此能否实现原子层沉积,选择合适的反应前驱体物质是很重要的。

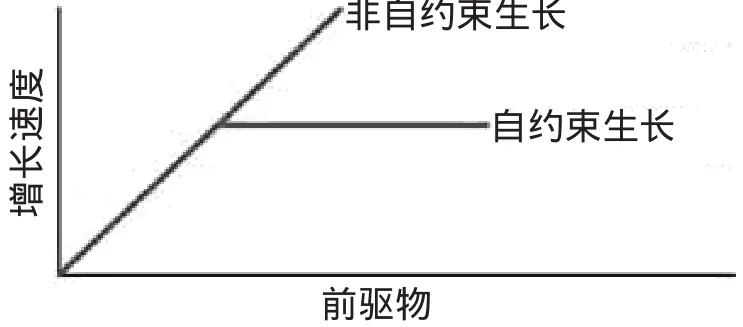

ALD技术对化学前驱物的要求与适用于CVD的那些材料不同。ALD工艺与衬底表面前驱物的化学性质关系极大。特别是为了获得好的粘附性和形貌必须有较高的反应性,不过在淀积单原子层过程中要阻止再进入反应位置的真正自约束生长。对于化合物(如金属氧化物或金属氮化物)的淀积,要求金属源和氧化/氮化化合物的选择与工艺条件(主要是输运/生长温度)和所涉及的二个或二个以上的化学物间的相互作用特别匹配。控制这些规范就能开发提供最佳性能的真正有自约束状态的ALD 工艺(见图1)。

图1 自约束和非自约束状态时的理论生长速度

原子层沉积是一种可以将物质以单原子膜形式一层一层地镀在基底表面的方法。原子层沉积与普通的化学沉积有相似之处。但在原子层沉积过程中,新一层原子膜的化学反应是直接与之前一层相关联的,这种方式使每次反应只沉积一层原子。由于沉积的每一周期有自约束性,因此对于超薄层生长的控制要好得多。ALD是在低于350℃的温度下进行的,而CVD要求的温度高于600℃,这就减少了能集成更复杂材料且又不产生交叉污染或内扩散的热沉积工艺。

原子层沉积工艺中,通过在一个加热反应器中的衬底上连续引入至少两种气相前驱体物种,化学吸附的过程达到表面饱和时自动终止,适当的过程温度阻碍了分子在表面的物理吸附。一个基本的原子层沉积循环包括4个步骤:脉冲A,清洗A,脉冲B和清洗B。沉积循环不断重复直至获得所需的薄膜厚度,是制作纳米结构从而形成纳米器件的最佳技术。

ALD的优点:

●可以通过控制反应周期数简单精确地控制薄膜的厚度,形成达到原子层厚度精度的薄膜;

●不需要控制反应物流量的均一性;

●前驱体是饱和化学吸附,保证生成大面积均匀性的薄膜;

●可生成极好的三维保形性化学计量薄膜,作为台阶覆盖和纳米孔材料的涂层;

●可以沉积多组份纳米薄层和混合氧化物;

●薄膜生长可在低温(室温到400℃)下进行;

●可广泛适用于各种形状的衬底。原子层沉积生长的金属氧化物薄膜用于栅极电介质、电致发光显示器绝缘体、电容器电介质和MEMS器件,而生长的金属氮化物薄膜适合于扩散势垒。

2 新一代逻辑组件所面临的课题

传统以来,逻辑组件的微缩是将关键的闸极氧化层以降低厚度的方式达成最佳化的目的,然而当工艺进入纳米节点后,由于传统的二氧化硅已无法再通过持续降低厚度达到良好的通道控制能力,其过高的漏电流将使得尺寸向下缩小变得无以为继,虽然目前有使用氮化二氧化硅(SiON)的方案,然而有限的介电系数并无法有效延展逻辑组件的世代演进,目前各大逻辑组件制造厂皆尝试着不同的几个方向来达成组件特性的改善,例如:加入局部或全面的应变结构,通过应变力改变通道中硅晶格常数来提升载子传输速度,以提升组件效能。然而单靠应变技术可能依然无法持续达成45 nm或32 nm以下所期盼的组件效能。导入高介电常数介电质及稳定的功函数金属闸极由于带电载子可通过穿隧效应穿透介电质而形成漏电流,导入高介电常数介电质取代传统SiO2或SiON成为可行的方案之一,以求降低漏电流并达成等效电容以控制通道开关。由于费米能级的钉扎(效应),不稳定的热性质,复晶硅闸极空阀,及硼扩散等问题,必须使用适当的双功函数金属来取代传统复晶硅,以作为匹配高介电常数介电质的控制电极。双功函数金属电极一则与NMOS搭配,一则与PMOS搭配,这使得相关的组件整合技术及工艺控制更为复杂,各材料的厚度及成分控制要求则更为严苛。3D立体鳍状结构晶体管:由于二维结构晶体管于32 nm节点以下的短信道效应,使得临界电压下降,并且无法有效控制通道开关。由三维立体的组件结构取代二维结构,通过增加的一维空间来改善驱动电流及取得较佳的临界电压控制,如此,闸极及金属电极包覆在微小的鳍状信道结构上,可让组件得到较佳控制,且可以有效被微缩。

2.1 高深宽比结构形貌

ALD在获得极佳的均匀平面薄膜的同时,它还具有另一显著的特征,该沉积工艺对3D和具有高深宽比(HAR)结构形貌有着良好的保形性。为了充分利用这一特征优势,ALD系统需要有一个良好的真空反应腔,能使用户具有所需的灵活性以使样品在反应气体中具有适度的暴露时间。这样脉冲式通入少量的前驱反应气体并在反应腔中停留较长的时间,可增加样品在生长化学气氛中的暴露时间,这是在具有复杂几何形状和高深宽比结构的样品上沉积具有良好保形性薄膜的关键。

2.2 高介电常数闸极介电层的运用

半导体器件制造正在趋向于采用k值愈来愈高的高k材料和能与它们相集成的阻挡层/接触层。根据ITRS,未来5~10年这些新型阻挡层/接触层会广泛采用。为Al2O3开发的技术已经向HfO2前进,并直指ZnO2等。但是这些新材料的寿命不会像过去的常规产品那么长。研究人员已经在研究超高k系材料,要求新化学材料和工艺能制造包含氧化钛、稀土氧化物和钡锶钛酸盐的电容器和晶体管。

在器件制造工艺中广泛将ALD用于高k、新电极材料、金属前介质和其它介质层 (如氧化硅等),这要求正确的化学材料组合。器件越来越小而提供的性能和功能则更强,化学材料仍在电子学革命中起着中坚作用,势头不减。随着各个公司期望分担R&D中的开发成本和推进创新解决方案,整个供应链合作程度将会持续提高。此外,对COO的关注将在电子工业中的作用越来越重要,未来只会强化。在新的方式中存在大量机会,愈来愈受关注的多学科合作及化学材料是持续推动创新的关键。

介电常数越高的介电层越能以较厚的厚度取得等效电容,可有效解决漏电流的问题。然而,并非越高介电常数的介电质越适合于逻辑组件的使用。通常,材料的热稳定性为考虑的重点之一,如何通过多重热预算(Thermal Budget)依然维持稳定的高介电常数,并保持理想的非结晶结构,以确保低漏电流的特性,目前研究最多的材料为HfO2、HfSiO、HfSiON、HfZrO、DyScO、Lao等。传统的整合工艺会在形成闸极后经过源极/汲极超浅界面活化回火(USJanneal,RTA,>1 000℃)。如此严苛的热预算环境,迫使大部分的高介电常数介电质皆有可能结晶而使漏电流大增,可能的解决方案为:耐高温的高介电材料开发:例如 HfSiO、HfSiON、DyScO、Lao。此法须搭配可忍受高温的双功函数电极工艺,其工艺整合流程较为简单,但材料的选取及沉积方法皆需面对较多的挑战,尤其是在材料的选择及薄膜成分的调整上,工程师必须面对的是上百种可能的材料以及各种材料间组合。开发变更程序的后闸极(Gate last,ReplacementGate)工艺:将传统前闸极(Gate First)工艺取代为后闸极,以避开高温热预算,材料的选择上虽然限制较宽,然而工艺整合相对复杂,由于介电材料可能沉积在间隙壁所定义出来的闸极区间内,其尺寸已进入纳米等级,且深宽比可为3~5。

3 原子气相沉积技术(Atomic Vapor De position,AVD)

一直以来,原子层沉积即被视为下一代组件工艺的明星技术,在一些高深宽比的沟槽或堆栈电容的量产上,由于其优异的阶梯覆盖及相对较低的热预算,的确提供世代演进的驱动力,然而其过低的沉积速率却成为量产时程上最大的障碍。此外,由于原子层厚度的控制来自于相对低温下的自我限制(self-limited)现象,使得可适用于此温度范围的先驱物相对较少,对于研发人员在材料的多方尝试上出现相当多的局限性。有鉴于此,如何在确保原子层沉积的分辨率(atomic layer resolution),并提供符合量产的沉积速率及适合研发的多样性选择,以降低生产及研发成本,即成为次世代薄膜沉积的重要课题。

相对于ALD,原子气相沉积技术需通过惰性气体(如N2或Ar)将金属先驱物及反应气体加以清除隔离(purge),以形成每一层原子层沉积。AVD是由精准的机械性微注射器(micro injector)来控制每一次金属先驱物的沉积厚度,其精度可达每次脉冲(pulse)2 nm,通过快速精准的脉冲(pulse)以达成原子等级的沉积厚度。此时,并不需要使用惰气加以隔离反应气体与金属先驱物,而是将反应气体以持续流放的方式,并于同时利用微注射器将金属先驱物注入反应腔体,透过适当的流场设计,即可沉积与ALD相同等级高质量的薄膜,其优点即是薄膜沉积速率大幅度的提升至倍数以上。

新一代的沉积技术─原子气相沉积提供了全新的设计概念,达成更精确的厚度及成份控制,更多的先驱物弹性及倍数的沉积速率,可提供客户最佳的研发及量产解决方案。由于原子层沉积技术可在晶圆表面一层一层的沉积原子或分子,对于45纳米以下的工艺需求是必须尝试的方案,以解决纳米等级精确的薄膜控制问题,然而一般原子层沉积技术受限于较少的先驱物(Precursor)弹性及过低的芯片产出,以致在研发及量产时程上迟迟无法提供有效的技术平台。

使用AVD沉积技术可通过控制脉冲频率加以调整对高深宽比之阶梯覆盖率,在深宽比超过1∶25的结构中AVD可以超越每分钟6 nm的速率达成接近100%阶梯覆盖率,其优异的填动能力及快速的沉积速率已提供Gate Last最具量产潜力的技术平台。

4 原子层沉积设备现状

原子层沉积设备能在较低温度下沉积薄而均匀的纯净薄膜,包括金属与介电质薄膜。原子层沉积(ALD)作为90 nm IC芯片和电子存储器件生产的关键技术正越来越在世界范围内被接受。以AIXTRON、Applied Materials、ASM International、Aviza Technology、Oxford Instruments等世界领先的半导体设备供货商,都先后推出了不同类型的原子层沉积设备,最新水平的设备亦也进入原子级。这些设备已被世界范围内的多种不同客户用于生产关键、先进的元件,比如HBT、PHEMT、MESFET、激光产品、LED、探测器和VCSEL,这些元件被用于光纤通信系统、无线和移动电话应用程序、光纤存储装置、照明、信号和照明设备以及其它广泛的先进技术上。

4.1 App lied M aterials公司iSprint Centura系统

应用材料 (Applied Materials)推出的iSprint Centura系统(图2所示),是结合300mm原子层沉积与化学气相沉积的系统,用于90 nm以下钨金属接触区量产应用上。应用材料表示,用于300mm的iSprint技术,在全球多家客户端进行65 nm产品的验证工作。

图2 iSprintCentura ALD/CVD系统

这套系统配挂4个反应室(见图3所示),每小时产出超过65片晶圆,据称较其它相似的竞争产品多出50%产出量,节省40%消耗与营运成本。这套系统的原子层沉积反应室能传送一层超薄(<5 nm)的成核层,较化学气相沉积技术降低15%以上的接触区电阻,可带动更快速与良率更高的产品。

图3 四模块工艺腔室

iSprint系统除提供原子层沉积技术外,特备有高压钨金属填充制程,以达到无空洞填充,利于接下来的化学机械研磨。这套系统补足应用材料Endura iLB(整合式线层 /阻障层)系统钛/氮化钛线层与阻障层金属沉积,提供客户目前及日后产品设计所需的接触区金属沉积解决方案。

4.2 Genus公司沉积设备

Genus公司位于美国Sunnyvale,是AIXTRON集团的公司成员之一;为全球的半导体工业和数据存储工业生产关键的沉积加工产品,为了能生产复杂的微型计算机芯片和电子存储装置,Genus为200 mm和300 mm半导体生产提供它的天猫座(LYNX)和StrataGem系列生产设备,它还为CVD(化学气相沉积)、ALD(原子层沉积)和预清洁性能提供薄膜沉积产品。Genus的CVD和ALD设备可分享同一个平台和系统设计,简化了生产和服务,并可快速完成安装。

Genus Strata Gem的300mm ALD加工设备已被台湾DRAM大厂——茂德科技公司(ProMOS Technologies)所采用,该系统将开始在位于中部科学园区(Central Taiwan Science Park)的ProMOS工程的Fab3上使用90 nm技术批量生产高级存储装置。300mm ALD系统将同时用于生产亚70 nm及其以上先进的DRAM?M IM?film(薄膜)。该公司的设备显示了Genus?ALD处理技术正在越来越被认同和接受,同时它也证明AIXTRON为市场提供先进技术的能力。AIXTRON目前正在集中扩大它在台湾市场的硅谷客户。

ALD市场已愈来愈重要,而AIXTRON极具创新的ALD、AVD和MOCVD的沉积技术正在寻求加快整合材料解决方案的实施,并将继续快速发展;Genus公司还多次从ProMOS科技公司获得先进的300mmCVD的订单,这种设备于2007年的第三季推出。

4.3 Oxford Instrum ents Plasma Technology公司的原子层淀积系统

Oxford Instruments Plasma Technology公司的FlexAL系统(图4所示)能够根据需求淀积超薄薄膜。设备采用等离子原子层淀积技术,能够在低温条件下得到高纯度、致密的薄膜,并且还能够使用热原子层淀积技术进行生产,这大大增强了设备的灵活性。设备已经具备生产高介电常数绝缘材料TiN、HfO2薄膜,室温淀积Al2O3薄膜和单层金属钌薄膜的能力,并能够兼容小样品到200mm硅片不同尺寸的操作对象。

图4 FlexAL原子层淀积系统

牛津仪器的FlexAL产品家族提供了一种新的、广泛的灵活性和能力,应用于纳米结构和器件工程,通过提供遥感等离子体原子层沉积(ALD)工艺和热ALD工艺,在单一系统内实现了:

(1)材料和源最大的选择灵活性;

(2)低温工艺,所以可以使用等离子体ALD;

(3)利用遥感等离子实现低损伤;

(4)通过程序控制的软件界面实现可控的,可重复的工艺。

该FlexALRPT原子层沉积设备能够:

(1)在单一系统中提供遥感等离子体和热ALD,可选择多种源和工艺;

(2)提供遥感等离子体和热ALD最广泛的源选择范围,具有最大数量的源传输模块,沉积温度高达700℃。

FlexALRPT系统特点:

(1)系统含有两个腔体:真空腔和沉积反应腔。有效地防止温度和真空度的泄漏,保持稳定的沉积反应条件,成膜均一细致无漏点。沉积腔与真空腔分开,沉积腔嵌入真空腔,形成一种保护套设备,可有效地防止沉积反应过程中沉积腔内的温度和化学气体泄漏,从而保证沉积腔内的体系稳定,不会有二次的化学反应。保证成膜效果和不损伤设备。真空腔一般会用密封胶圈密封,沉积腔处于高温、真空腔处于室温,所以密封胶圈在室温下寿命长、密封效果好,真空腔的真空度不会泄漏,从而保证成膜质量。如果沉积腔与真空腔共用一个腔体,密封胶圈在高温下使用,寿命短,时间一长密封效果不好,真空度会泄漏,从而使得成膜质量下降;

(2)前躯体化学品在反应腔中流动方向类似花伞喷射,垂直沉积于基体上,快速稳定,有别于横流式沉积系统。独特的顶端流动沉积模式比传统的横向流动沉积模式在成膜效果、沉积时间、自动控制等方面都有很显著的提高;

(3)可以通过控制反应周期数简单精确地控制薄膜的厚度,形成达到原子层厚度精度的薄膜。可生成极好的三维保形性化学计量薄膜,作为台阶覆盖和纳米孔材料的涂层。前驱体是饱和化学吸附,保证生成大面积均匀性的薄膜,不需要控制反应物流量的均一性。可以沉积多组分纳米薄层和混合氧化物;

(4)可广泛适用于各种形状的衬底。原子层沉积生长的金属氧化物薄膜用于栅极电介质、电致发光显示器绝缘体、电容器电介质和MEMS器件,而生长的金属氮化物薄膜适合于扩散势垒;

(5)前驱体源装置稳定可靠,可以用20年,并不是简单的源瓶带个加热夹套。沉积腔表面经过耐腐蚀处理,能够适应氯化物和氟化物等前驱体化学品的强腐蚀。样品载物台升降为气动式控制,具有自锁功能。样品沉积过程中能很稳定地保持体系环境 (例如湿度对于一些氮化物沉积就比较敏感),有效地减少环境波动对沉积效果的影响。系统配置高级独立的软件,具有自锁和保护功能。

4.4 ASM的Pulsar原子层沉积技术

ASM International N.V子公司ASM America日前宣布推出一个新的原子层沉积(ALD)工艺,通过氧化镧 (LaOx)及氧化铝 (AlOx)高k盖帽层(High K Cap layers),使32 nm节点高k金属栅堆栈可使用单一的金属,而不同于之前CMOS所需要的两种金属。高k电介质结合金属栅能实现更快和更小的芯片,适合高性能服务器和低功耗要求的先进产品,如笔记本计算机、PDA和智能手机等。

ASM这项尚在批准的氧化镧及氧化铝盖帽工艺专利,能够应对32 nm及其以下节点几何结构的挑战。如果没有这些盖层,需要采用两种不同的金属,在晶体管开关的P结和N结产生适当的电学特性。通过在基于铪(Hafnium)的栅介质和金属栅间引入超薄的盖帽层膜(cap film),原子层的电荷将会影响介质和金属间的相互作用。在小于1 nm的范围内 (相当于几个原子层厚度),通过改变cap film的厚度,可获得合适的金属薄膜性能。要达到这样的超薄膜所需的工艺控制能力,要求最先进的ALD技术,这也是ASM Pulsar®工艺模块所能提供的。多个Pulsar模块可以整合成单一的Polygon®平台,以在密闭环境中连续沉积铪基薄膜和盖帽层,并控制膜间界面层。

“对我们大部分的客户来说,解决高k与金属栅集成的挑战是最优先的考虑”ASM晶体管产品部产品经理Glenwilk说。“新工艺极大地简化了高k与金属栅集成工艺,并使我们能够支持先栅极(Gate First)以及后栅极(Gate last)工艺流程。ASM目前可以提供针对高k电介质、盖帽层及金属栅的ALD工艺。新工艺目前正在几个关键客户处进行试制,同时可在ASM应用实验室里进行演示,并且在世界范围内已有超过50台的Pulsar模块用于ALD高k工艺量产。”

ASM的Pulsar是第一款用于高k栅极量产的工具,其由45 nm节点开始采用,现在已经延伸至28 nm节点。Glen wilk表示:“我们的高k工艺证明了在28 nm节点上的生产能力,我们也期望进一步的开发成果能够将这些利益延伸到未来的节点上。”

4.5 Aviza公司的Celsior fx ALD系统

Aviza Technology,Inc.是全球半导体、化合物半导体、纳米技术及其他相关行业的设备和工艺供应商,该公司同时提供前端和后端工艺设备,包括ALD、LPCVD、APCVD、CVD、蚀刻和 PVD。Celsior和Verano 5500均为该公司商标。

该设备将用于45 nm及更小结点逻辑上的研究和高k栅极介质和金属电极薄膜的开发。Aviza的ALD设备大部分应用于存储单元,包括DRAM和flash。据报道该公司为中国晶圆代工厂SM IN装配了ALD工具。

最近Aviza宣布了其公司加入一个联合发展计划,参与该计划的还有台湾地区的Mosel Vitelic Corp公司。Aviza和Mosel将为下一代的flash应用联合开发ALD材料。

4.6 原子气相沉积系统

德国爱司强AIXTRON AG公司产品Tricent AVD?原子气相沉积系统(见图5),设计用于半导体原子层等级的薄膜沉积,特殊的Triject?通过精确至微秒等级的micro injection装置,可将每一次pulse精确控制其沉积厚度以达成优越的线性关系及超高速的产出,是ALD的3~10倍以上。针对多重组成的薄膜需求,AVD可通过多组独立控制的micro injection,对于原子等级的薄膜组成及模厚控制加以弹性操控,无论是单一组份(HfO2、ZrO2、TaN、Ru、Ir、TaCN) 双重组份(HfSiOx、HfZrOx、Ru-SiOx…),三重组份(PZT、SBT),甚至四重组份的薄膜需求,AVD皆具备优越的工艺弹性。

图5 Tricent AVD原子气相沉积系统

5 原子层沉积工艺对真空系统的挑战

在半导体业界日趋受欢迎的原子层沉积工艺(ALD)已造成对真空系统及废气处理子系统全新的挑战。有些300mm原子层沉积工艺真空泵寿命甚至不到一百片晶圆。为了要达到合理的原子层沉积工艺成本,真空系统寿命必须要能改善到超过100倍才能符合成本要求。

目前原子层沉积工艺最大的挑战是反应物在真空泵内的沉积。这种沉积不同于传统的气相沉积对干式泵浦的影响,是均匀而且分布于整个泵浦的抽气室(图6所示)。均匀的薄膜在泵浦微米级的间隙形成而使泵浦卡死或在再开启时失效。而如果未形成薄膜,反应物所生成的坚硬粉末将会刮伤泵浦内部零件进而损坏泵浦。

图6 泵浦抽气室

目前专为化学气相沉积工艺设计的真空系统通常不能满足原子层沉积工艺的需求,因为他们通常容易增加干式泵浦内的副产物沉积量。要以合理的成本来达到延长目前泵浦系统寿命一百倍需要有创意的工程技术及深厚的应用知识。

在原子层沉积工艺中,绝大部分的反应物都并未在反应室反应而通到真空泵浦中。而这些反应物,就像在反应室内一样,也会在泵浦内部反应而将泵浦内腔表面饱和化。改变温度及氮气冲洗已被证明无法有效在下一种反应物进入前将原有沉积物自泵浦内腔表面移除。较高的泵浦温度一般并不能解决问题因为它并不会停止原子层沉积反应也不会挥发沉积膜。某些状况高温的泵浦甚至增加了泵浦内腔沉积的速度。

真空系统在研发阶段遭遇的困难和量产时所可能遭遇到的失败机制有时并不相同。即使主机台已被证实足以应付高产量的使用,在转移工艺至生产线时仍有可能发生延迟上线的状况。同时,工艺反应室内的压力,不论使用何种真空系统解决方案,必须要维持稳定。

所有不同形式的干式泵浦如螺旋式或是鲁式加爪式结构都可以适用于上述状况。不过泵浦设计细节如间隙、材质、表面处理、电动机功率及监控等都有可能产生影响。而实际经验显示即使调整反应室出口到泵浦之前的状况也可能影响到是否能顺利量产。

因为原子层沉积工艺的问题并不在于粉末的处理或是避免凝缩,有两种处理方案可以依原子层沉积的化学或是主机台特性单独或混合使用:

(1)避免所有反应物都进入泵浦。

(2)所有反应在泵浦前完成而以一些机制如阱在泵浦前就先行处理这些副产物。

[1]H.Kim“Atomiclayerdepositionofmetalandnitridethin?lms:Current research efforts and applications for semiconduc tor device processing”[J]J.Vac.Sci.Technol.B216,2003(Nov/Dec):2231-2259.

[2]Ganesh M.Sundaram,Eric W.Deguns,Ritw ik Bhatia,Mark J.Dalberth,Mark J.Sowa,Jill S.Becker;“ALD用于非平面性3D形貌结构的薄膜沉积”[J]半导体科技2009(8/9):29-34.

[3]Chen Yuh Herng,Kevin Lin,“原子层沉积制程真空系统”[J]半导体科技 2007(4/5):23-26.

[4]SANTA CLARA,“Applied Materials’High-k/MetalGate Technology Selected by ST microelectronics for 28nm Chip Production” [EB/OL]www.appliedmaterials.com/products/Highk–MetalGate-4.htm l.

[5]“Unique Integeated ALD and CVD Tungsten System for≤65nm/70nm”[EB/OL]www.applied materials.com/products/.../32_iSprint_noKPI.