数字Costas环在FPGA中的实现

封小钰 鄢文飞 刘必刚

(武汉理工大学信息工程学院 武汉 430063)

在利用相干解调的数字通信系统中,载波同步是正确解调的前提,也是实际通信中的一项关键技术[1-2].常用的载波同步方法有平方环和Costas环等,由于Costas环有跟踪低信噪比的抑制载波信号的特性而在实际系统中得到广泛的应用.目前国内外对Costas环尤其是改进后的Costas环进行了一系列的研究,尚耀波等建立了Costas环的Z域模型,通过软件编程实现,称之为软件Costas环[3];李波等根据Costas环的结构,在FPGA芯片中完成了硬件实现[4].然而,这些研究大部分都是基于传统的Costas环结构,同时也没有考虑到程序在实际应用中的资源占用情况.本文在分析Costas环的构成原理后,根据实际硬件的片上资源调整了滤波器的结构,提出一种用CIC滤波器来取代传统的环路滤波器.最后,本文结合项目的应用,首先在Simulink平台上实现了该算法,然后移植到Verilog上,用实际的FPGA芯片对此算法进行了验证.

1 Costas环原理

1.1 传统Costas环的结构

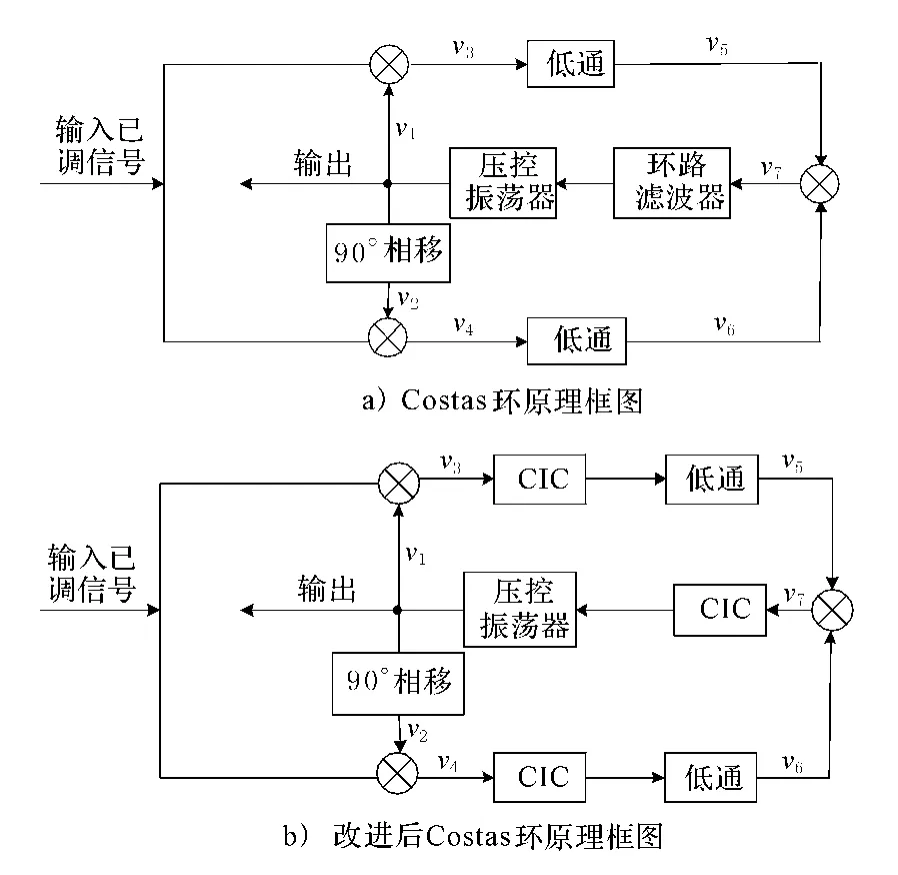

科斯塔斯环又称同相正交环Costas环,Costas环由Costas1956年提出,其环路工作频率为载波频率,远远低于平方环的工作频率,实现成本较低.其原理框图如图1a)所示.

图1 改进前后Costas环原理框图

在Costas环环路中,误差信号v7是通过两路低通滤波输出相乘得到.压控振荡器(VCO)输出信号直接供给一路相乘器,供给另一路的则是压控振荡器输出经90°移相后的信号.两路相乘后经过低通滤波和环路可以得到仅与载波相位偏差信号有关的信号v7.用此信号来控制VCO就可以调整VCO输出和载波信号保持一致的相位.

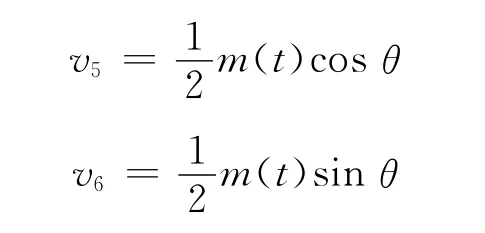

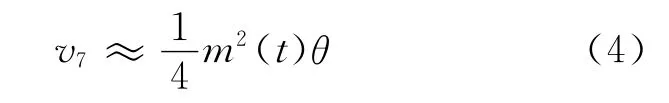

设输入调制信号为m(t)cosωct,则

经低通滤波器后的输出分别为

将v5和v6在相乘器中相乘,得

式(3)中θ是压控振荡器输出信号与输入信号载波之间的相位误差,当θ较小时

式(4)中的v7大小与相位误差θ成正比,它就相当于一个鉴相器的输出.用v7去调整压控振荡器输出信号的相位,最后使稳定相位误差减小到很小的数值.这样压控振荡器的输出就是所需提取的载波.

1.2 本设计Costas环的结构

考虑到FPGA资源的消耗的问题,本设计在实际过程中采用了CIC加低通滤波器的结构,并且用CIC滤波器代替了环路滤波器,改进后的结构图如图1b)所示,仿真结果表明,在提取载波效果相同的基础上,改进后的Coatas环大大节省了资源.

2 Costas环的Simulink实现

本Simulink仿真在Matlab 6.5环境下通过.仿真模型如图2所示.调制模块采用Bernoulli Binary Generator模块产生的32k的nrz码与Sine Wave模块产生的128k的载波相乘,然后与压控振荡器VCO恢复的本地载波进行相乘,VCO输出信号90°移相是通过希尔伯特变换[5]来完成的.

调制后的信号与VCO恢复的相互正交的两路本地载波进行相乘后,分为IQ两路,经过低通滤波器成为基带信号的解调输出,考虑到采样频率过高会造成FPGA芯片资源消耗严重,所以此处低通滤波器用CIC滤波器加低通滤波器的结构代替.Costas环设计的重点是环路滤波和VCO参数的调整.

2.1 环路滤波

本设计环路滤波部分用CIC滤波取代.CIC滤波器可以对数据流进行降速处理,本设计IQ两路采用抽取后滤波,降低4倍的采样速率(见图3中的Downsample模块).

图2中的CIC内部结构图如图3所示,后面的FPGA仿真也验证了此方法的优点和正确性.

图3 CIC滤波器结构图

2.2 VCO

本Costas环调频信号用Voltage-Controlled Oscillator产生,中心频率和输出信号幅度和载波信号保持一致,压控灵敏度λ根据实际情况计算调节.

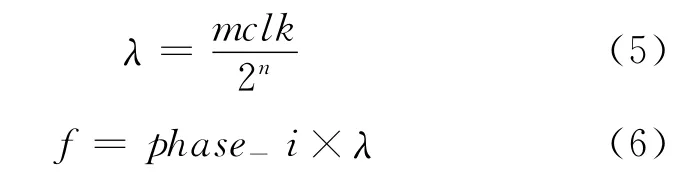

式中:f为信号的中心频率;phase-i为调整步进;mclk取4.096M;n取22位,则

压控灵敏度λ取0.976 5625.

2.3 仿真结果

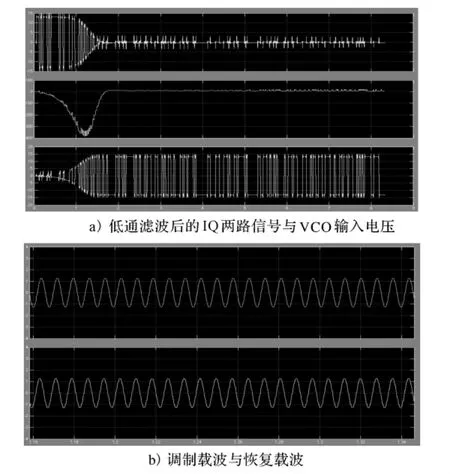

图4为运行simulink模型后的波形.图4a)是图2中示波器Scope的波形,为低通滤波后的IQ两路信号与VCO输入电压.图4b)是图2中示波器Scope1的波形,为调制载波与恢复载波.

由图4a)仿真波形可以看出,VCO输入电压在过一段时间后波形稳定,低通滤波后的IQ两路信号恒包络并且一路趋于为零,表示环路得到锁定.图4b)仿真波形可以看出,环路恢复出的载波与调制载波频率相同,表示环路已经成功的恢复出了载波信号.

图4 Costas环simulink仿真结果

3 Costas环的FPGA实现

本系统由Verilog语言进行设计,硬件选择Cyclone II系列的EP2C5Q208C8芯片,布局布线.综合工具选择Quartus II 8.1,波形仿真工具ModelSim SE 6.1f,系统由正交分量相乘模块、CIC滤波模块、低通滤波模块、误差相乘模块和DDS模块组成[6].

3.1 DDS模块

DDS模块调用Quartus自带的IP core NCO(数控振荡器).nco在波形仿真中要注意拷贝core中的dds_cos_c.hex,dds_cos_f.hex,dds_sin_c.hex,dds_sin_f.hex这4个文件到simulation\modelsim文件夹下,此4个文件用来产生正弦波,如果仿真过程中vco没波形,要注意检查此问题,并且在改变nco的设置时,同样要检查这4个文件是否同时更新.

3.2 环路锁定的判定

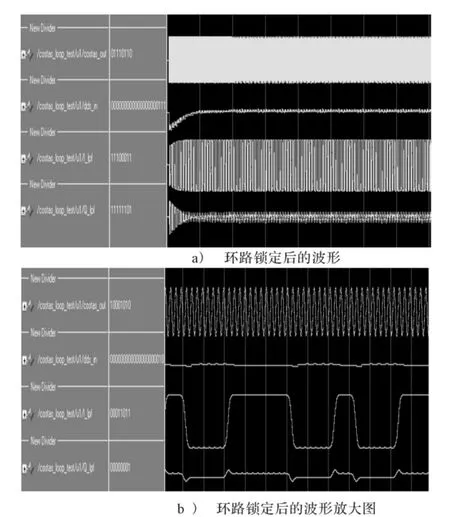

图5a)为环路锁定后的波形,图5b)为环路锁定后的波形放大图.图中costas_out为环路恢复出的正弦波,dds_in为压控振荡器的输入电压,I_lpf为I路信号经过低通滤波器后信号,Q_lpf为Q路信号经过低通滤波器后信号.

图5 Costas环modelsim仿真结果

由图5可以看出,此环路已经很好的锁定.

4 结 论

1)BPSK信号是由32k的NRZ码调制到128k载波产生,costas程序能够在频差+200Hz内(频偏为0.15%)恢复载波.

2)用CIC滤波器来取代传统的环路滤波器,很大程度上节省了系统的资源.

3)本环路设计已在软件无线电实验箱中得到应用,在一片FPGA(EP2C5Q208C8)上编程实现,摆脱了传统的硬件电路设计,其算法可移植性强,符合未来通信设计的发展方向.

[1]樊昌兴,张甫翊,徐炳祥.通信原理[M].北京:国防工业出版社,2001.

[2]曹志刚,钱亚生.现代通信原理[M].北京:清华大学出版社,1992.

[3]尚耀波,郭 英.一种软件科斯塔斯环的模型建立与实现[J].空间电子技术,2009,4:35-38.

[4]李 波,李玉柏,等.在FPGA中用costas环实现载波同步和数字下变频[J].信息通信,2006(2):22-25.

[5]邵玉斌.Matlab/Simulink通信系统建模与仿真实例分析[M].北京:清华大学出版社,2008.

[6]田 耘,徐文波,张延伟,等.无线通信FPGA设计[M].北京:电子工业出版社,2008.