一种新的多路数字信号光纤传输系统的设计与仿真

蹇清平,佘新平

(长江大学电子信息学院,湖北 荆州 434000)

一种新的多路数字信号光纤传输系统的设计与仿真

蹇清平,佘新平

(长江大学电子信息学院,湖北 荆州 434000)

提出了一种新的多路数字信号光纤传输系统,介绍了系统总体架构,同时阐述了硬件电路的设计思路和方法,完成了整个系统电路的VHDL设计、验证以及FPGA实现,并给出了系统的仿真结果。仿真结果表明,该系统符合光纤传输的技术要求。

光纤传输;VHDL;FPGA

随着通信领域中数字信号处理技术的发展,对数据传输速度以及传输距离提出了越来越高的要求。采用FPGA设计专用的多路数字信号光纤传输系统具有极大的灵活性,通过软件仿真,验证设计的正确性,可大大节省设计的时间,并提高了开发和研制的效率。而光纤具有很宽的带宽、低损耗、抗干扰和保密性好等优点[1]。结合以上2个优势,笔者通过采用光纤以及FPGA可实现多路数字信号的远距离传输。

1 系统总体设计

整个系统以FPGA主控芯片EP1C3T144C8为核心控制器来组织工作,其整体设计框图如图1所示。系统主要由4部分组成,分别为发送端的电端、光端和接收端的电端、光端,其中输入信号由外部信号源提供,3路数字信号分别通过时分复用、HDB3编码、HDB3译码、CMI编码,然后送至1301nm光发模块实现电光转换,光信号通过光纤传输到达接收端,经1301nm光收模块实现光电转换并经过译码、解时分复用的处理得到3路数字信号输出。

图1 系统结构框图

2 各模块的设计

2.1时分复用器的设计

时分复用器应完成2个功能:①循环接收1路帧同步信号和3路256kbps数字信号,每路每次送8位信息码(其中第1路送入固定的帧同步码01110010),形成32位的合路数据;②将合路数据以2048kbps的速率发送出去,形成合路信号。

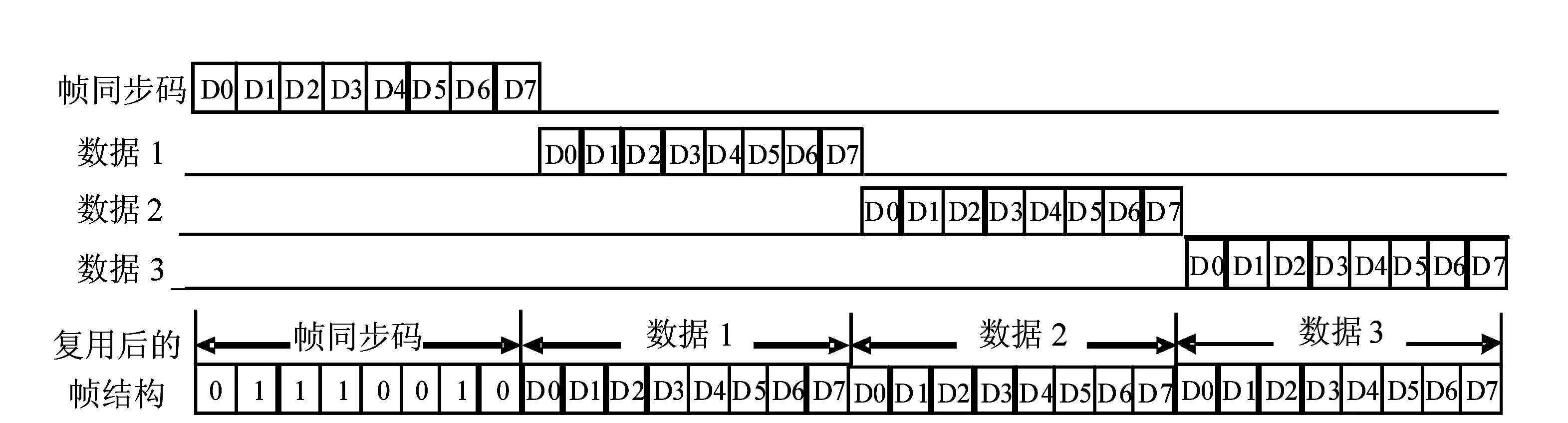

256kHz的同步时钟,每个时隙传送8位码,4路信号可通过定时开关预置,并以复接方式合成一路帧长为32位复用串行码。3路信号的速率固定,信息结构固定,每8位码代表一个“码字”。按顺序每次复接一路信号的8位码。复用过程如下:首先取固定的帧同步码,接着取第1路信号的第1个“码字”,再取第2路信号的第1个“码字”, 最后取第3路信号的第1个“码字”。依此类推,得到3路数字信号的复用,复用过程如图2所示。复用后的数据传输速率为2048kbps。

图2 数字信号复用示意图

2.2时分解复用器的设计

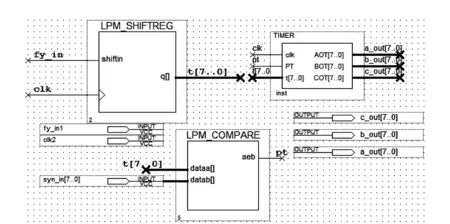

时分解复用器的功能与复用器相反,它通过移位寄存器与帧同步的提取来实现2048kbps的串行数据写入和256kbps的数据读出,实现合路信号的解复用。它由8位移位寄存器、帧同步信号比较器和定时输出模块组成,采用VHDL编程实现解复用的原理图如图3所示。2048kbps的合路信号经过8位移位寄存器LPM_SHIFTREG进行移位和串并转换,得到8位数据的并行输出,将输出的8位数字信号送入8位比较器LPM_COMPARE与帧同步信号比较,若与帧同步信号一致,则给定时输出模块TIMER一个捕获脉冲,并定时输出其他3路数字信号。

图3 解复用器VHDL设计原理图

2.3HDB3编码器的设计

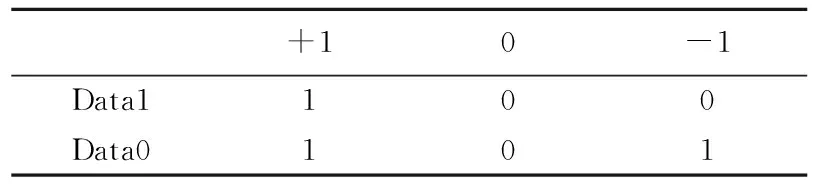

表1 HDB3编码输出表

由于VHDL不能处理负电平,只能面向“1”、“0”2种状态,所以要对它的输出进行编码,如表1所示。编码的实现是根据HDB3编码原理[2]把二进制码编码成两路单极性的码字输出,之后经过单双变换模块形成HDB3码。在编码过程中,要经过连0检测、破坏节判断、破坏节间“1”的个数判断、调整“1”的符号输出等步骤,编码部分可分为4个模块[3],编码流程如图4所示。

在进行HDB3编码器的设计时,需注意以下2个问题:①考虑将某些“0”改为“1”。用一个4位移位寄存器来对输入的序列进行检测,当检测到4个连“0”时,将其第4个“0”改为“1”。再设置一个T触发器来检测2个相邻的破坏节之间“1”的个数,若T触发器为“0”则说明2个相邻的破坏节之间“1”的个数为偶数,需要将第2个破坏节的第1个“0”置“1”,若T触发器为“1”,则说明2个相邻的破坏节之间“1”的个数为奇数,第2个破坏节的第1个“0”不变。②正、负号的考虑。除了破坏节的V即“1”的符号与它前面最近的“1”的符号相同外,其他的“1”的符号都是正、负交替的。所以再设置一个T触发器,当它检测到“1”时就使Data1翻转。当然,这样就不可避免地使破坏节的V的符号也出现翻转,为了防止它的翻转,用1个3位移位寄存器来跟踪V码,以保证V码的符号不变(与它前面最近的“1”的符号相同)[4]。

2.4HDB3译码器设计

图4 HDB3编码VHDL设计流程图

译码器设计是根据HDB3码的特点首先检测出极性破坏点,即找出4连零码中添加V码的位置(破坏点位置),其次去掉添加的V码,最后去掉4连零码中添加的B码以将其还原成单极性不归零码。

由HDB3码的编码规则[2]可知,“0000”都被“000+1”或“000-1”或“+100+1”或“-100-1”取代,所以,只要能检测出“+1000+1”、“-1000-1”、“+100+1”、“-100-1”,将它们分别改为“10000”、“10000”、“0000”、“0000”就可以了。当然“+1”、“-1”、“0”还是由Data1,Data0来表示,那么就需要有2个5位移位寄存器(C和D),Data0通过D,Data1通过C。通过D,C来检测,如果测到2个移位寄存器分别为“10001”、“0xxx0”或“10001”、“1xxx1”或“1001x”、“1xx1x”或“1001x”、“0xx0x”,数据输出是将D里面的数据流输出。所以只要将D中所测到的以上数据分别改为“10000”、“10000”、“0000x”、“0000x”,这样就可以得到HDB3码的译码输出了[4]。

2.5CMI编码器的设计

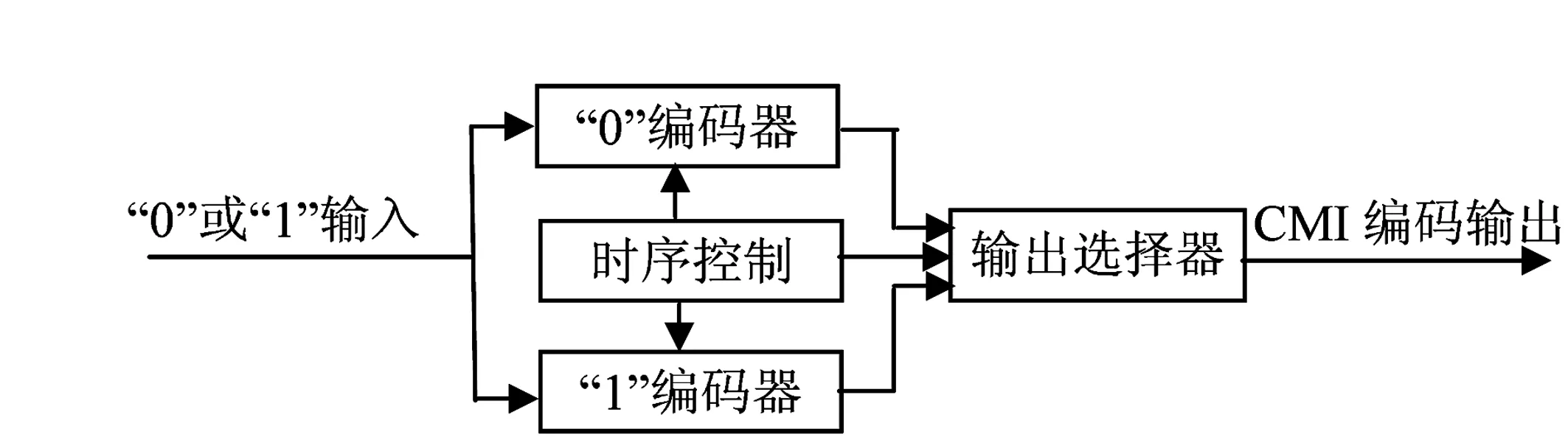

图5 CMI编码器设计框图

如图5所示,CMI编码器由“1”编码器、“0”编码器、输出选择器、时序控制4部分组成:①“1”编码器。因为在CMI编码规则[2]中,要求在输入码为“1”时,交替出现“00”、“11”码,因而在VHDL程序中必须设置一状态来确认上一次输入比特为“1”时的编码状态。这一机制是通过一个D触发器来实现的,每次当输入码流中出现“1”码时,D触发器进行一次状态翻转,从而完成对“1”码编码状态的记忆(“1”状态记忆)。同时,D触发器的Q输出端也将作为输入比特为“1”时的编码输出[5]。②“0”编码器。当输入码流为“0”时,则以时钟信号输出“01”码。③输出选择器。由输入码流来选择是“1”码编码器输出还是“0”码编码器输出。 以上3部分都是在时序控制下完成的。

2.6CMI译码器的设计

因为经过CMI编码后,1位码变成2位码,所以码的速率增加1倍。按照CMI码的译码规则[6],用系统的传输时钟(2048kHz)作为位同步时钟,在时钟的上升沿对CMI编码码流(1024kHz)进行采样,当采样结果为“1l”或“00”时,译码输出为“l”;当采样结果为“0l”时,译码输出为“0”。输出的译码码流的速率为CMI码流速率的1/2。

3 仿真结果分析

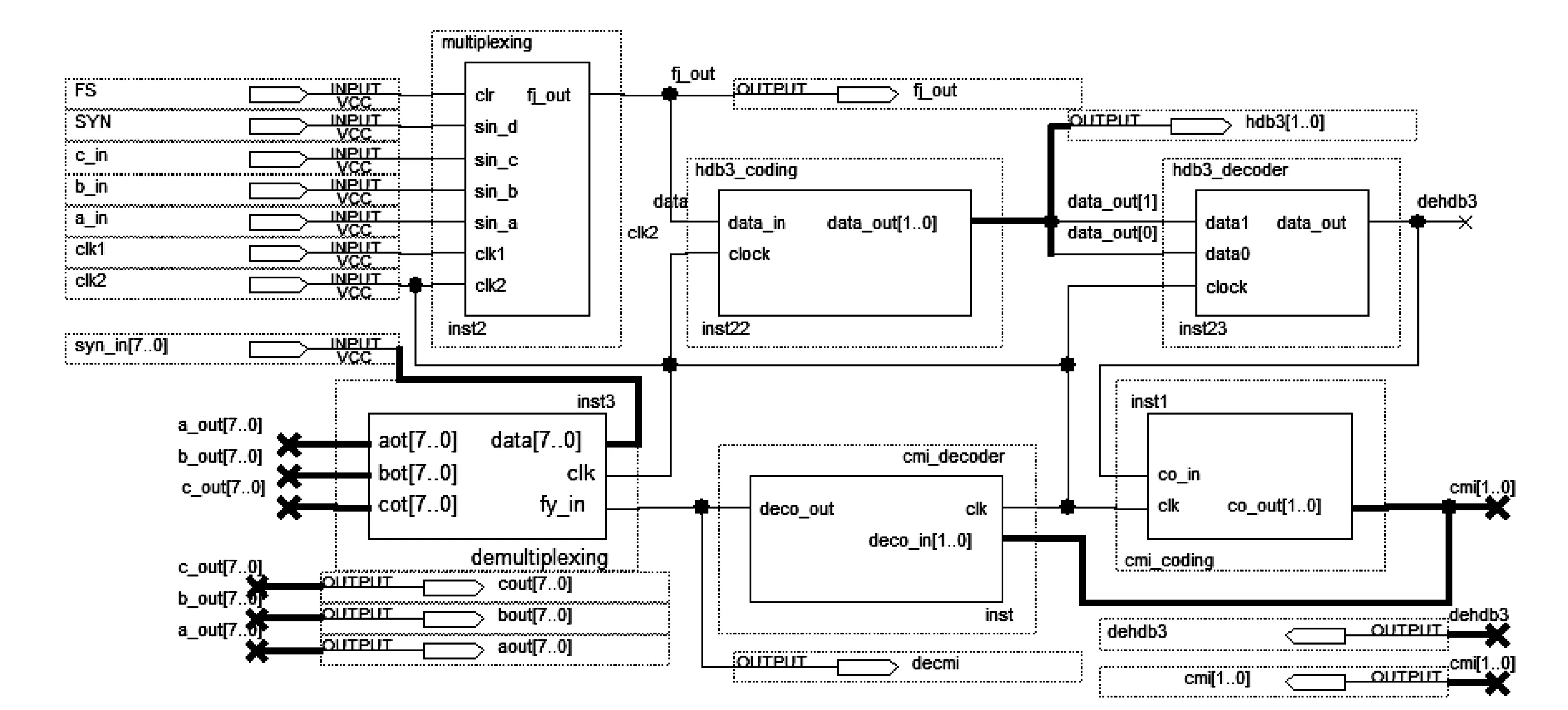

为了进一步确保系统设计的可实用性,将系统各组成模块按照自环工作状态连接起来,对系统各模块进行了整体仿真,完整的VHDL原理图如图6所示。帧同步信号和3路数字信号依次经过时分复用、HDB3编译码、CMI编译码和时分解复用输出,其中multiplexing、hdb3_coding、hdb3_decoder、cmi_coding、cmi_decoder和demultiplexing分别是时分复用、HDB3编码、HDB3译码、CMI编码、CMI译码和时分解复用模块。

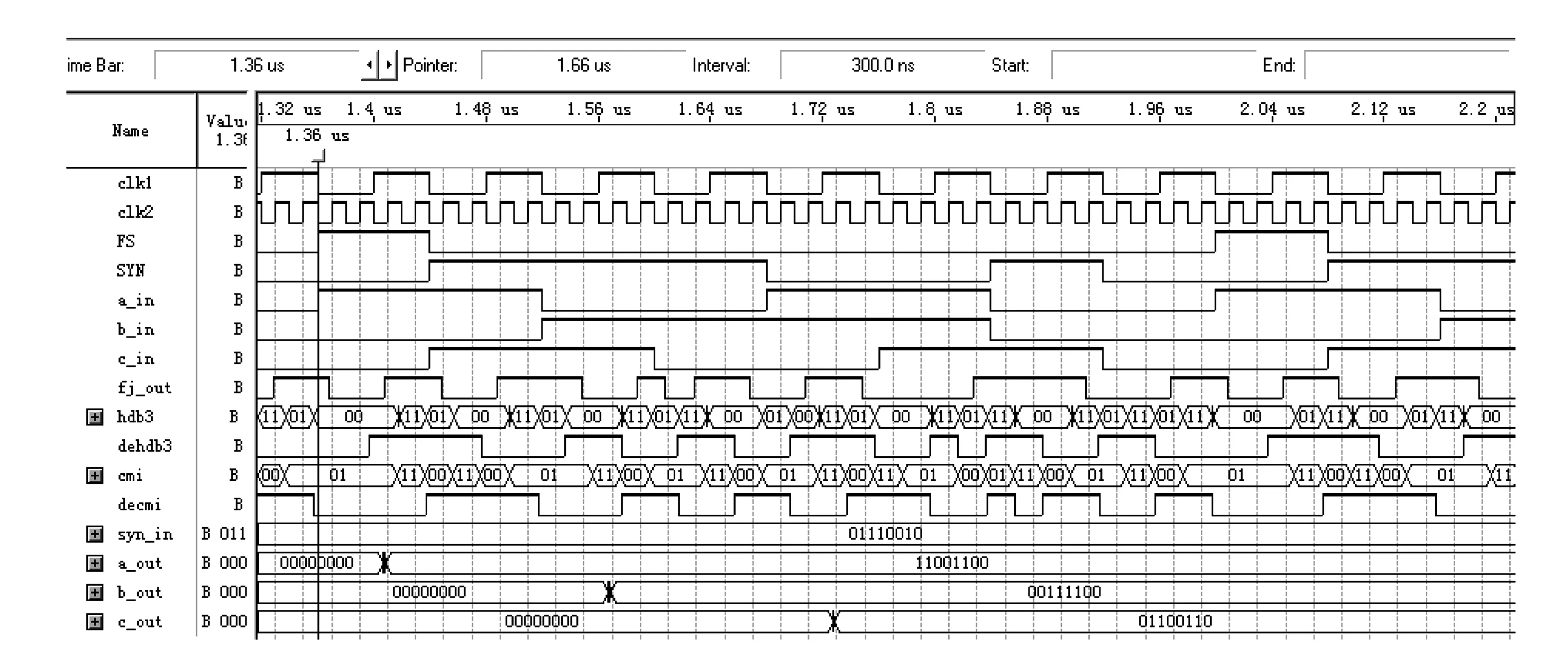

时序仿真结果如图7所示,其中clk1的频率是256kHz;clk2是频率为2048kHz的时钟(信号的传输速率);FS是时分复用的同步信号;SYN是帧同步码序列,固定为01110010;3路数字信号a_in、b_in、c_in分别是稳定的256kbps信号序列11001100、00111100、01100110;syn_in 是输入的帧同步码,用来检测帧同步码;fj_out是时分复用的输出信号;hdb3是HDB3编码输出信号;dehdb3是HDB3译码输出信号;cmi是CMI编码输出信号,decmi是CMI译码输出信号;a_out、b_out、c_out分别是时分解复用后输出的3路数字信号。由各信号的仿真结果可知,时分复用、HDB3编译码、CMI编译码、时分解复用的结果完全符合其功能原理,其中HDB3编译码器的设计各用了5个移位寄存器,所以其仿真结果分别延迟5个传输时钟。但由于时钟频率很高,所以影响不大。系统仿真最后并行输出3路信号11001100、00111100和01100110,与输入信号一致,满足设计要求。

图6 系统设计原理图

图7 系统时序仿真图

4 结 语

采用FPGA及VHDL 语言开发设计的一种多路数字信号光纤传输系统,其硬件设计采用了自顶而下的设计方法,整个系统具有结构简单,性能稳定,有效性、可靠性高。运用FPGA的设计,给调试带来方便,而且将电路各个模块集成到同一块FPGA芯片中,减少了外接元件,提高了系统集成度,缩短了开发周期。

[1]张宝福,谭笑,蒋慧娟. 光纤通信系统原理与实验教程[M]. 北京:电子工业出版社,2004.

[2]樊昌信,张甫翊,徐炳祥,等. 通信原理[M]. 北京:国防工业出版社,2006.

[3]贾惠彬,王兰勋. 基于CPLD的HDB3编译码器[J]. 电子科技,2005,9:37~40.

[4]吴海涛,陈英俊,梁迎春. 基于FPGA的HDB3编解码器设计[J]. 微计算机信息,2008,24(6-2):236~239.

[5]赵冬梅. CMI码的编译码电路设计及应用[J].机械管理开发,2006,2(1):90~91.

[6]张秀平,钟奇. 基于FPGA设计数字锁相环[J].河海大学常州分校学报,2007,21(3):51~54.

[编辑] 易国华

TP722;TN913.7

A

1673-1409(2009)03-N081-04

2009-06-10

蹇清平(1986-),女,2008年大学毕业,硕士生,现主要从事信号与信息处理方面的研究工作。