基于π型谐波控制网络的高效功率放大器设计

摘" 要: 为了提高通信系统的工作效率,提出一种基于F类理论的π型谐波控制网络。该网络利用直流偏置电路引入二次谐波短路点,从而降低谐波控制电路的复杂度;同时,能够确保二次、三次谐波阻抗不受后续基波匹配电路的影响。为避免寄生参数对晶体管芯漏极阻抗的影响,在π型谐波控制网络与晶体管之间引入L型寄生补偿电路,实现二次谐波阻抗趋近零、三次谐波阻抗趋近无穷大。为验证所设计网络的可行性,设计一款高效率F类功率放大器并进行仿真测试,结果表明在1.8~2.1 GHz工作频带内,饱和输出功率为43.21~44.84 dBm,增益为13.21~14.84 dB,功率附加效率为69.59%~73.54%。由此证明了所提出的π型谐波控制网络在高效率放大器设计中能够很好地满足各项性能指标。

关键词: F类功率放大器; 工作效率; π型谐波控制网络; 谐波阻抗; L型寄生补偿电路; 联合仿真

中图分类号: TN722⁃34" " " " " " " " " " " " " " "文献标识码: A" " " nbsp; " " " " " " " 文章编号: 1004⁃373X(2025)02⁃0009⁃05

Design of high⁃efficiency power amplifier based on π⁃type harmonic control network

WANG Yating1, YANG Ping1, WANG Jun2, BAI Tian2

(1. PLAC Laboratory, College of Physical Science and Technology, Central China Normal University, Wuhan 430079, China;

2. CICT Mobile Communication Technology Co., Ltd., Wuhan 430205, China)

Abstract: In order to enhance the efficiency of the communication system, a π⁃type harmonic control network based on class F theory is proposed. In this network, the DC bias circuit is used to introduce second harmonic short⁃circuit points, thereby simplifying the complexity of the harmonic control circuit. Simultaneously, it can ensure that the second and third harmonic impedance is not affected by the subsequent fundamental wave matching circuit. In order to mitigate the impact of parasitic parameters on transistor core leakage extreme impedance, an L⁃type parasitic compensation circuit is introduced between the π⁃type harmonic control network and the transistor, so as to realize the second harmonic impedance approaching zero and the third harmonic impedance approaching infinity. In order to validate the feasibility of the designed network, a high⁃efficiency class⁃F power amplifier is designed and simulated. The results show that within the operating frequency band of 1.8~2.1 GHz, the saturated output power is 43.21~44.84 dBm, the gain is 13.21~14.84 dB, and the power⁃added⁃efficiency is 69.59%~73.54%. It confirms that the proposed π⁃type harmonic control network can effectively meet performance requirements for the high⁃efficiency amplifier design.

Keywords: class⁃F power amplifier; work efficiency; π⁃type harmonic control network; harmonic impedance; L⁃type parasitic compensation circuit; joint simulation

0" 引" 言

随着第五代移动通信技术迅猛发展,现代高速通信系统对射频功率放大器提出了更为严苛的要求,这些要求涵盖了更高的效率、更大的输出功率以及更卓越的线性特性。近年来,学者们广泛而深入地探讨了高效率功放F类[1⁃5]和逆F类[6⁃9],力求在性能与技术上实现突破。与此同时,前两代半导体已无法满足射频设计需求,而基于新一代半导体GaN的功放[10⁃14]在发射机系统中展现出了广阔的应用前景,为通信行业带来了巨大的变革可能性。

F类功率放大器是通过调节功率放大器漏极的电压和电流波形来提高效率,然而,由于漏源电容和封装寄生参数[15]等因素的影响,漏极的二次和三次谐波阻抗可能会迅速偏离理想F类阻抗范围。因此,文献[15]中采用了双微带线进行寄生补偿,以减少封装寄生效应并提高阻抗匹配精度;而文献[16]中则提出了一种L型传输线寄生补偿技术,该技术具备可灵活调节参数的特点,从而实现晶体管漏端谐波阻抗达到F类或逆F类条件。本文采用了新提出的π型谐波控制网络和L型寄生补偿电路[16]构成的创新谐波控制电路,满足了F类功率放大器在晶体管漏极端口的谐波阻抗条件,实现了结构简单、高效率功放设计。

1" F类功率放大器基本原理

传统功率放大器中的晶体管在工作过程中会产生较多的谐波,存在一定的功率损耗,因此其工作效率较低。为了提高功率放大器的效率,降低各次谐波的功率是一种行之有效的方法,在时域上表现为晶体管漏端电压和电流的波形没有重叠。F类功率放大器在设计上具有独特的优势,可以通过增加谐波控制电路对晶体管输出电压或电流中的谐波成分进行精确调控[16]。这种调控方式使得漏端电流呈半正弦状波形且只包含基波电流和偶次谐波电流,而漏端电压则呈方波式波形且只包含基波电压和奇次谐波电压,可以实现对信号波形的整形,示意图如图1所示。通过这种方式可以降低晶体管的直流损耗,并实现功放的高效运转。在理想情况下,F类功率放大器可达到100%的能量利用效率,这意味着在输出信号中,几乎所有的输入能量都会被转换为有用能量,而不会以热量等形式损耗,这对于提高系统性能、降低能耗以及实现绿色通信具有重要意义。

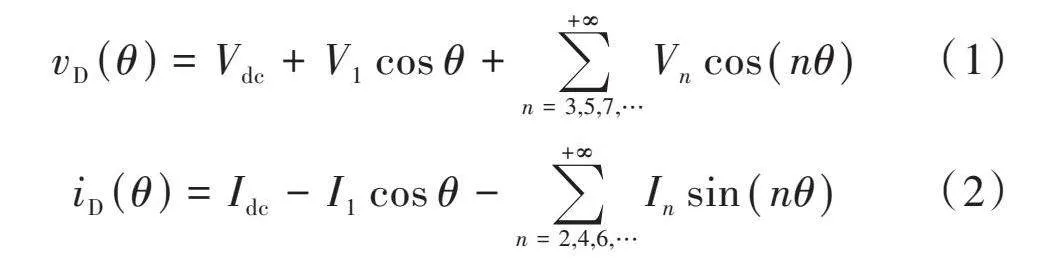

由傅里叶变换可得,F类功放的电压、电流分别为:

[vD(θ)=Vdc+V1cosθ+n=3,5,7,…+∞Vncosnθ] (1)

[iD(θ)=Idc-I1cosθ-n=2,4,6,…+∞Insinnθ] (2)

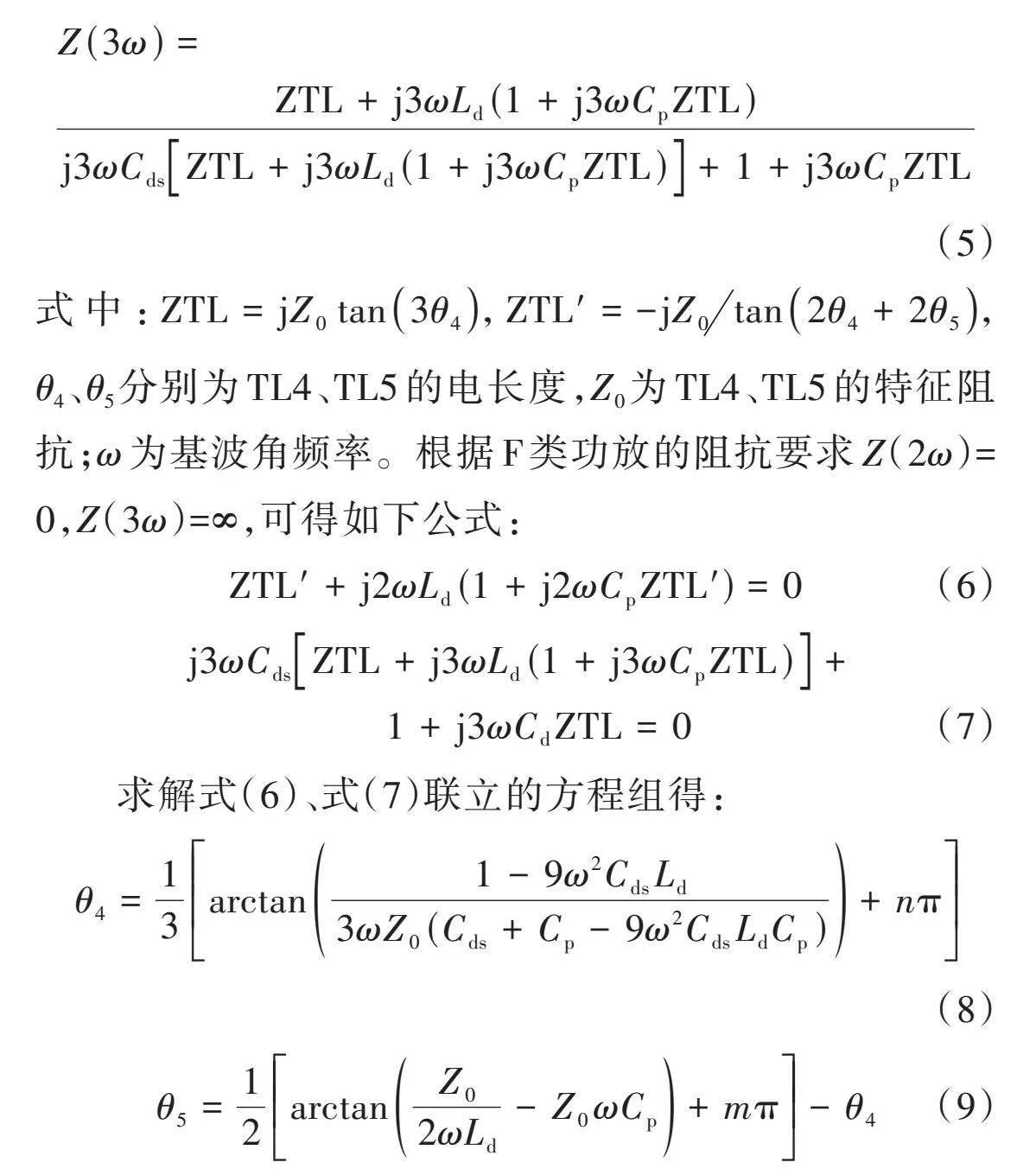

式中:[θ=ω0t],[ω0=2πf0],[f0]、[ω0]分别为基波频率、角频率;V1、I1为基波的系数;Vn、In为n次谐波的系数。电流系数前的负号表示电流和电压之间存在相位相反的关系。通过式(1)、式(2)可得出,F类功率放大器的阻抗符合式(3)时,功率放大器可实现100%的漏极效率。

[Zn=0, n为偶数∞, n为奇数] (3)

综上所述,要实现理想的F类功放并达到100%的漏极效率,必须满足以下条件:基波阻抗与最佳负载阻抗匹配,同时偶次谐波阻抗固定在史密斯圆图左侧的短路点,奇次谐波阻抗固定在右侧的开路点。这就需要设计复杂的谐波控制网络,然而在实际设计中,通常没有必要引入非常复杂的控制网络来控制所有谐波,此外,三次以上的谐波对F类功放的效率影响并不大。因此,本文后续分析将只针对二次和三次谐波进行控制。

2" F类功率放大器整体设计

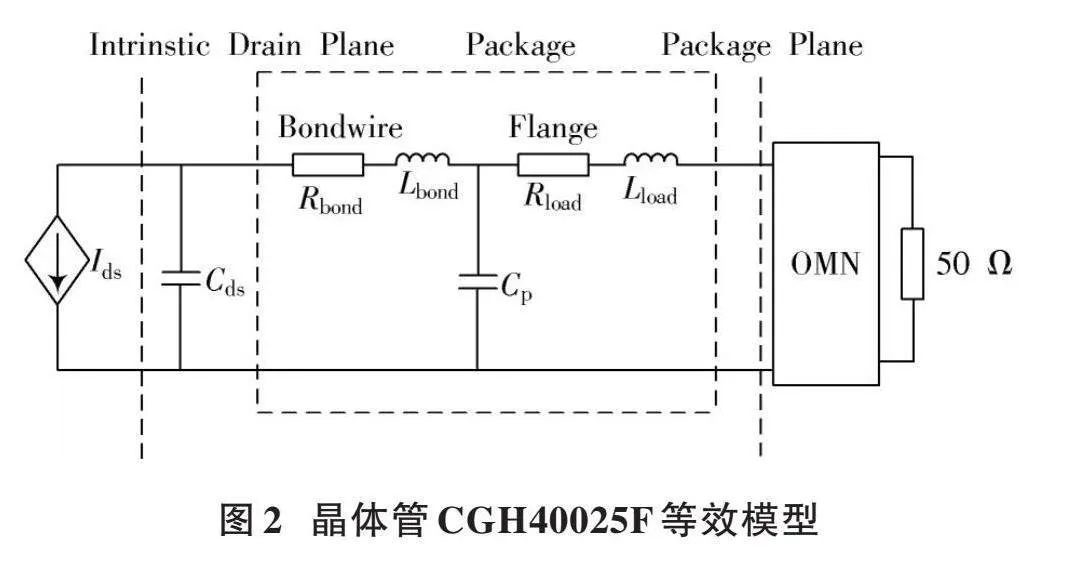

在设计目标功率放大器时,必须充分考虑晶体管的寄生效应。晶体管CGH40025F等效模型如图2所示,在功率放大器晶体管的输出端(封装表面)和实际漏极之间存在许多寄生元件,包括漏极和源极之间的寄生电容、封装引起的寄生电容和电感。这些参数会导致晶体管漏极端电压和电流波形偏移,从而降低功率放大器的效率,因此,在F类功率放大器设计中,必须考虑寄生参数对电路的影响。

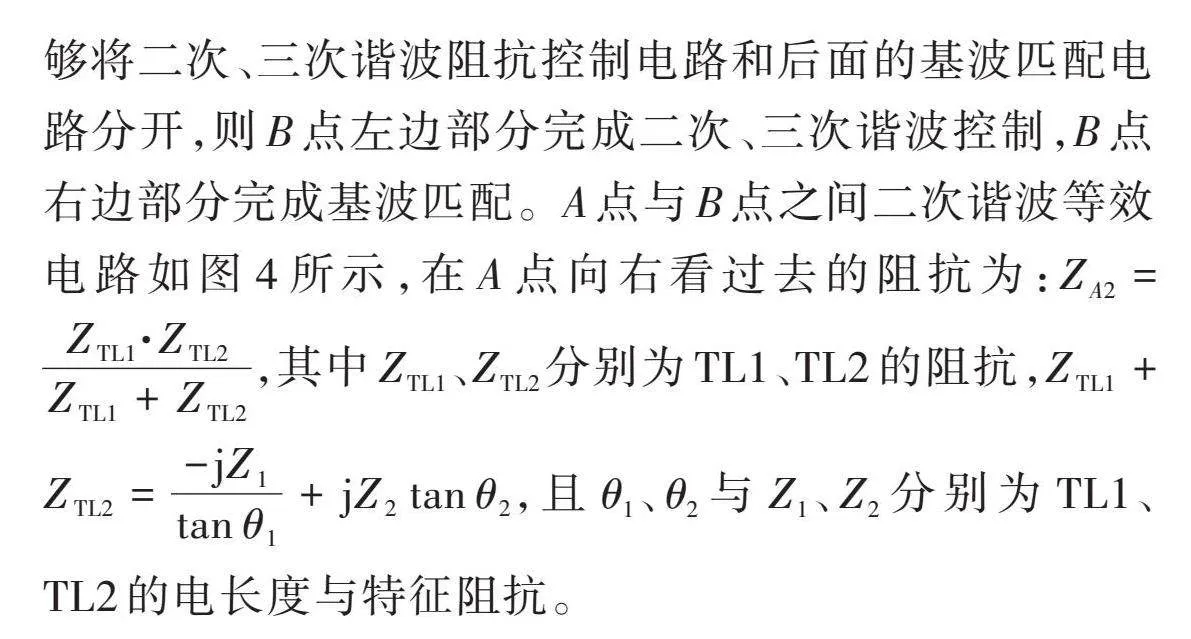

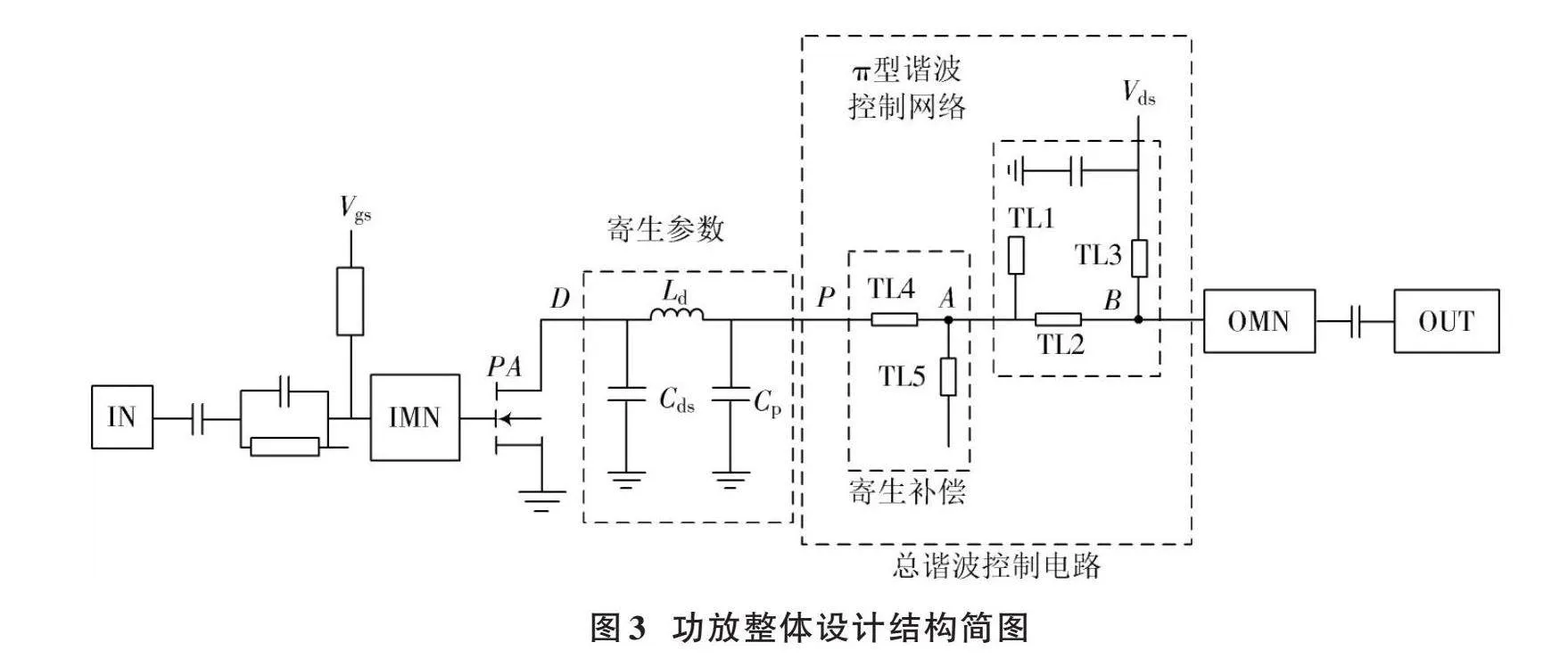

本文介绍了一种L型寄生补偿电路,以减少参数影响并提高功率放大器效率。实际的F类功率放大器的谐波控制电路包括本文设计的π型谐波控制网络和文献[16]提出的寄生补偿电路,以确保晶体管漏极谐波阻抗满足F类功率放大器的阻抗条件。功放整体设计结构简图如图3所示。图3中,晶体管漏极到封装面的寄生分量中,漏源寄生电容Cds与封装寄生电容Cp决定了到地寄生电容大小,键合线电感为串联电感的主要部分。因此,可以将晶体管漏极D与封装面P之间的寄生分量简化成图中寄生参数部分。图3中总谐波控制电路框中π型谐波控制网络为本文提出的谐波控制网络,A点与B点之间电路实现二次谐波开路、三次谐波短路,加入的寄生补偿电路与晶体管寄生参数实现二次、三次谐波阻抗变换,在D点二次谐波短路、三次谐波开路。TL1为终端开路微带线,其波长为[λ12](λ为基波波长),对于三次谐波为[λ34](λ3为三次谐波波长),通过阻抗变换可知三次谐波在A点短路。由“谐波陷阱”概念知,由于A点提供一个三次谐波短路点的存在,使晶体管漏端向右看过去的三次谐波阻抗只与漏端和A点之间电路有关,与A的右边电路无关。TL3为终端短路微带线,其电长度为[λ4],对于二次谐波为[λ22](λ2为二次谐波波长),通过阻抗变换知二次谐波在B点短路。同理,对于二次谐波而言,晶体管漏端向右看过去的二次谐波阻抗只与漏端和B点之间电路有关,所以此电路能够将二次、三次谐波阻抗控制电路和后面的基波匹配电路分开,则B点左边部分完成二次、三次谐波控制,B点右边部分完成基波匹配。A点与B点之间二次谐波等效电路如图4所示,在A点向右看过去的阻抗为:[ZA2=ZTL1·ZTL2ZTL1+ZTL2],其中ZTL1、ZTL2分别为TL1、TL2的阻抗,[ZTL1+ZTL2=-jZ1tanθ1+jZ2tanθ2],且θ1、θ2与Z1、Z2分别为TL1、TL2的电长度与特征阻抗。

B点之间等效电路图

二次谐波在A点实现开路的条件为ZA2=∞,令ZTL1+ZTL2=0,取Z1=Z2=50 Ω,得θ2=15°,实现了ZA2=∞。

在以上电路中,A点已满足逆F类功率放大器的谐波阻抗要求。如果设计F类功率放大器,需要使用寄生补偿电路和寄生参数来完成阻抗变换;而如果设计逆F类功率放大器,则只需利用寄生补偿电路来抵消寄生参数的影响即可。本文旨在设计F类功率放大器,通过L型结构的微带线寄生补偿电路和π型寄生电路实现从A点到D点的二次、三次谐波分量的阻抗变换。图5所示为二次谐波和三次谐波的等效电路。对于三次谐波,等效电路只包含TL4;而对于二次谐波,等效电路则包括TL4和TL5。首先通过调节TL4来实现三次谐波阻抗的变换,然后固定TL4,并调节TL5来实现二次谐波阻抗的变换。从漏端向右看过去的二次谐波和三次谐波输入阻抗公式如下:

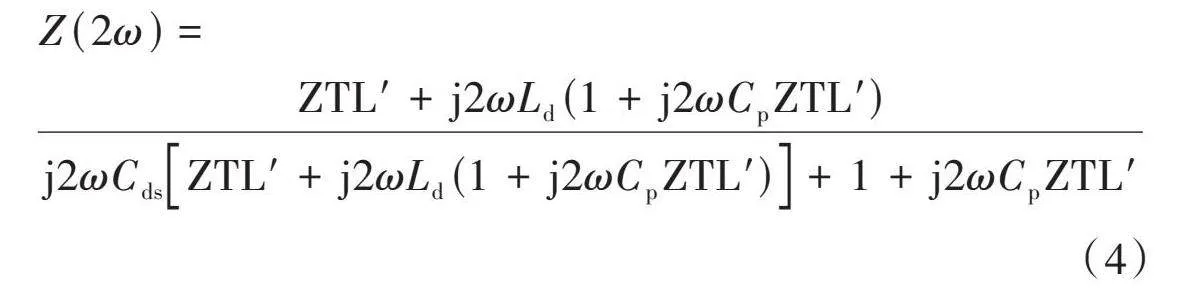

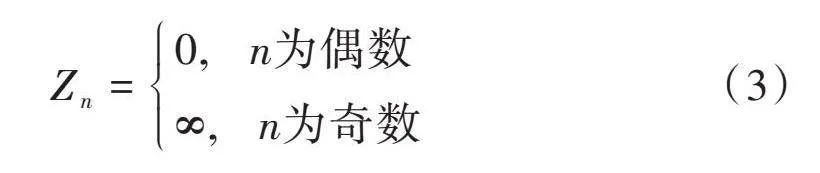

[Z(2ω)=ZTL'+j2ωLd(1+j2ωCpZTL')j2ωCdsZTL'+j2ωLd(1+j2ωCpZTL')+1+j2ωCpZTL'] (4)

[Z(3ω)=ZTL+j3ωLd(1+j3ωCpZTL)j3ωCdsZTL+j3ωLd(1+j3ωCpZTL)+1+j3ωCpZTL] (5)

式中:[ZTL=jZ0tan3θ4],[ZTL′=-jZ0tan2θ4+2θ5],θ4、θ5分别为TL4、TL5的电长度,Z0为TL4、TL5的特征阻抗;ω为基波角频率。根据F类功放的阻抗要求Z(2ω)=0,Z(3ω)=∞,可得如下公式:

[ZTL'+j2ωLd(1+j2ωCpZTL')=0] (6)

[j3ωCdsZTL+j3ωLd(1+j3ωCpZTL)+" " " " " " " " " " " "1+j3ωCdZTL=0] (7)

求解式(6)、式(7)联立的方程组得:

[θ4=13arctan1-9ω2CdsLd3ωZ0(Cds+Cp-9ω2CdsLdCp)+nπ] (8)

[θ5=12arctanZ02ωLd-Z0ωCp+mπ-θ4] (9)

式中:m和n为任意整数,需要选择合适的m和n以确保θ4和θ5的最优化。该结果为设计提供了一个优化的初始范围,在电路中需要进行一定的优化调整。

3" F类功率放大器仿真及结果

通常情况下,F类功率放大器的偏置设定在B类状态,本文基于25 W GaN HEMT CGH40025F晶体管进行高效率放大器设计,功率放大管的寄生参数列于表1中。选择将栅极的偏置电压设定在接近其阈值电压的-3 V,漏极的偏置电压设定为28 V。当晶体管增益较大时,可能会出现不稳定现象,导致自激振荡。因此,在设计放大器之前,需要确保功放管在设计频段1.8~2.1 GHz内能够稳定工作。

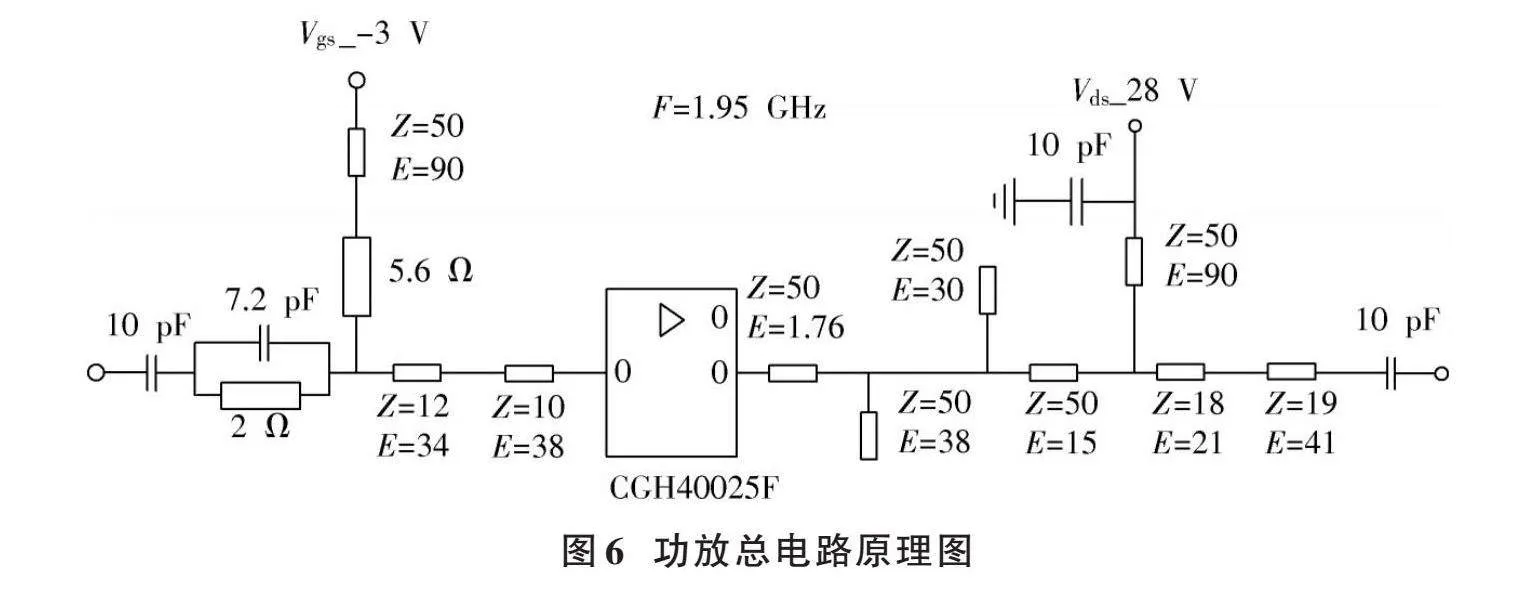

为了保证电路工作的稳定性,在功放输入通路中加入了RC并联稳定电路,并且在栅极偏置电路中加入了5.6 Ω电阻。接下来需要设计输入输出匹配电路,使输入输出信号能够高效传输。为了获得最佳匹配效果,使用ADS的Load⁃Pull和Source⁃Pull进行迭代操作以得到最佳阻抗。在1.8 GHz、1.95 GHz和2.1 GHz三个不同频率下进行仿真,以获取最佳的负载阻抗和源阻抗区域,并在此基础上综合权衡,选择最佳阻抗数值。输入和输出匹配电路均采用两段不同阻抗的传输线构成的匹配网络,借助史密斯圆图计算出匹配网络的具体参数。电路设计中,隔直电容选用村田电容GRM18中的10 pF电容,并使用RO4350B板材进行仿真。最终得到的功放总电路整体设计原理图如图6所示。

联合仿真测试结果如图7所示,在1.8~2.1 GHz工作频段内,输入功率为30 dBm时,饱和输出功率范围为43.21~44.84 dBm,增益范围为13.21~14.84 dB,功率附加效率为69.59%~73.54%。

为了更全面地了解所设计的F类功率放大器的性能,对1.8~2.1 GHz以20 MHz的间隔进行晶体管漏断电压电流波形扫描,饱和输出功率下晶体管漏端处的电压电流波形如图8所示。观察图8可知,晶体管漏端的电压电流波形呈现出半正弦电流和方波电压输出的特点。这一结果基本实现了F类功率放大器的理想输出特性,证明了本文设计的正确性和可行性。

为了更直观地展示所设计功率放大器的性能,将其与已发表文献数据进行了对比,如表2所示。结果表明,采用π型谐波控制网络结合L型寄生补偿电路的设计方法,在提高功率放大器性能方面具有一定优势。

4" 结" 论

本文主要提出了一种π型谐波控制网络,该网络结构简洁,能够降低电路复杂度并提高系统性能。根据所提出的网络与L型寄生补偿电路进行设计,成功设计一种功率放大器。ADS联合仿真结果表明:在1.8~2.1 GHz工作频带内,输入功率为30 dBm时,饱和输出功率为43.21~44.84 dBm,增益为13.21~14.84 dB,功率附加效率为69.59%~73.54%。

参考文献

[1] 刘国华,王维荣,范凯凯,等.高效率F类Doherty功率放大器研究[J].实验室研究与探索,2021,40(12):1⁃4.

[2] PIRASTEH A, ROSHANI S, ROSHANI S. Design of a miniaturized class F power amplifier using capacitor loaded transmission lines [J]. Frequenz, 2020, 74(3/4): 180.

[3] SHAMIL H. High efficiency class F power amplifier design for GSM system [J]. International journal of computer applications, 2019, 178(37): 38⁃42.

[4] DHAR S K, SHARMA T, DARRAJI R, et al. Investigation of input⁃output waveform engineered continuous inverse class F power amplifiers [J]. IEEE transactions on microwave theory and techniques, 2019, 67(9): 3547⁃3561.

[5] SHARMA T, ROBERTS J, DARRAJI R, et al. Novel integrated class F power amplifier design for RF power infrastructure applications [J]. IEEE access, 2018(6): 75650⁃75659.

[6] MOON J, JEE S, KIM J, et al. Investigation of a class⁃F⁃1 power amplifier with a nonlinear output capacitor [C]// 2011 6th European Microwave Integrated Circuit Conference. Manchester, UK: IEEE, 2011: 124⁃127.

[7] SAJEDIN M, ELFERGANI I, RODRIGUEZ J, et al. Multi⁃resonant class⁃F power amplifier design for 5G cellular networks [J]. Radio engineering, 2021, 30: 372⁃380.

[8] HUANG H, ZHANG B, YU C, et al. Design of inverse class⁃F power amplifier based on dual transmission line with 87.4% drain efficiency [J]. Microwave amp; optical technology letters, 2017, 59(12): 3010⁃3014.

[9] XU J X, ZHANG X Y, SONG X Q. High⁃efficiency filter⁃integrated class⁃F power amplifier based on dielectric resonator [J]. IEEE microwave amp; wireless components letters, 2017, 27(9): 827⁃828.

[10] 孙伟锋,张波,肖胜安,等.功率半导体器件与功率集成技术的发展现状及展望[J].中国科学:信息科学,2012,42(12):1616⁃1630.

[11] 郑新.三代半导体功率器件的特点与应用分析[J].现代雷达,2008(7):10⁃17.

[12] 郑佳欣.AlGaN/GaN高电子迁移率晶体管模型研究与功率放大器设计[D].西安:西安电子科技大学,2018.

[13] OTSUKA N, KAWAI Y, NAGAI S. Recent progress in GaN devices for power and integrated circuit [C]// 2017 IEEE 12th International Conference on ASIC (ASICON). Guiyang: IEEE, 2017: 928⁃931.

[14] POSTHUMA N E, YOU S, STOFFELS S, et al. Gate architecture design for enhancement mode p⁃GaN gate HEMTs for 200 and 650 V applications [C]// 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD). Chicago, IL, USA: IEEE, 2018: 188⁃191.

[15] CHENG Z Q, XUAN X F, KE H J, et al. Design of 0.8~2.7 GHz high power class⁃F harmonic⁃tuned power amplifier with parasitic compensation circuit [J]. Active and passive electronic components, 2017, 2017: 1⁃8.

[16] 朱守奎.高效率GaN HEMT F类/逆F类功率放大器研究和设计[D].天津:天津大学,2017.

[17] 程晖.基于CGH40010F的连续F类功率放大器仿真与设计[J].现代电子技术,2020,43(16):26⁃29.

[18] 王宋业,程知群,张志维,等.F类可重构功率放大器设计[J].微波学报,2023,39(2):39⁃42.

[19] 刘文进,张野,南敬昌,等.1~3 GHz连续类功率放大器的设计[J].电子元件与材料,2023,42(6):736⁃742.