一种带Cache加速的HyperRAM控制器设计与验证

摘 "要: 针对目前可穿戴设备上对存储设备性能要求高、体积小、功耗低等问题,在FPGA上实现了一款可拓展的高性能HyperRAM控制器,并引入Cache缓存加速设计,以提高对频繁访问数据的命中率和优化存储器访问模式,实现更高速的数据传输和优化的系统性能。运用UVM验证方法学和FPGA进行验证,结果表明,带有Cache缓存的HyperRAM控制器相较于普通HyperRAM,在读写连续地址时性能提高61%,并具有较好的可靠性与有效性,可为嵌入式系统提供高效、灵活的存储器解决方案。

关键词: HyperRAM控制器; Cache缓存; 可穿戴设备; 存储器; UVM验证方法学; FPGA

中图分类号: TN492⁃34; TP333 " " " " " " " " " "文献标识码: A " " " " " " " " " " 文章编号: 1004⁃373X(2024)06⁃0091⁃06

Design and verification of HyperRAM controller with Cache acceleration

ZOU Min1, LU Aoyu1, ZOU Wanghui1, YU Hua2

(1. School of Physics amp; Electronic Science, Changsha University of Science and Technology, Changsha 410114, China;

2. Guangdong Synwit Integrated Circuit Co., Ltd., Changsha 410205, China)

Abstract: In allusion to the problems of high⁃performance requirements, small size and low power consumption of storage devices in wearable devices, a scalable high⁃performance HyperRAM controller is implemented on FPGA, and the design of Cache acceleration is introduced to improve the hit rate of frequently accessed data and optimize the memory access mode, so as to realize higher⁃speed data transmission and optimized system performance. By means of UVM verification methodology and FPGA verification, the results show that in comparison with ordinary HyperRAM, the performance of the HyperRAM controller with Cache cache is improved by 61% when reading and writing continuous addresses, and has good reliability and effectiveness, which can provide an efficient and flexible memory solution for embedded systems.

Keywords: HyperRAM controller; Cache cache; wearable devices; memory; UVM validation methodology; FPGA

0 "引 "言

随着嵌入式系统的不断演进,CPU与内存之间数据交换速率要求越来越高,对存储器接口的要求日益增加[1⁃2]。为满足数据快速传输和处理的需求,新一代存储器技术应运而生,其中包括了备受瞩目的HyperRAM存储器。与传统存储器技术相比,HyperRAM具有更高的读写速度和更低的访问延迟,适用于对数据访问速度要求较高的应用场景,使其成为各种嵌入式系统的理想选择[3⁃4]。

然而,在大规模数据处理和频繁读写操作的情况下,HyperRAM的原始接口可能面临性能瓶颈。Cache缓冲作为一种常见的高速存储器,被广泛应用于处理器和系统的设计中[5],允许暂存频繁读取的数据,从而减少对主存储器的频繁访问,提高数据读写效率和性能。将Cache缓冲引入HyperRAM存储器接口,有望进一步提高对频繁访问的数据的命中率,优化存储器访问模式,从而实现更高速的数据传输和更优化的系统性能[6⁃7]。

本文基于HyperRAM的逻辑功能,设计了一种基于AMBA总线的HyperRAM控制器,同时内部设计了高速缓存Cache模块,以提高读写速率,降低存储器的访问频率。经测试,所设计的控制器能稳定工作在166 MHz频率下,同时写入数据与读出数据能够保持一致,数据未出现丢帧、误码现象,系统性能稳定可靠。

1 "HyperRAM控制器的设计

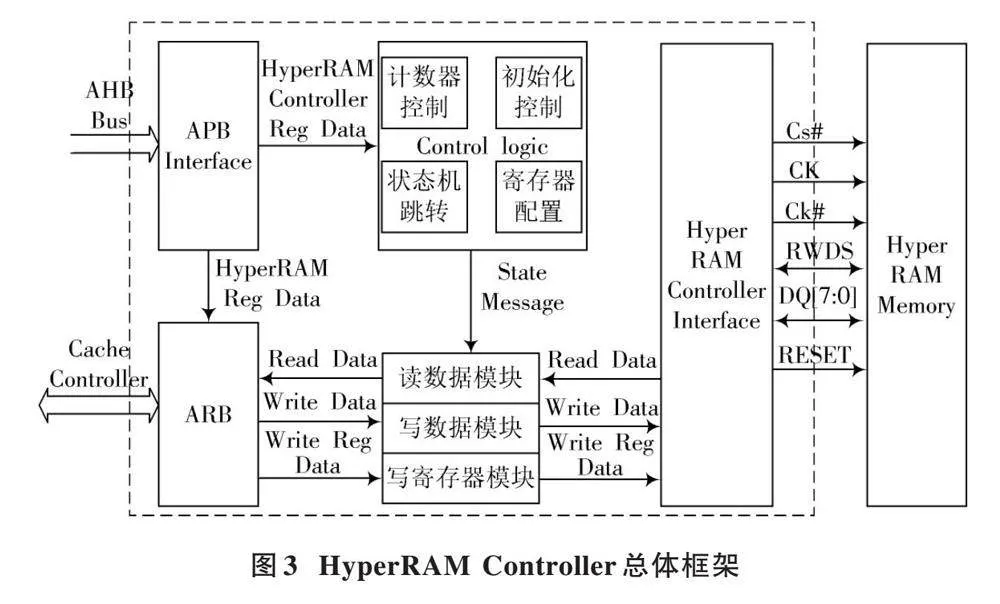

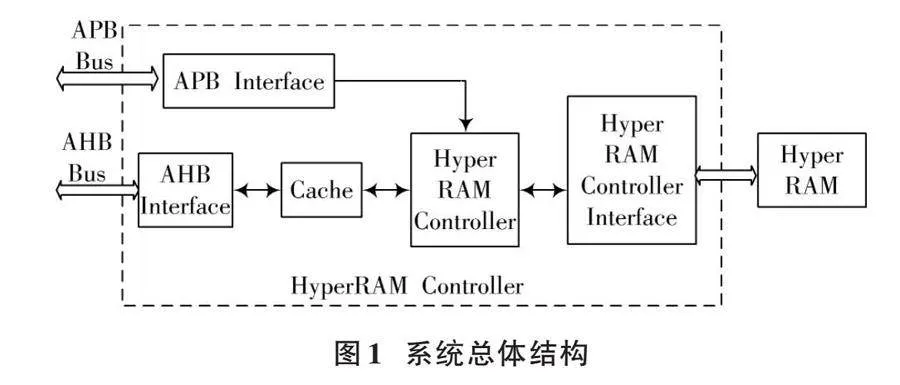

图1为本文HyperRAM控制器设计的总体框图。HyperRAM控制器由AHB Interface模块、APB Interface模块、Cache模块、HyperRAM Controller模块以及HyperRAM Controller Interface模块组成。其中APB总线提供寄存器配置,AHB总线提供读写命令以及读写数据。

系统的工作过程为:在上电后,通过AHB Interface模块解析读写信号,如果Cache模块命中,则直接从Cache模块完成操作;如果Cache模块未命中,则根据Cache模块不同的情况,通过HyperRAM Controller模块产生信号,经过HyperRAM Interface模块时,通过HyperRAM完成数据交互,再通过Cache模块输出。而APB总线则产生寄存器配置信号,使Cache模块以及HyperRAM Controller模块工作在不同的模式下。

1.1 "Cache设计

缓存容量越大,可以存储越多的主存数据,提高命中率,但会增加成本和访问时间[8]。本文选取64 KB的缓存容量,既能与主存容量相匹配,又不会因为容量太大而造成成本高;设置256 bit的行大小,能够与主存行大小相匹配,使设计简化。同时,组相连映射相对直接映射与全相连映射具有更低的硬件成本、更少的Cache颠簸。两路组相连映射具有设计复杂度小、速度快的特点。不良的缓存替换策略会引发多种性能问题,包括应用程序执行时间长、内存利用率低、频繁替换和可能的内存不足错误[9⁃10]。而LRU(最近最少使用)替换策略更加的合理,更适合本次设计,命中率提升更大。

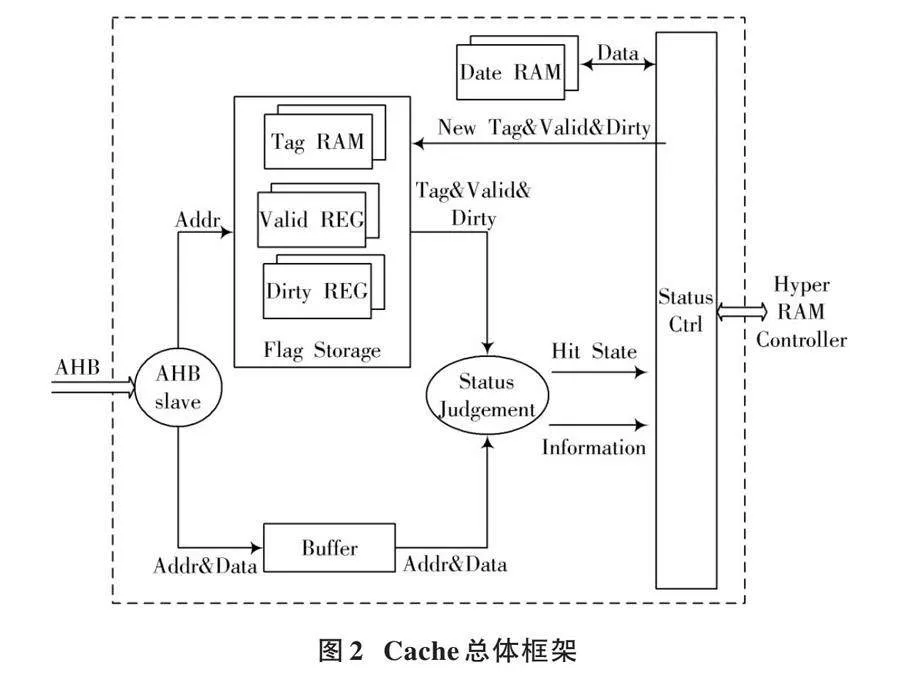

因此,本文Cache设计采用两路组相连映射缓存、带有LRU替换策略,总容量为64 KB,Cache行大小为256 bit。Cache的设计结构如图2所示。

当数据信号地址信息被AHB slave接收到后,与Flag Storage进行状态的比对,同时存入Buffer等待第二周期的数据,收到总线上的数据后,进入Status Judgement进行状态判断,如未命中则通过端口与HyperRAM通信获取所需数据,否则直接从DataRAM修改目标数据。

1.2 "HyperRAM Controller模块的设计

HyperRAM Controller模块主要有3个端口通信:ARB端口与Cache模块通信,实现数据交互;在APB端口进行寄存器配置;HyperBus端口与存储器通信。控制逻辑会对整体进行控制,如寄存器配置、状态机的跳转、计数器的配置、初始化控制等。存储器采用CYPRESS公司旗下的S27KS0641系列HyperRAM芯片。该款芯片具有功耗低、体积小、易于集成等特点,非常适合本次设计。整体设计图如图3所示。

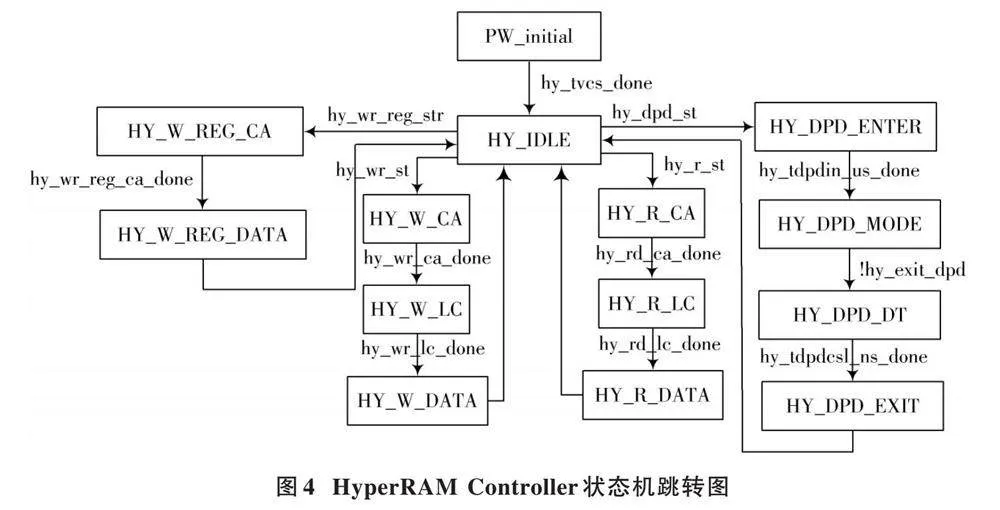

图4为HyperRAM Controller状态机跳转图,实现过程如下:

步骤1:PW_initial→HY_IDLE:控制器上电复位过程。在存储器上电复位完成后,控制器会发起短暂的自启动过程,完成特定的寄存器配置,以保证控制器的功能与存储器一致。

步骤2:HY_IDLE→HY_W_CA→HY_W_LC→HY_

W_DATA:控制器写数据过程。首先发送6个字节的CA命令,再根据RWDS信号的不同发起一段延迟,最后接收读数据,完成后返回HY_IDLE状态。

步骤3:HY_IDLE→HY_R_CA→HY_R_LC→HY_

R_DATA:控制器读数据过程。该过程与写数据过程类似。

步骤4:HY_IDLE→HY_W_REG_CA→HY_W_REG_DATA:控制器写寄存器过程。在接收到写寄存器命令后,首先发送6个字节的CA命令,随后发送配置寄存器的数据,完成后返回HY_IDLE状态。

步骤5:HY_IDLE→HY_DPD_ENTER→HY_DPD_

MODE→HY_DPD_DT→HY_DPD_EXIT:深度掉电模式(DPD模式)。收到进入深度掉电模式的操作后,控制器往存储器中CR0[15]写入“0”,使得存储器进入深度掉电模式。直到收到下一次对存储器的操作,或者复位操作,才会退出DPD模式。

2 "HyperRAM控制器的验证

2.1 "UVM验证平台搭建

在Linux平台下,搭建UVM验证平台框架,如图5所示。测试平台通过Interface发送数据,Monitor监测数据输入与响应,与参考模型输出的数据进行比对。待测设计(即RTL代码,下文简称DUT)通过连接S27KL0641芯片的模型,以产生相应的波形,通过VCS编译代码、Verdi查看波形。

2.2 "UVM验证及结果分析

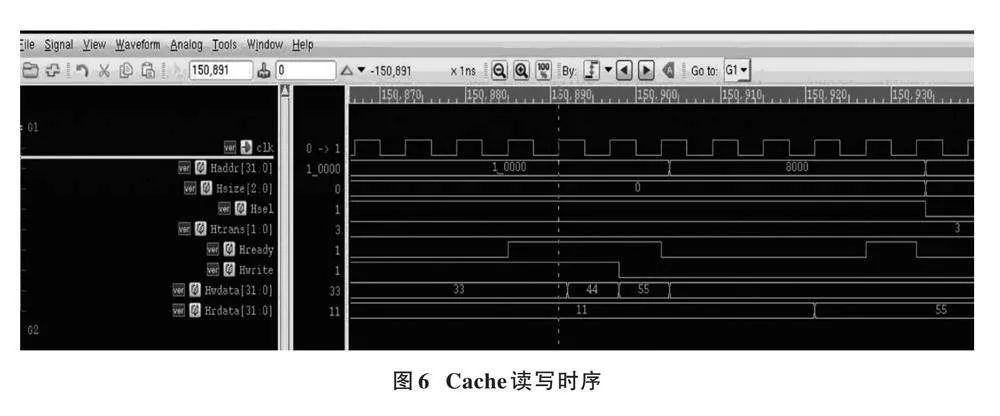

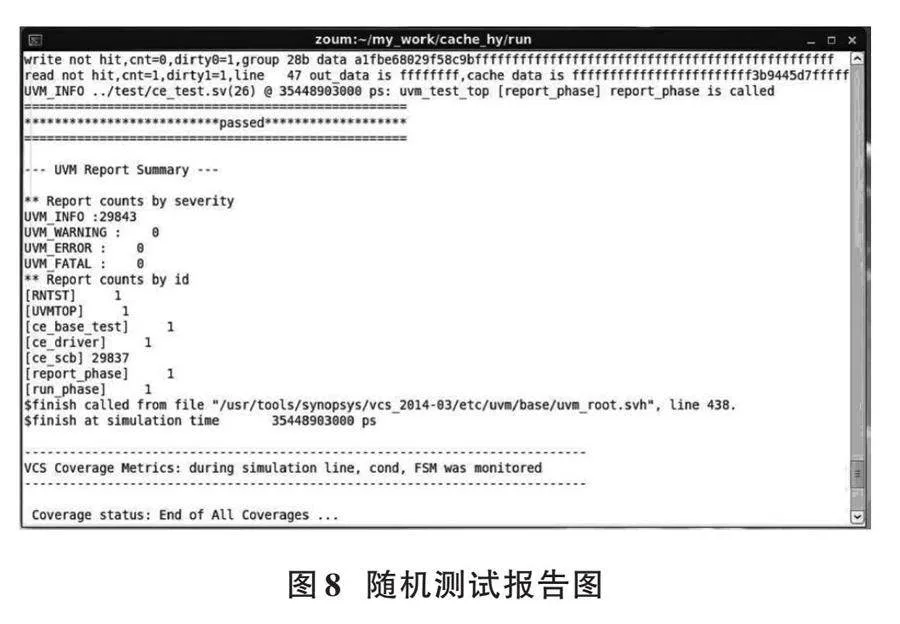

搭建验证平台后,对设计进行验证功能点分析,找到设计中需要着重关注的功能点。针对相应的验证功能点编写相应的UVM测试,确保设计功能的正确性与完整性。设置时钟频率为166 MHz,并运行相应测试,部分运行结果如图6、图7所示。

图6中,在15 885 ns时钟上升沿时总线发起写指令,向地址1_0000写入数据8’h44;随后在15 891 ns时钟上升沿时对相同地址写入8’h55,以替换原有数据8’h44,能测试Cache替换是否正常。后15 897 ns时钟上升沿时读取地址1_0000的数据,输出结果为8’h55,达到预期目标。图7中,在414 363 ns时,Cache模块发来写信号,而后经过处理信号,控制器开始向存储器发送写数据指令;在414 417 ns时,Cache模块发送读指令。控制器在完成写指令后,紧接着完成总线上的读数据指令,并将读取到的数据输出给Cache。经过分析,达到预期目标。在图8中,不加约束进行随机化测试,从报告中可以看出,测试环境共运行了约35 000 μs,Scoreboard共比对了29 837次,DUT输出的结果与参考模型数据结果一致,最终结果通过。

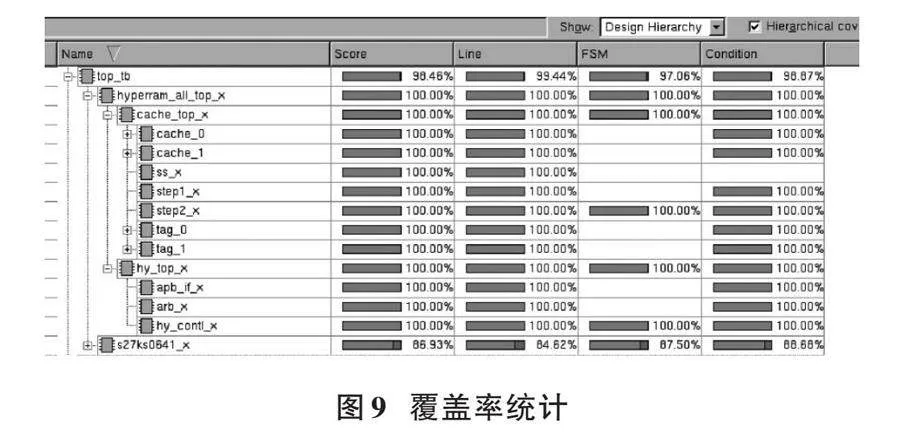

经过随机测试的检验和定向测试的添补,整体覆盖率如图9所示。

图9中,代码覆盖率达到了98.46%,其中行覆盖率达到了99.44%,状态机覆盖率达到了97.06%,条件覆盖率达到了98.87%。因为在读寄存器的操作中,设计时直接从控制器返回了寄存器数据,并没有读取存储器的过程,所以IP的覆盖率没有达到100%,但控制器的设计总体达到了100%,故此验证达到预期目标。

2.3 "FPGA验证及分析

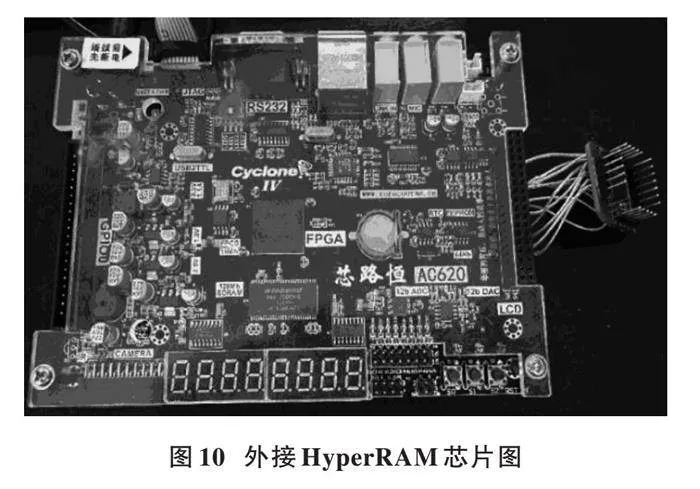

为了进一步验证设计的正确性,需要进行FPGA实验。本文中制作了一个附加的PCB板,集成了S27KS0641系列HyperRAM芯片。通过跳线的方法与FPGA开发板的I/O口连接,如图10所示。

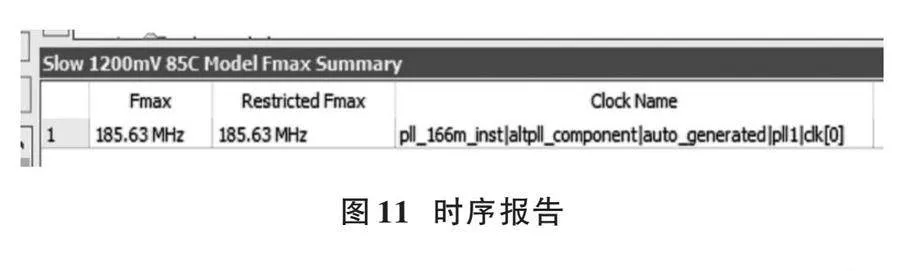

连接好开发板后,利用Quartus Ⅱ EDA工具进行了综合、时序约束、生成网表等操作[11]。处理后的结果如图11所示,报告表明,系统最高可以达到185 MHz的频率设计要求。

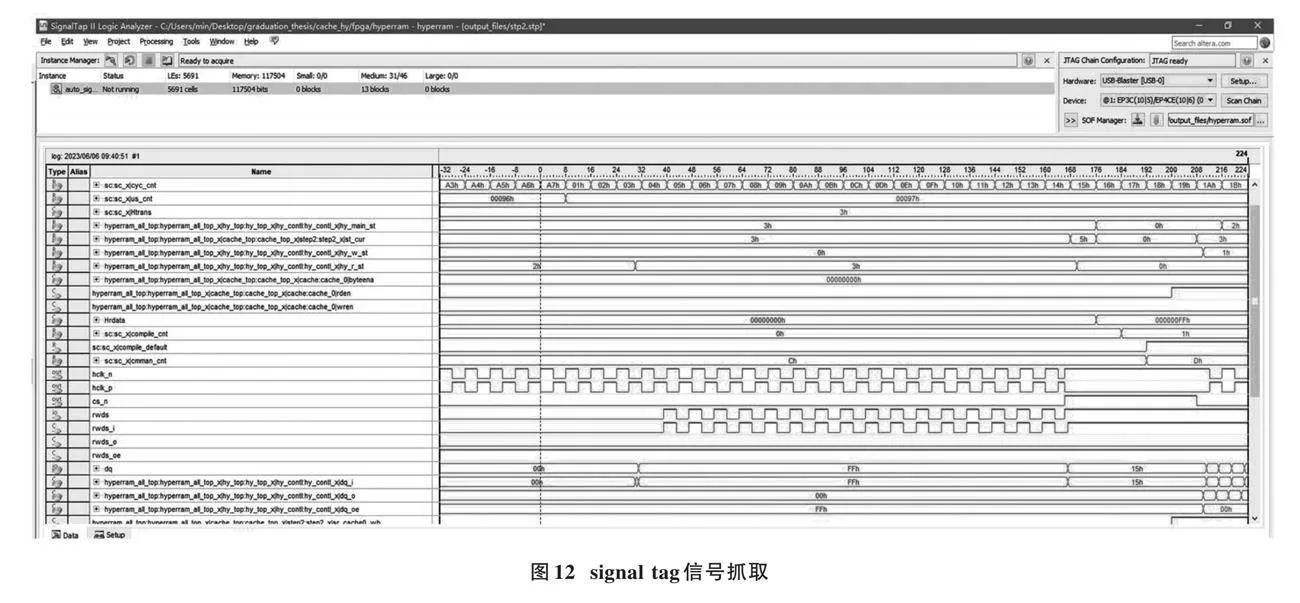

在将设计下载到开发板时,需要考虑硬件对高速电路和时钟的影响。由于硬件环境可能引入信号传播延迟、时钟抖动等不稳定因素,以及PLL生成的时钟占空比的可能波动,因此为确保稳定的测试和评估,有必要适当地降低测试频率。设置工程的系统时钟为100 MHz时,通过Quartus Ⅱ软件中的signal tag工具,抓取信号的波形,最终测试结果如图12所示。测试结果表明,本文设计的HyperRAM控制器具有可实现性,能够稳定运行,达到工程标准。

2.4 "性能分析

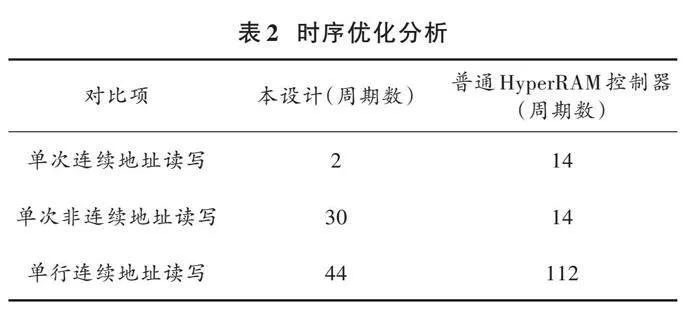

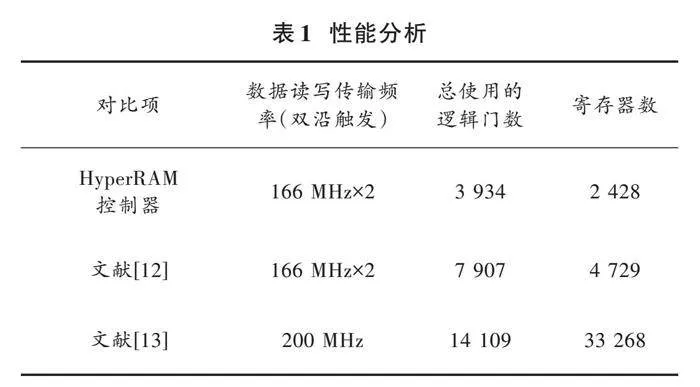

程序下载后,资源报告中显示了有关HyperRAM控制器测试项目的主要信息,如表1所示。同为存储器系列产品,DDR2 SDRAM因其具有低成本、高速、大容量等高性价比优点,目前仍被广泛运用在各个领域中[12⁃13]。本文与文献[12⁃13]中DDR2 SDRAM控制器相比,运行在同样的时钟频率下,却使用了更少的逻辑门、更少的寄存器数量,更适合体积小、易于集成的嵌入式系统。

同时由于本文设计集成了Cache模块,与普通的HyperRAM控制器相比,虽然在不连续的地址下,需要一次读取一个数据(256 bit),以及增加了1个周期用于判断命中,会比普通控制器慢;但在工程中连续的地址下,本设计提升了61%的读写数据所需的周期数。时序优化分析表如表2所示。

3 "结 "语

本文设计一款带有Cache加速模块的HyperRAM控制器,通过Linux下的VCS平台,完成了RTL代码设计,并基于UVM验证方法学搭建了验证环境。验证结果表明,所设计控制器通过了验证并且覆盖率总体达到了99%。基于AC620开发板完成了FPGA验证,验证结果显示,本设计实现了HyperRAM接口控制功能,且在数据读写方面表现一致可靠,数据传输方面表现稳定,具有一定的应用价值。

参考文献

[1] MA J H, LIU H F, YANG N, et al. Circuit⁃level memory technologies and applications based on 2D materials [J]. Advanced materials, 2022, 34(48): e2202371.

[2] 王泉,杨天若,朱大开,等.智能嵌入式系统结构与软件关键技术专题序言[J].西安电子科技大学学报,2021,48(6):1⁃7.

[3] LUZA L M, SÖDERSTRÖM D, PUCHNER H, et al. Neutron⁃induced effects on a self⁃refresh DRAM [J]. Microelectronics reliability, 2022, 128: 114406.

[4] VALENTE L, TORTORELLA Y, SINIGAGLIA M, et al. HULK⁃V: a heterogeneous ultra⁃low⁃power linux capable RISC⁃V SoC [C]// Automation amp; Test in Europe Conference amp; Exhibition (DATE). Antwerp, Belgium: IEEE, 2023: 1⁃6.

[5] 吴修权,钟其柱,罗耀满.Cache在移动互联网的应用与分析[J].电信工程技术与标准化,2018,31(3):88⁃92.

[6] LEE J Y, SONG Y, EOM Y I. DCA: a dual⁃layer cache architecture for providing high lookup performance in KV stores [C]// International Conference on Big Data and Smart Computing. Jeju, Korea: IEEE, 2023: 285⁃286.

[7] MOSQUERA F, KAVI K, MEHTA G, et al. Guard cache: creating noisy side⁃channels [J]. IEEE computer architecture letters, 2023, 22(2): 97⁃100.

[8] 程志炜,陈财森,朱连军,等.基于Pearson相关系数的Cache计时模板攻击方法[J].计算机工程,2019,45(7):159⁃163.

[9] JING H Y, JUAN F, MIN C, et al. A prefetch⁃adaptive intelligent cache replacement policy based on machine learning [J]. Journal of computer science and technology, 2023, 38(2): 391⁃404.

[10] LI H, JI S, ZHONG H, et al. LPW: an efficient data⁃aware cache replacement strategy for apache spark [J]. Science China (information sciences), 2023, 66(1): 77⁃96.

[11] GAO J, GAO Y. Research the SDRAM controller based on FPGA [J]. Journal of physics: conference series, 2022(1): 10241.

[12] 钱素琴,刘晶华.基于FPGA的DDR2 SDRAM控制器设计[J].电子测试,2021(11):9⁃12.

[13] 韩笑,闫永立,李勇彬,等.基于FPGA的DDR2_SDRAM控制器用户接口设计[J].电子设计工程,2021,29(1):168⁃171.