基于RFSoC 的可重配置SAR 收发模块设计与实现

赵麒瑞,刘霖,张昆明,曹越,常桂林

(1.中国科学院空天信息创新研究院,北京 100094;2.中国科学院大学电子电气与通信工程学院,北京 100049)

数字收发模块通常由多个功能单元构成,实现发射信号产生、回波信号采集以及信号预处理等功能[1],在合成孔径雷达(Synthetic Aperture Radar,SAR)系统中具有重要作用。近年来,随着多模式SAR 系统的快速发展,传统收发模块设计方案面临复杂度高、体积功耗大、兼容性和通用性较差等问题。针对以上问题,该文提出一种基于RFSoC 的可重配置数字收发模块设计方案。RFSoC 在片上系统内集成了射频转换器,消除了对外部数据转换器的需求[2-3]。将RFSoC 架构与动态部分重配置策略相结合,利用重配置策略动态调整信号通道数量,而片上处理器则用于调整转换器速率与工作模式。测试结果表明,该文所设计的收发模块可根据需求实时调整信号通道数和转换器速率,完成基带与中频信号的生成、采集和处理,满足预期设计需求。

1 部分动态重配置技术

1.1 部分动态重配置原理

作为一种重配置技术,部分动态重配置对系统任务既进行了时间的划分,也进行了空间的划分[4]。利用部分动态重配置技术,能够在系统运行期间实现逻辑功能的重配置,而其他逻辑的运行在配置过程中不受影响,具有相当的灵活性和可靠性[5-7]。

部分动态重配置方法的实现需要将逻辑设计分成静态和动态两部分,其中,静态部分为固定逻辑,动态部分为可重构逻辑。需要注意的是,对FPGA器件而言,并不是所有资源都是可重构的,例如片上缓存、时钟以及收发器等逻辑资源不能被包含在动态逻辑设计中[9]。

对于重配置文件的加载,既可以从板载非易失性存储介质中进行加载,也可以由外部设备控制配置过程,还可以由微处理器通过内部配置访问端口(Internal Configuration Access Port,ICAP)或处理器配置访问端口(Processor Configuration Access Port,PCAP)将配置文件写入FPGA 内部的可重配置分区[8-16]以实现配置文件的加载。

1.2 基于FPGA管理器框架的部分动态重配置方法

与已有的部分动态重配置设计方案相比,该文所使用的部分动态重配置设计方案基于FPGA 管理器(FPGA Manager)框架,使用片上处理器通过PCAP进行重配置文件的加载[10-12],无需对配置文件进行固化,使得对配置文件的管理变得更加方便。

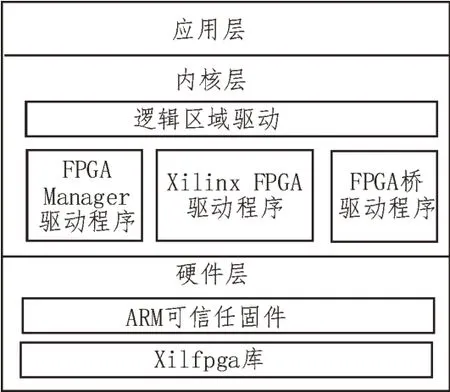

FPGA Manager 是Linux 内核的一部分,用于加载镜像文件以对可编程逻辑进行编程,其架构如图1 所示。在该框架下,所有应用程序编程接口(Application Program Interface,API)与FPGA 制造商无关。对于RFSoC 而言,其制造商信息被包含在底层Xilinx FPGA 驱动程序中。该驱动程序向Linux 内核中添加加载配置文件所需的相关指令。利用FPGA Manager 架构,可以很容易地实现包括配置文件加载、回读以及设备树覆盖在内的诸多功能,便于系统后续的升级与维护。

图1 FPGA Manager架构

2 可重配置数字收发模块实现

该文提出的数字收发模块设计方案所使用的RFSoC 芯片型号为ZU28DR。ZU28DR 是赛灵思推出的第一代RFSoC 芯片,集成了射频数据转换器、高性能可编程逻辑及多核ARM 处理器,支持最高8 路12 位射频模数转换器(Radio Frequency Analog-to-Digital Converter,RF-ADC)输入与14位射频数模转换器(Radio Frequency Digital-to-Analog Converter,RFDAC)输出,每路RF-ADC最高采样频率为4.096 GHz,每路RF-DAC 最高转换频率为6.554 GHz。

2.1 数字收发模块架构及重配置流程

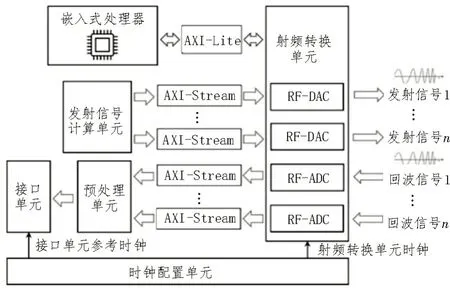

该文所设计的数字收发模块基本框架如图2 所示,包括发射信号计算单元、射频转换单元、预处理单元、接口单元以及时钟配置单元。发射信号计算单元根据当前工作模式下对应的系统参数计算发射信号,并传递给RF-DAC 转换为对应的模拟信号。RF-ADC 对回波信号进行采集并传递给预处理单元,处理后的回波信号通过接口单元发送给其他功能模块。嵌入式处理器负责配置射频转换单元以及控制重配置文件的加载,时钟配置单元为接口单元以及射频转换单元提供参考时钟和工作时钟。时钟配置单元与接口单元以外的各个单元通过AXI 总线进行通信与数据交互。

图2 可重配置数字收发模块基本框架

当切换模块工作模式时,首先,调整时钟配置单元,使其与射频转换单元当前工作模式下的转换速率相匹配;然后,通过嵌入式处理器对射频转换单元进行配置,调整当前的转换速率、混频器模式、抽取倍率等相关配置;最后,使用嵌入式处理器通过PCAP 加载当前工作模式下对应的重配置文件,完成工作模式的切换。

2.2 发射信号计算单元的设计与配置

发射信号计算单元根据当前工作模式下的相关参数计算发射的数字调频信号。

在该文所设计的收发模块中,发射信号计算单元既能够计算包含载波的中频信号,也能够计算不含载波信号的基带信号。之所以这样设计,是因为对于带宽较大的数字发射信号,受限于RF-DAC 转换速率,无法准确地将数字信号转换为对应的模拟信号。针对这一情况,该方案先计算基带发射信号,再通过模拟方式进行调频。

由于不同工作模式下信号通道的数量并不相同,因此在模块设计中将发射信号计算单元设置为部分重配置模块,并生成不同工作模式下发射信号计算单元所对应的部分配置文件[14-15]。

基带模式下,发射信号可表示为如下形式:

其中,A为信号量化幅度,K=BW/TS为信号的调频率,BW为调频信号带宽,TS为调频信号脉冲宽度。在基带发射信号计算单元中,t可以根据如下公式进行计算:

其中,tin为基于RF-DAC 时钟所产生的累加数,FS为RF-DAC 当前的转换速率。

中频模式下,发射信号可写为如下形式:

其中,F0为发射信号的中心频率。比较式(1)与式(3)可知,中频模式下发射信号的计算过程与基带模式任意一路信号基本一致。

在该文所提出的收发模块设计方案中,发射信号计算单元采用高层次综合(High Level Synthesis,HLS)策略进行设计,利用不同工作模式下所给定的信号带宽、脉冲宽度、中心频率以及采样频率,根据式(1)和式(3)完成对应模式下发射信号的计算。

该设计方案下静态逻辑和动态逻辑相应的资源使用情况如表1 所示。由表1 可知,重配置功能模块仅占用少量逻辑资源,一方面降低了对其他功能模块资源使用的影响,另一方面也提高了重配置模块的加载速度。

当需要切换发射信号计算单元工作模式时,通过前文所述的FPGA Manager 框架进行重配置文件加载。当应用程序发出加载配置文件指令后,由FPGA Manager 驱动程序分配所需内存,并根据对应API 地址发送电源控制请求。在ARM 可信任固件响应请求后,执行处理器中断,将配置文件写入重配置分区,并将应答由驱动程序传递给应用程序。

2.3 射频转换单元的动态配置

对于射频转换单元,通过嵌入式处理器使用驱动程序内置的API 函数对其有关配置参数进行查询、修改以及多通道同步。

以混频器设置为例,当调整混频器模式时,首先调用函数XRFdc_GetMixerSettings 以获取当前待调整转换器所对应的混频器设置信息,包括混频模式、混频器频率以及抽取/内插倍数等设置信息;然后调用函数XRFdc_SetMixerSettings,对当前混频器设置信息进行修改;最后比较修改前后混频器设置,若二者不同,则表示修改成功并打印相应提示信息,否则输出错误信息。具体流程如图3 所示,其余相关参数配置流程相关参数的配置流程与之基本一致。

图3 调整射频转换单元混频器设置流程

在调整信号通道数时,需要对使用的RF-ADC和RF-DAC 进行多通道同步,以使每个数据通道间的相对时延一致。在进行通道同步时,调用同步函数XRFdc_MultiConverter_Sync 使指定的Tile 同步。在此过程中,Tile 中的模拟采样时钟通过延迟抽头链捕获系统参考时钟,使用系统参考时钟将Tile 中的数字部分同步复位。

2.4 时钟配置单元设计与配置

时钟配置单元由LMX2592 频率合成器及Si5341A 可编程时钟芯片组成。其中,频率合成器通过QSPI 控制器进行配置,为射频转换单元提供所需的时钟信号;可编程时钟芯片通过I2C 控制器进行配置,为接口单元提供参考时钟信号。

当射频转换单元转换速率变化时,时钟配置单元依据当前射频转换单元的转换速率,使用Microblaze 嵌入式模块通过QSPI 和I2C 处理器修改时钟芯片的配置信息,调整输出时钟信号的频率,使其与当前射频转换单元的转换速率相匹配。

3 可重配置数字收发模块测试

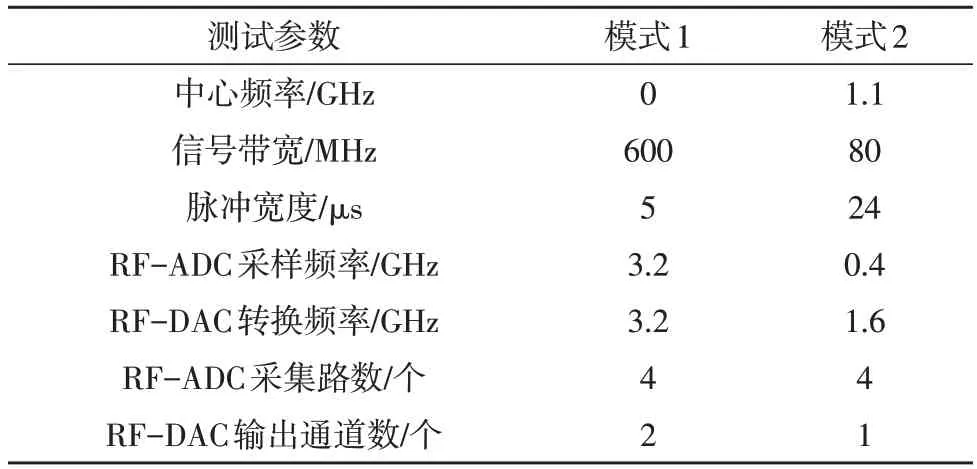

在对模块进行功能测试时,将RF-DAC 输出信号发送至射频综合单元,通过RF-ADC 采集回波信号。利用示波器与频谱仪观察RF-DAC 输出信号的波形与频谱,并与RF-ADC 所采集信号的波形与频谱进行比较。不同测试模式下模块工作参数如表2所示。

表2 收发模块测试模式参数

3.1 模式1测试结果

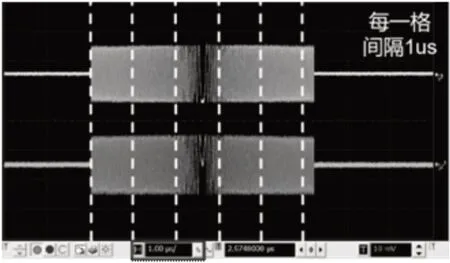

接通模块电源后,首先启动时钟配置单元。当时钟配置完成后,加载模式1 所对应的部分配置文件并启动片上操作系统。此时,收发模块工作在模式1 下,RF-DAC 两个输出通道内的信号如图4 所示,对应的频谱如图5 所示。

图4 模式1发射信号波形

图5 模式1发射信号频谱

可以看出,输出信号的脉冲宽度为5 μs,带宽为600 MHz,信号频谱位于第一奈奎斯特区内,带内平坦度小于±1 dB。

对通道2 输出信号对应的回波信号进行采集,采集后的信号归一化波形如图6 所示,其频谱如图7所示。可以看出,采集后的信号仍然为线性调频信号,脉冲宽度为5 μs,带宽为600 MHz,与模式1 下被采集的输出信号一致。以上测试结果表明,模式1下发射信号相关参数与给定测试参数一致,回波信号采集正确无误。

图6 模式1采集信号波形

图7 模式1采集信号频谱

对所采集的回波信号进行脉冲压缩,压缩后信号的峰值旁瓣比(Peak Side Lobe Ratio,PSLR)为-12.953 7 dB,积分旁瓣比(Integrated Side Lobe Ratio,ISLR)为-10.451 7 dB。

3.2 模式2测试结果

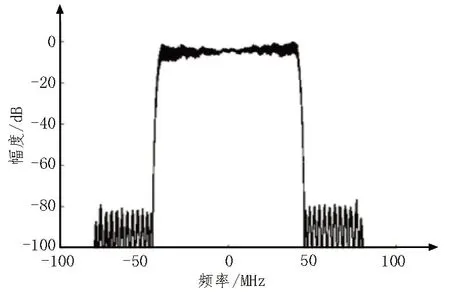

按前文所述顺序,依次调整时钟配置单元和射频转换单元配置信息,并加载模式2 对应的重配置文件。完成上述操作后,收发模块在模式2 下工作,此时RF-DAC 的输出信号频谱如图8 所示。可以看出,输出信号中心频率为1.1 GHz,带宽为80 MHz,信号频谱位于第二奈奎斯特区内,带内平坦度小于±1 dB。

图8 模式2发射信号频谱

对输出信号进行采集,采集后的中频信号经下变频处理后归一化波形如图9 所示,其频谱如图10所示。可以看出,采集后的信号仍然为线性调频信号,脉冲宽度为24 μs,带宽为80 MHz,与模式2 下被采集的输出信号一致。以上测试结果表明,模式2下发射信号相关参数与给定测试参数一致,回波信号采集正确无误。

图9 模式2采集信号波形

图10 模式2采集信号频谱

对所采集的回波信号进行脉冲压缩,压缩后信号的PSLR 为-12.766 3 dB,ISLR 为-10.382 1 dB。

综上,发射信号计算单元与射频转换单元在不同工作模式下的测试均得到了预期的结果。上述测试结果表明,所设计的收发模块能够根据不同模式所设置的工作参数实时调整信号通道数和转换器速率,完成基带与中频信号的生成和采集。

4 结束语

该文提出一种以RFSoC 为平台的可重配置数字收发模块设计方案,并对其功能进行了验证。结果表明,与传统设计方案相比[17-18],该文所提出的设计方案能够根据需求实时调整信号通道数和转换器速率,支持基带与中频信号的生成、采集和处理,不仅具有较强的灵活性和通用性,还降低系统的体积与功耗。后续的改进方向包括两方面:1)进一步优化重配置模块设计,提升配置文件加载速度;2)在模块中添加包括抗干扰处理在内的其他功能单元。