边界扫描测试技术及可测试性设计研究

张永涛,皇甫强龙,岳佳欣

(航空工业西安航空计算技术研究所 陕西 西安 710068)

0 引言

集成电路的发展,特别是大规模集成电路和超大规模集成电路的出现,带来了日益强大的功能实现能力,但也使得其内部结构变得更加复杂。随着集成度的提高和组装密度的增加,电路测试面临着引脚数量减少和测试难度增大的挑战。测试成本已经变得异常高昂,甚至超过了芯片本身的制造成本。因此,需要采取有效的策略来降低测试成本并确保电路的可靠性和性能。过去,学术界探索了一些策略,如增加测试点、设计独立的测试电路来检测复杂线路等。尽管这些方法在一定程度上改善了传统测试方法,但对于提高电路可测性的作用仍然有限。此外,这些方法的通用性也较差,难以适应不同应用场景的需求。鉴于此,在1987 年,联合测试行动组(Joint Test Action Group,JTAG)提出了一种全新的用于电路板测试的方法,即边界扫描测试技术。1990 年边界扫描测试技术被电气与电子工程师协会(Institute of Electrical and Electronic Engineers,IEEE)接纳为IEEE 1149.1 标准[1]。

1 边界扫描测试技术的发展史

在1990 年初,IEEE 发布了边界扫描测试标准1149.1[1]。随后IEEE 对其进行不断的完善和规范,又发展出了如IEEE 1532、IEEE 1581、IEEE 1687 等一系列的行业标准,以上标准都可以视为对边界扫描测试技术的延伸扩展。

IEEE 1149.1 的发布作为边界扫描测试行业的第一个标准,为行业的发展作出了巨大贡献。尽管IEEE 1149.1 标准只能应用于纯数字电路,但是它证明了良好的测试方法可以有效节约后期排故所需的时间和精力,同时也为后续一系列标准的发展打下了基础。IEEE 在1999年提出了全新的IEEE 1149.4 边界扫描技术标准协议[1],解决了IEEE 1149.1 标准无法完成模拟电路与混合信号电路的参数测试、互联测试和内部测试的问题。

IEEE 1149.4 标准是完全向前兼容的。它使用IEEE 1149.1 标准规定对混合信号电路中的数字部分进行边界扫描测试;IEEE 1149.4 标准进一步规定了特殊的边界扫描结构,用于解决混合信号电路中模拟电路的边界扫描测试。IEEE 1149.4 标准的出现使得模拟电路的可测试性得到了实现,尽管它还不能完全检测出模拟和数字混合信号中的问题,但已经填补了模拟电路测试的空白。

IEEE 1149.1 标准只适用于板级测试要求,无法满足系统级测试的需求。因此,在1995 年IEEE 发布了针对模块测试和总线维护协议的IEEE 1149.5 标准[1],扩展边界扫描测试从板级到系统级的支持。通过对模块的测试和维护总线的协议进行控制,可以花费较少的测试费用完成对元件级、板级和系统级的测试和维护。

IEEE 1149.6 标准于2003 年发布[1],为高级数字网络的故障检测和诊断提供了一套完整和标准化的可测试性设计方法。为了充分利用IEEE 1149.1 数字边界扫描测试标准被广泛接受和应用的优势,IEEE 1149.6 标准与IEEE 1149.1 完全兼容。对于数字电路中直流耦合部分的边界扫描测试标准继续使用IEEE 1149.1 内容;而对于交流耦合部分,IEEE 1149.6 标准规定了专用的测试指令和测试结构,以满足相应的边界扫描测试需求。IEEE 1149.6 标准在实际应用中显著提高了故障覆盖率,增强了设备的可测量性和稳定性[2]。

2010 年,IEEE 发布了1149.7 标准[1],这是一种全新的测试方法,它以IEEE 1149.1 为基础,并在系统结构、引脚效率和功能等方面进行了扩展。该标准显著改进了调试功能,并且降低了对系统级芯片(system on chip,SoC)引脚数量的要求。此外,该标准还实现了功耗控制的标准化,简化了多芯片模块和叠层裸片器件的结构,使得复杂的数模混合电路的测试和调试对研发人员要求显著减低。

最新的边界扫描测试标准IEEE 1149.10 于2017 年由IEEE 发布[1]。该标准解决了IEEE 1149.1 TAP 在量产SoC 测试中速度慢和引脚受限的问题。IEEE 1149.10 首先引入了复用任务模式引脚的概念,通过使用HSTAP 和PEDDA 来实现高带宽测试,例如3D 芯片间的测试数据传输,或者适用于引脚资源有限的测试场景,如低功率电流互感器(low power current transformer,LPCT)。其次,1149.10 标准还提供了更短的测试和配置时间,并放宽了对测试设备引脚的要求。最后,它还有可能降低扫描时钟速率和压缩系数。IEEE 1149.10 标准代表了芯片测试技术的未来发展方向。它不仅解决了现有标准在量产SoC测试中的限制,还提供了更高效和灵活的测试方法,使得在引脚资源有限的情况下仍能实现高带宽测试和数据传输。通过使用1149.10 标准,芯片测试过程中的测试和配置时间大大缩短,并且对测试设备引脚的要求也更为宽松。这一标准的引入将极大地推动芯片测试技术的进步,为未来的芯片设计和生产提供更可靠和高效的测试方法。

2 边界扫描测试原理与测试流程

2.1 边界扫描测试原理

边界扫描测试技术的基本思想是在芯片的每个输入/输出引脚位置,也就是与芯片内部逻辑相邻的位置,放置由移位寄存器组成的边界扫描单元。当电路板处于测试模式时,用户可以通过特定指令对这些移位寄存器组成的扫描单元进行控制,进而控制输出引脚的状态。通过对输入引脚状态的读取,能够完成电路板的全面互连测试。边界扫描测试的基本原理如图1 所示。

图1 芯片互联边界扫描测试原理

在图1 中,展示了一个四线测试总线结构——数据输入线(test data in,TDI)、数据输出线(test data out,TDO)、时钟(test clock,TCK) 和模式选择(test model select,TMS)。在边界扫描测试软件中对图中输出端芯片的引脚输出的测试向量进行数据处理和数据分析,得出芯片互联状态故障的判据。例如对图1 中芯片A 与芯片B 之间的互联状态进行测试,首先将测试向量从JTAG 的输入端输入进芯片A 的边界扫描单元(boundary-scan cell,BSC),使其在芯片A 的所有BSC 单元中以串行移位的方式进行传输。当测试向量完成传输后,芯片A 所有的管脚均被设置成预期态。其次读取芯片B 与芯片A 对应相连的BSC单元状态,确认芯片A 与芯片B 的互联状态是否符合预期。类似地,还可以将测试向量从芯片B 的TDI 测试访问端口输入,对其管脚状态进行设定,达到控制芯片C 管脚的目的。

2.2 边界扫描测试流程

边界扫描测试主要分为以下7 步:

(1)建立测试工程;

(2)读入边界扫描描述语言(boundary-scan description language,BSDL)文件、网表文件、电路板原理图等;

(3)编译输入文件,编译通过后通过测试软件生成测试矢量;

(4)初始化边界扫描控制器;

(5)扫描链完整性测试,测试电路板是否正确;

(6)加载测试矢量,执行测试任务;

(7)采集测试响应,分析测试结果。

详细测试流程如图2 所示。

图2 边界扫描测试流程

3 边界扫描测试与传统测试的区别

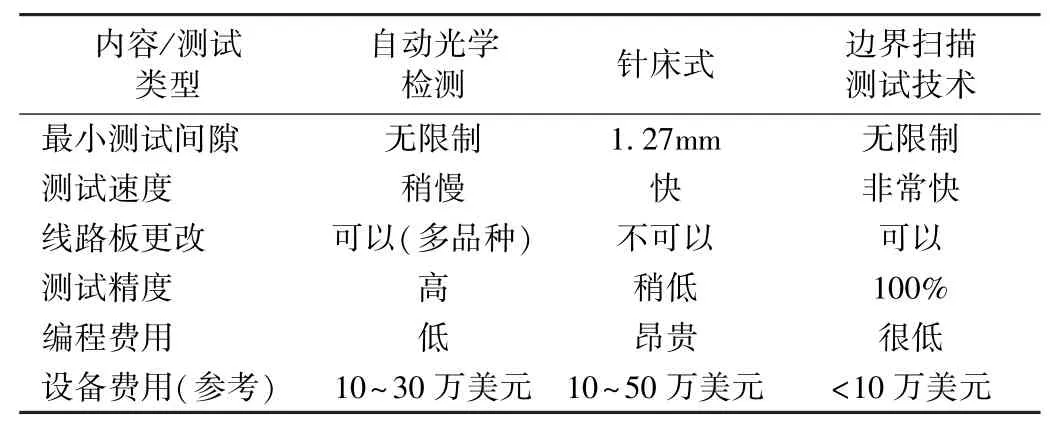

凭借其独特的优势,如对测试资源的要求较少和对器件及电路性能影响较小,边界扫描测试技术有效解决了现代电子技术的测试问题,已迅速发展并广泛应用于电子设计和制造领域。该技术的应用显著提升了器件的可观测性和可控性,通过提高故障覆盖率,边界扫描测试技术能够减少故障诊断时间并具有良好的性价比。表1 是边界扫描测试技术与传统测试的区别,如表1 所示。

表1 边界扫描测试与传统测试的区别

4 边界扫描测试技术的应用

边界扫描测试技术不仅应用于单个芯片测试,而且在板级测试领域同样广泛应用。对于多模块构成的产品,边界扫描测试主要可以归纳为以下几个方面:

(1)边界扫描链路完整性测试

采用读取边界扫描器件指令寄存器中默认值的方法来判断扫描链路的完整性[3]。

(2)器件间互联测试

通过发送“外部测试”(extest)指令,添加激励和检测响应,可以检测出待测模块边界扫描芯片的硬件连接情况,包括节点之间的正常连接测试、多节点之间的短路故障、两节点之前的断路故障、两节点之间与电源或地的短路故障

(3)簇功能测试

通过发送测试向量对待测模块进行控制,可以测试待测模块逻辑功能、回路测试、特定时序。

(4)非边界扫描器件的测试

通过发送测试向量对待测模块的双倍速率同步动态随机存储器(double data rate synchronous dynamic random access memory,DDR SDRAM)存储芯片、FLASH 芯片进行控制,可以访问模块内部存储空间、从指定起始地址读取指定长度的内容、向指定起始地址写入指定内容、读取Flash 芯片的指定存储空间、擦除Flash 芯片的存储空间、向Flash 芯片的指定存储空间烧录指定的文件等手段测试DDR 和FLASH 是否存在故障。

(5)兼容调试功能

部分边界扫描工具(如Asset、GOEPL、CORELIS)能够对待测模块完成对

可擦编程只读存储器(erasable programmable read-only memory,EPROM)、Flash 芯片程序的烧结,复杂可编程逻辑器件(complex programmable logic device,CPLD)等芯片程序的下载,并能借助上位机测试原有调试电路的工作情况。

总体而言,边界扫描测试技术在电子系统的机内自测试和故障自诊断系统设计中,对于提高故障检测率、隔离率和降低虚警率具有显著的优势。它为系统测试和调试提供了强大的工具和方法,有助于提高产品品质、节约时间和成本,提升用户体验。

5 测试性设计建议

为了提高测试效率并降低测试成本,测试性设计技术已广泛应用于装备电子系统的设计中。在高可靠性系统中,几乎所有系统都进行了可测试性设计[4]。边界扫描技术作为一种扩展的内建自测试(built-in self-test,BIST)技术,无需额外的辅助电路,在芯片可测试性设计中已成为主流。

为了顺利地实现边界扫描的可测试性,在产品研发阶段,测试性设计建议可参考执行:

(1)尽可能多选用1149.x 兼容的器件,可以提高测试覆盖率。JTAG 接口不只可以用于程序加载,其支持的IEEE 1149.x 系列标准,还可用于以边界扫描的方法进行芯片测试。尽可能多选用1149.x 兼容的器件,可以提高测试覆盖率,电路中的边界扫描器件数量越多,可以实现充分测试的可用节点越多。

(2)不同厂家的边界扫描器件应分链放置。由于IEEE 1149.1 标准中未对边界扫描命令寄存器的长度作限定,不同厂家的边界扫描命令寄存器长度往往不一致,如果将它们放置在同一条链路中,会带来兼容问题,导致扫描链路不能正常工作。

(3)边界扫描器件TCK 频率与其他器件相差较大时,器件应单独成链。边界扫描接口采用串行信号传输,通常的时钟频率介于10 MHz~50 MHz 之间。电路板上的TCK频率由边界扫描链上最慢的器件决定。因此,在设计扫描链时需要注意每个边界扫描器件的TCK 频率,并将与其他器件的TCK 频率差异较大的器件单独成链,以免影响扫描链上可编程器件的编程速度。

(4)JTAG 链路上串联器件数大于或者等于5 个时,应对链路的JTAG 接口信号进行缓冲驱动。由于单个JTAG器件的信号驱动能力有限,通常只能够驱动大约3 个设备。当扫描链长度较长(大于等于10 cm)时,为了增强JTAG 信号的稳定性,需要使用驱动器来增加JTAG 信号的驱动能力。此外,对于长距离的扫描链路,使用驱动器可以降低噪声干扰,减少时钟偏差,并满足阻抗匹配的要求。

(5) 对于无法支持边界扫描的存储器件,例如FLASH、EPROM 等,应该确保所有与该类器件相关的必要引脚都可以通过边界扫描器件进行访问。

为了避免测试过程中因信号竞争导致器件损坏或测试不可靠,对于不支持边界扫描逻辑控制信号访问的器件,必须将其控制信号连接到边界扫描单元,以实现对该器件的非使能控制。这样可以确保测试期间对非边界扫描器件的控制信号进行有效的管理和控制。

6 结语

边界扫描测试技术已被广泛认可,作为一种可测试结构技术,它不但能够支持传统集成电路芯片的管脚状态测试,还可以检测内部引线的开路短路等故障,被视为当前和未来测试流程中不可或缺的一部分。边界扫描测试技术对数字电路的可观察性和可控制性的显著提升,有效解决了传统测试方法无法涵盖的测试问题,达到对芯片内部的工作状态进行全面检测的目的。同时,边界扫描测试技术的应用也对被测试电路板的可测试性设计提出了更高要求。未来的研究可针对可测试性设计展开更多探讨。