低功耗高速率IR-UWB 发射机设计与实现

姜 帆,陈 潇,张 磊,盛旭阳,林 敏

(上海大学通信与信息工程学院特种光纤与光接入网重点实验室,上海 200444)

IR-UWB 是一种具备高空间分辨率、高速率数据通信和低功耗特性的无线通信技术,特别适合用于高精度室内定位[1-6]、增强现实/虚拟现实和脑机接口[7-9]等新兴的无线通信与传感应用。一个低功耗、高数据传输速率的发射机对于IR-UWB 技术在无线通信与传感方面的应用具有重要的意义。

传统的IR-UWB 发射机可以像连续波通信发射机一样,在基带中产生脉冲,通过混频器转换为射频信号,并通过线性功率放大器发射。文献[10]采用的发射机最大数据传输速率可以达到1.8 Gpulses/s,但消耗的功率高达129 mW。由于这种发射机设计复杂而且没有充分利用脉冲发射机的特点,其并不适合低功率的应用。文献[11]提出了脉冲振荡器方法,其中发射脉冲是由基带脉冲控制振荡器产生。虽然功耗低至0.26 mW,但其最大数据传输速率只有2 Mb/s。这主要是因为振荡器的响应时间限制了发射器的输出带宽,因此难以实现高数据速率通信。

针对上述结果的不足,该文提出了一种低功耗高速率的发射机架构。该设计中使用注入锁定环形振荡器(Injection Locked Ring Oscillator,ILRO)为发射机提供射频载波,在节省面积的同时,具有较低的功耗。同时,调制信号经过基于FIR 滤波器的模拟延迟线,生成输出功率谱密度(Power Spectral Density,PSD)满足FCC MASK 的基带波形要求,从而得到一个低功耗高速率的IR-UWB 发射机。

1 电路整体架构

该文提出的发射机架构如图1 所示,其包括调制模块、脉冲整形模块、ILRO 和数字功率放大器(Digital Power Amplifier,DPA)。其中,调制模块包括逻辑电路和译码模块,产生基带脉冲和数据调制信息,可以实现二进制开关键控(On-Off Keying,OOK)、二进制相移键控(Binary Phase Shift Keying,BPSK)。调制模块所产生的基带脉冲被送入脉冲整形模块,用于生成发射脉冲。在发射机正常工作之前,脉冲整形模块中的延迟单元需要通过延迟锁定环(Delay Loop Lock,DLL)进行片上校准,以满足输出脉冲宽度的要求。调制完成后,脉冲整形模块向DPA 提供多相信号,以控制输出脉冲宽度。锁相环为ILRO 提供注入时钟,其输出信号将被锁定在注入时钟的八次谐波上,从而为DPA 提供射频载波。为了实现这一点,ILRO 需要在注入时钟之前通过频率估计模块进行校准,使数控环形振荡器(Digital Control Ring Oscillator,DCRO)的振荡频率接近发射机所需的射频载波频率。

图1 发射机整体架构

2 模块设计

2.1 调制模块设计

由图1 可知,调制模块由逻辑电路和译码模块构成,其中DATA 为发送数据,PRF 为脉冲重复频率,Mod 用于控制调制模式。如图2 所示,逻辑电路主要用于生成基带脉冲DPulse,并且根据时钟clk_ruler 的频率改变DPulse 的脉冲宽度。当clk_ruler 为499.2 MHz 时,DPulse 输出脉宽约为1 ns;当其为998.4 MHz 时,输出脉宽约为0.5 ns。

图2 调制模块逻辑电路时序图

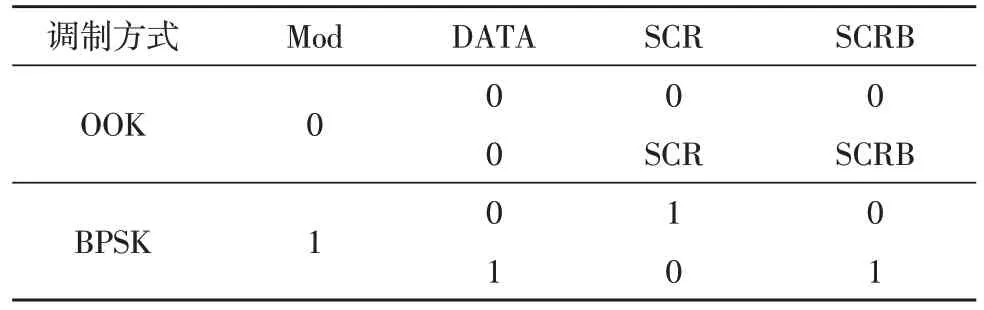

OOK 和BPSK 的调制结果可由表1 得到。译码模块可以在OOK 模式下输出伪随机二进制序列(Pseudo-Random Binary Sequence,PRBS),也就是SCR和SCRB,其频率与PRF相同,用于选择载波相位。因此在OOK 模式下,SCR 和SCRB 可以使载波相位随机变化,这样平滑了输出频谱中的离散频谱能量,并在满足FCC规定的情况下使输出PSD最大化[7,12]。

表1 调制结果

2.2 脉冲整形模块设计

IR-UWB发射机的输出PSD必须符合FCC MASK的要求,所以需要特殊考虑发射脉冲波形。文献[13]中分析了一些特殊形状的脉冲频谱,如三角型、指数型和分段型。基于这一分析,该设计采用了三角型脉冲,并通过脉冲整形模块产生。如图3 所示,脉冲整形模块采用基于FIR 滤波器的模拟延迟线,结构简单而且功耗低。该电路由多级延迟单元构成的延迟线和DPA 组成,滤波器输出的多相控制信号在DPA 处相加,得到射频发射信号的包络。模拟延迟单元采用基于反相器的架构,通过温度计码B<62:0>控制NMOS 电容阵列NM0-NM125 接入的个数,从而控制延迟时间。电容阵列共63 组,上下两个电容构成一组,使得信号路径上的充放电时间匹配。该设计将16 个延迟单元(τ=62.6 ps)级联相接,其中8 个延迟单元的输出信号分别连接到DPA 单元上,并且通过PW 选择脉冲宽度,当PW=′1′时,DPulse 脉宽为1 ns,如图3 所示,选择CLK1,3,…,15 为输出多相信号,延迟间隔为2τ,得到输出脉宽约为2 ns。当PW=′0′时,DPulse 脉宽为0.5 ns,选择CLK1,2,…,8 输出多相信号,延迟间隔为τ,输出脉宽约为1 ns。所设计的延迟单元覆盖了一定的延迟范围,同时通过片上DLL 环路校准,提高延时电路的鲁棒性,生成具有精准脉冲宽度的发射脉冲。

2.3 注入锁定环形振荡器设计

注入锁定环形振荡器在降低电路功耗、面积和优化相位噪声方面具有优势,因此被广泛用于产生射频本地时钟[14-15]。该设计采用的ILRO 架构如图4所示,由注入脉冲产生模块和DCRO 构成。

图4 ILRO电路原理图

DCRO 由两个电流匮乏的伪差分反相器构成,频率fDCRO=1/(8×td),其中td为伪差分反相器的延时,可通过10 bit 数字控制的电流舵数模转换器(Current Steer Digital-to-Analog Converter,CS-DAC)调节延时。整个DCRO 的调谐范围为3.5~10 GHz,其中构成DCRO 的电流匮乏的伪差分反相器如图4 所示。由于信号路径上由PM0-1 和NM0-1 构成的反相器存在死锁的可能,因此PM2-3 和NM2-3 构成的交叉耦合对用来防止振荡环路进入死锁状态。交叉耦合对的尺寸应足够大,从而阻止DCRO 进入死锁状态,无法振荡。同时尺寸也不应该过大,过大会导致功率的消耗和噪声的增加,因此需要考虑这两种情况,选取合适的尺寸。

脉冲产生模块根据注入时钟Inj_clk(499.2 MHz或998.4 MHz)的频率,产生相同频率且脉宽为40~100 ps 的窄脉冲Inj,送入DCRO。如果Inj 的脉宽过宽或过窄都可能导致电路无法锁定,因此要将脉宽控制在一定范围内。对于注入晶体管M0 的尺寸也需要仔细设计,其与Inj 的脉宽具有相同的效果,决定了注入强度。M1 为负载匹配,与M0 尺寸相同。ILRO 根据Inj 频率的不同,将频率锁定在Inj 频率的8 次谐波处,也就是该设计的两个中心载频:3 993.6 MHz 和7 987.2 MHz。由图4 中的时序图可以看到,DCRO 的输出相位周期性地与干净的参考时钟沿重新对准,以抑制DCRO 电路的长期噪声,优化了DCRO 本身不理想的相位噪声。由于DCRO 的低品质因数,电路可以快速启动并稳定,同时注入锁定技术可以瞬时锁相,因此ILRO 可以在不发射脉冲时关闭,进一步降低电路功耗[16]。

从式(1)来看[17],ILRO 产生的参考杂散如果低于-40 dBc,则对于499.2 MHz 和998.4 MHz 的参考频率,需要自由振荡频率与目标锁定频率的差分别在5 MHz 和10 MHz 以内。因此,采用了片上频率估计模块电路来校准DCRO 频率,其在预设定的时间内对DCRO 输出频率进行计数,同时采用SAR 逻辑,可在80 μs 内完成频率的校准。频率估计模块电路校准流程图如图5 所示。

图5 频率估计模块校准流程图

3 电路仿真

3.1 脉冲整形模块仿真结果与分析

脉冲整形模块主要由模拟延迟单元级联构成。由于延迟时间随着工艺角变化很大,因此需要采用片上DLL 环路进行校准,从而产生准确的延迟间隔。由图6 可以看出,在各种工艺角下,单位延迟均可以校准到62.6±0.4 ps 以内,很好地满足了该设计的需求。

图6 延迟单元的校准

3.2 ILRO仿真结果与分析

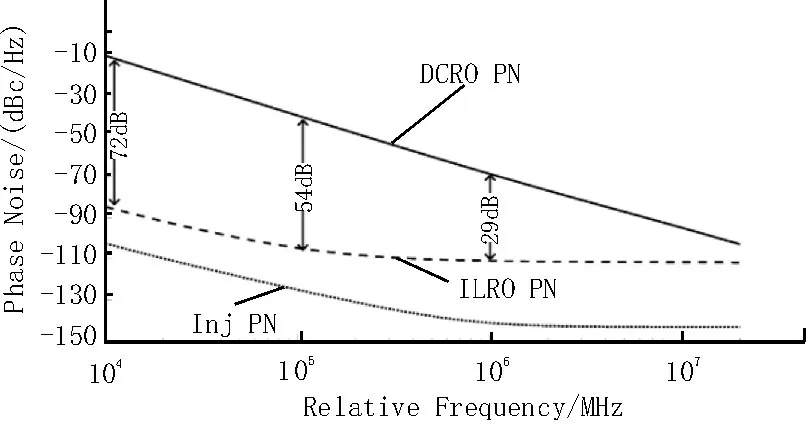

ILRO 中DCRO 的开环频率范围为3.5~10 GHz,可覆盖绝大部分UWB 频带,包括该设计的所需频点3 993.6 MHz 和7 987.2 MHz。图7 表示的是注入频率为998.4 MHz,ILRO 输出频率为7 987.2 MHz 时,DCRO、ILRO 和注入时钟Inj 的相位噪声曲线。可以看到,相较于DCRO,ILRO 在10、100 和1 MHz 频偏处分别优化了72、54 和29 dB 的相位噪声,很好地改善了DCRO 较差的噪声性能,可以为发射机提供稳定、纯净的射频载波。

图7 LO为7 987.2 MHz时的相位噪声

3.3 发射机整体仿真结果与分析

如图8(a)所示,当使用OOK 调制且PRF 为499.2 MHz 时,数据传输速率为499.2 Mb/s,输出脉冲的幅度信息与图2 显示的数据调制结果相符。发射机输出脉冲的PSD 如图8(b)所示,当脉冲宽度约为2 ns 和1 ns 时,其输出带宽约为1.1 GHz 和2.2 GHz,PSD 满足了FCC MASK 的要求。所设计的发射机采用1.1 V 供电,消耗功率约为5.9 mW,其中ILRO、脉冲整形模块、DPA 和调制模块分别消耗2.82、0.91、1.94 和0.23 mW 的功率。经过仿真验证,所设计的发射机在采用40 nm 工艺,1.1 V 供电的条件下,不仅实现了最高可达499.2 Mb/s 的高速数据传输速率,而且能量效率值低,仅为11.8 pJ/bit。

图8 发射机仿真结果

该文选取了一些高速率发射机进行对比,比较结果如表2 所示。所设计的发射机相较于文献[18],在相同的数据速率下具有更低的能量效率值。与文献[19]相比,虽然数据速率低,但是具有更好的能量效率,可更好地满足低功耗下的应用需求。

表2 发射机性能对比

4 结论

文中所设计的发射机采用注入锁定环形振荡器产生射频载波,同时基带信号通过基于FIR 滤波器的模拟延迟线产生发射所需要的波形。在满足了FCC MASK 的要求下,发射机功率消耗仅为5.9 mW。因此得到了一种低功耗、高速率的IR-UWB 发射机,其工作频率为3 993.6 MHz 和7 987.2 MHz,具有1.1 GHz 和2.2 GHz 两种发射带宽,同时支持OOK 和BPSK 调制方式。通过仿真验证,所提出的IR-UWB发射机的最大数据速率为499.2 Mb/s,能量效率仅为11.8 pJ/bit,可以较好地满足低功耗高速率无线通信的需求。