24 GHz 频段高性能压控振荡器的设计

张和平,陈磊

(上海电力大学电子与信息工程学院,上海 201306)

随着毫米波频段的不断开发与应用,雷达系统在电子消费和车规领域的应用不断扩大,压控振荡器(Voltage-Controlled Oscillator,VCO)作为本振信号,是其核心模块[1-2],VCO 性能直接影响通信传输速率、雷达探测距离及精度[3]。噪声与功耗是衡量VCO性能优劣的重要指标[4-5],较宽的调谐范围是雷达系统获得良好距离分辨率的重要前提[6]。

文中提出了一种应用于24 GHz 频段,适用于Doppler 和FMCW 雷达系统的低功耗、低噪声、宽调谐范围VCO。采用自行设计的高Q值电感构成谐振腔,提高了压控振荡器的噪声性能;可配置电容偏置电压和四位电容阵列用于实现更宽的调谐范围、更高的子带重叠和更低的调谐增益,可配置偏置电流用于调节功耗。仿真及测试结果表明,VCO 工作功耗为2.42 mW,输出相位噪声在1 MHz 频偏处为-103.05 dBc/Hz,实现6 GHz的宽调谐范围。

1 振荡器构成和工作原理

1.1 振荡器的工作原理

压控振荡器通常有电感电容振荡器和环形振荡器两种架构[7],在频段较高的情况下,LC VCO 的噪声性能优于Ring VCO[8-9],具有低功耗、低相位噪声的优点[10]。LC VCO 通过并联电感和电容构成谐振回路,其有源电路作为负电阻,补偿无源器件的损耗,也称其为负阻振荡器[11]。振荡器是正反馈系统,正反馈产生的负阻与LC 谐振腔构成的正阻相互抵消,实现了稳定的振荡频率[12]。

1.2 LC VCD的结构与原理

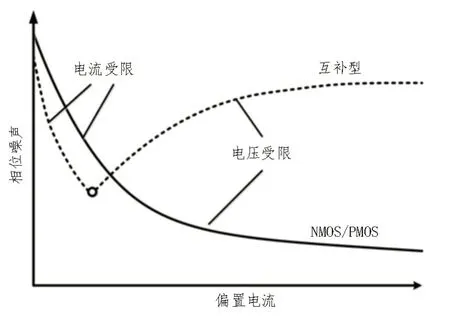

如图1 所示,LC VCD 有三种基本架构,分别为交叉互补型、NMOS 型、PMOS 型[13]。

图1 LC VCO三种架构

对于LC VCO,噪声和功耗是一对相互制约的指标。图2 所示为不同架构下电流与噪声的关系。

图2 相位噪声随电流变化的曲线

对于互补型结构,LC 谐振腔在一个振荡周期里面电流会两次且反方向流过,假设流过电流为Ib、谐振腔等效电阻为Rb,则振幅为4×Ib×Rp/pi;对于NMOS或PMOS 结构,由于电流只流过一次,因此其振幅为2×Ib×Rp/pi。互补型结构的振幅不能超过电源电压,且电流增大过程中,电路的非线性增加,会恶化相位噪声;而对PMOS 或NMOS 结构,其振幅受到Vsg的限制,但是Vsg正相关于Ids的平方根,因此,对于这两种结构来说,随着电流的增加,相位噪声会继续减小。具体应用时,应根据电源电压来选择相应的结构,对于互补型的结构,需要优化偏置电流,使其工作在电流与电压受限区的转折点。

1.3 LC无源器件的设计

压控振荡器电路中,电感和电容等无源器件的设计至关重要[14]。主要包含片内电感的设计、可变电容结构的设计、权位电容的设计。

电感的感值和Q值是影响频率和相噪的主要因子,且电感占据芯片面积较大。一般采用ADS 或者EMX 自设计电感,主要设计和优化金属线宽度、间距和电感的内径[15]。增大金属线的宽度,可以减小寄生电阻以提高Q值。但是在相同的电感值和圈数的情况下,金属线宽度越大电感的面积越大,并且高频时由于趋肤效应,电流只流过金属的表面,因此宽度取值要合理;金属线的间距要小,增加互感,同时要注意太小会导致金属线之间的边际电容增大,影响电感的谐振频率;电感的半径不能太小,否则涡流效应造成内圈的阻值上升,进而导致电感的Q值降低[16]。

可变电容有二极管型和MOS 可变电容两种,其电容值随其偏置电压的变化而变化,直接关系到调谐增益的设计,影响调谐范围和调谐线性度。

权位电容的设计即调谐范围的设计,主要为开关的设计及权位电容的单位容值设计。开关的结构设计要点是导通电阻和关断电阻,导通时要电阻尽量小,电阻越小,电容阵列的Q值越大,对相位噪声的影响越小。权位电容的单位电容取值大小是和可变电容统一考虑,要基于频率输出范围和调谐曲线的增益综合设计。

2 振荡器电路设计

如图3 所示,提出的差分LC VCO 采用无电流源NMOS 结构,有助于提高NMOS 的过驱动电压,降低杂散电容。

图3 设计的24-30 GHz压控振荡器

M1 和M2 为差分NMOS 负阻管,采用自偏置技术,连接交流耦合电容C3和C4,以降低电源噪声。Cvar1和Cvar2是由环路滤波器输出电压Vtune控制的可变电容。为了保证变容器的偏置电压在0 电压附近变化,将Cvar1和Cvar2分别连接到LC 槽中的电容C1和C2上。变容管的电容随偏置电压的变化而变化,有利于提高VCO 的调谐范围。

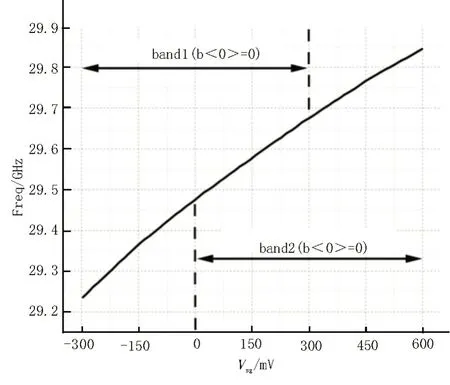

图4 显示了VCO 输出频率随变容管偏置电压Vsg的函数关系。

图4 可变电容调谐曲线

从图4 中可以看出,VCO 在Vsg=0 V 时增益值Kvco_max最大;当Vsg为-0.3~0.3 V时,Kvco近似等于Kvco_max;当Vsg为0.3~0.6 V 时,Kvco约等于0.75Kvco_max;当Vsg为-0.6~-0.3 V 时,Kvco约等于0.5Kvco_max。Kvco的取值将影响锁相环的环路增益和环路稳定性,因此,Vsg的最理想值范围为-0.3~0.3 V。但是电源电压为1.1 V,为了保证电荷泵中所有MOS 晶体管都在饱和状态下工作,Vtune的输出电压通常在0.3~0.9 V 之间变化,因此设置变容器控制电压Vdc为0.6 V,使得Vsg在-0.3~0.3 V 之间变化。

Vtune电压控制在0.3~0.9 V,当Vdc设置为0.3 V 和0.6 V 两个偏置独立电压时,Vsg的变化范围为-0.3~0.6 V。如图5 所示,Vdc由数字信号b<0>控制,相当于将原频段分成两部分。

图5 b<0>控制位作用下得到不同频率子带

为了实现更大的调谐范围,减小VCO 的增益值,采用了四位电容阵列。数字信号b<4:0>将整个VCO频段划分为16 个子带,提高了VCO 调谐范围和各子带的重叠程度。采用电阻阵列产生不同的偏置电压Vbias来调节VCO 的电流,Vbias的开关控制同一时间只有一个开关会被打开。

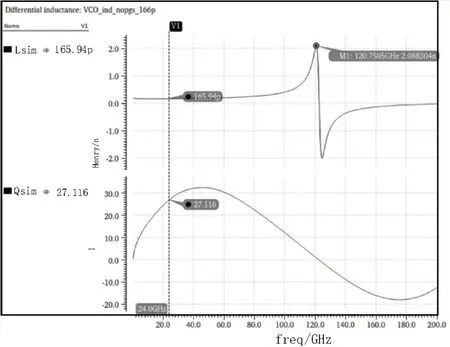

无源器件电感的设计采用自建模的电感设计,八字电感的设计有利于减小磁场之间的相互耦合影响,提高Q值,同时降低CMOS 工艺下衬底的泄露。

设计的电感长120 μm、宽75 μm,内径为40×53 μm,采用顶层金属UTM,线宽为11 μm。采用EMX 仿真,结果如图6 所示,电感值为165.94 pH,Q值为27.12,自谐振频率为120 GHz,远远低于所需的24 GHz 频段。

图6 自设计的电感L与Q

3 振荡器电路版图设计与仿真

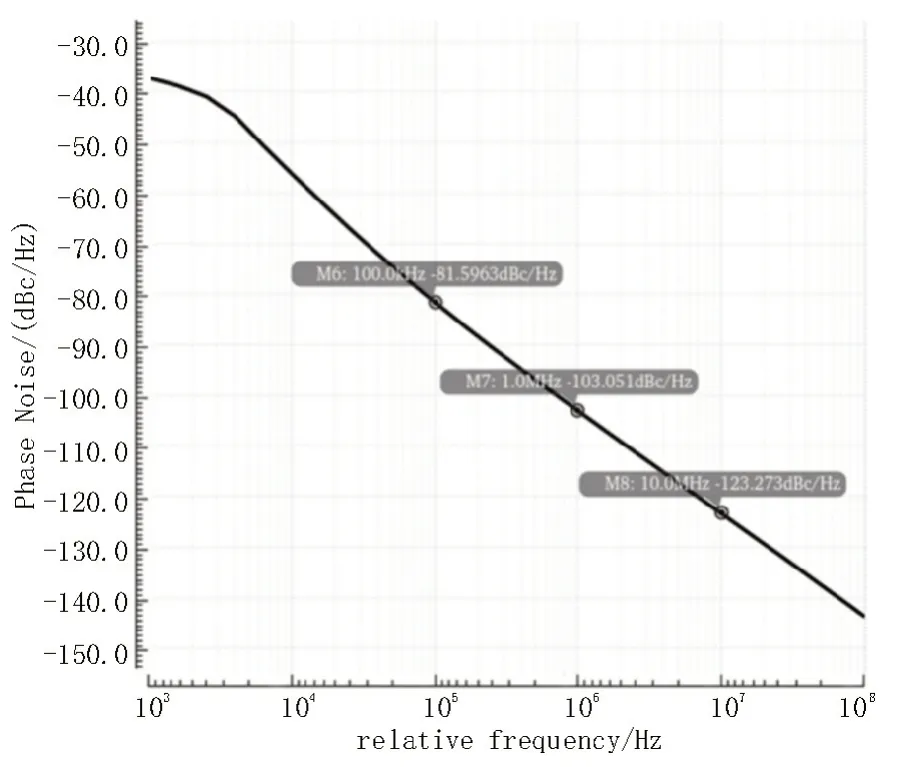

VCO 采用SMIC 40 nm 射频CMOS 工艺设计,调谐特性如图7 所示,相位噪声性能如图8 所示。

图7 VCO调谐特性

图8 VCO的相位噪声性能

可以看出,设计的4 bit 调谐阵列使得VCO 的调谐范围为24.09~29.85 GHz,约为6 GHz,1.1 V 电源下平均工作电流为2.2 mA。虚线右侧部分是通过使用两个独立的偏移Vdc:0.3 V 和0.6 V,来提高频率调谐范围,采用该方案,各频段的调谐范围扩大了41.8%,重叠增加了20%。图8 所示为VCO 的相位噪声性能,相位噪声在1 MHz 偏移处为-103.05 dBc/Hz,在10 MHz 偏移处为-123.27 dBc/Hz。仿真结果表明,设计的VCO 具有低功耗、低噪声、宽调谐范围的优良性能。

4 振荡器测试结果

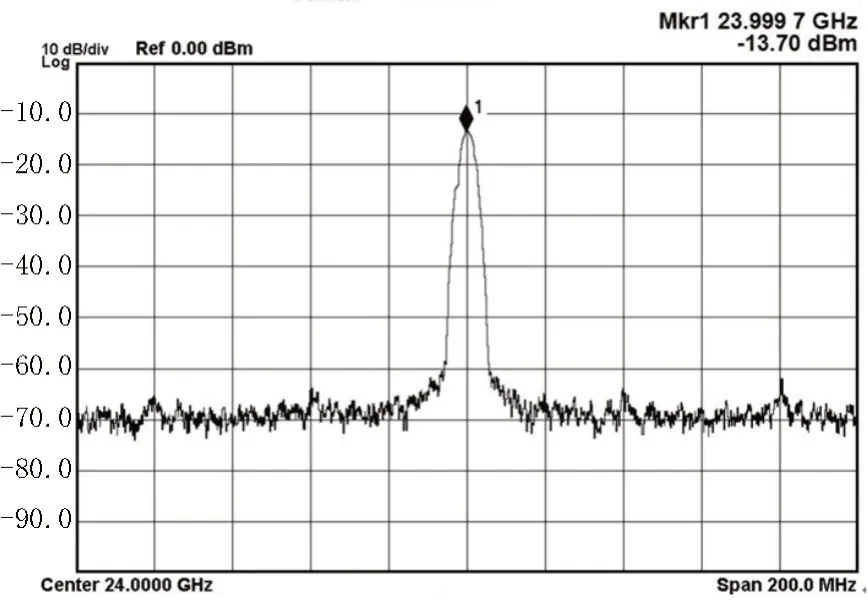

芯片采用COB 封 装,PCB 采 用FR4 板 材,外接1.1 V 电源板作为芯片的供电电源,采用Keysight N9040B 进行频谱测试。输出频率为24 GHz 时,频谱如图9 所示。

图9 VCO芯片测试频谱图

芯片不同控制位下,输出频率范围如表1 所示,整体调谐范围达到6 GHz 左右,功耗为2.42 mW。

表1 VCO输出频点值

5 结论

基于SMIC 40 nm 射频CMOS 工艺,设计了应用于24 GHz 频段,一种低功耗、低噪声、宽调谐范围的压控振荡器。流片测试结果表明,实现了6 GHz的宽调谐范围,1.1 V 电源下工作电流2.2 mA,功耗2.42 mW,相位噪声为-103.05 dBc/Hz@1 MHz和-123.27 dBc/Hz@10 MHz。该压控振荡器模块可应用于24 GHz 频段的doppler 和FMCW 雷达系统,实现测距测速的功能。