基于FPGA 的高速模数转换器评估系统

陈旻琦,邓岚清,杨琳韵

(中科芯集成电路有限公司,江苏 无锡 214000)

0 引言

在通信与信息系统中,处理器对信号进行计算和处理,达成系统设计的功能。目前多数的电子计算机器基于二进制工作,以数字运算的方式对信息进行处理。在自然界中的信号是连续的模拟量,这意味着要处理模拟信号要对模拟量进行量化,转换为电子计算机可以处理的数字信息[1]。将模拟信号转换成数字信号的电路称为模数转换器(ADC)。根据奈奎斯特定律[2],ADC 转换信号的速率越快,可以转换的信号频率越高,因此,高速ADC 广泛应用于射频、通信、雷达、电子战等高频信号场景,对高速ADC 的测试和评估在工程应用中尤为重要。

本文提出了一种基于现场可编程逻辑阵列(FPGA)的高速ADC 评估系统,设计了FPGA 逻辑和上位机程序,在实验室环境下搭建并验证了其对高速ADC 的测试效果。经实验,该系统可以完成高速ADC 的评估和测试,准确反映出ADC 的关键性能参数。

1 系统架构

ADC 测试通常以FPGA、数字信号处理器(DSP)分别完成ADC 的控制采集和处理传输,外挂大容量的内存芯片(DDR)来存储FPGA 从高速ADC 采集到的数据流[3]。例如亚德诺半导体公司的ADS7-V2EBZ 通用驱动板卡,其架构如图1 所示,硬件上使用Xillinx 公司的可编程逻辑阵列XC7VX330T-3FFG1157E 完成数据采集,使用亚德诺公司的微处理器ADSP-BF527KBCZ-6A进行数据处理和与上位机通信,外挂了两颗4 GB 容量的DDR3 用来进行ADC 数据的缓存和读出[4]。

图1 常见ADC 测试架构

由于其数据处理速度快,数据容量大,该架构在高速ADC 的评估系统中应用广泛,缺点是此系统硬件结构较为复杂,各个子模块之间存在多级数据链路,信号走线复杂,且需要对FPGA、DSP、上位机程序分别开发软件,对于硬件设计、软件开发和电路板制造有很高的要求,实现的成本较高。

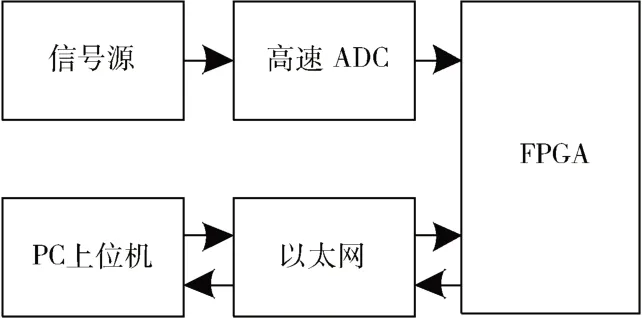

本文提出一种架构,选用FPGA 作为主要控制芯片,在FPGA 中集成ADC 的控制、高速数据流的采集存储、以太网通信等功能,将数据处理等功能转移到了电脑端,围绕FPGA 设计硬件,将软件开发集中到FPGA 端和上位机端,简化了系统结构,如图2 所示。

图2 高速ADC 评估系统架构

在本系统中,FPGA 通过以太网接口直接与电脑上位机通信,接收到控制指令后控制ADC 采样并将ADC发送的数据存储到FPGA 内部的分布式存储器(Block RAM)中,FPGA 再根据指令从RAM 中读出数据发送给电脑,在电脑端完成数据的处理和用户界面功能。这种系统结构简化了硬件板卡端的数据处理和存储等功能,降低了硬件复杂度和软件开发难度。

2 ADC 关键参数

表征ADC 性能指标的参数可分为动态参数和静态参数,分别表示ADC 采样变化信号的能力和自身对模拟量转换的内部工作特性。动态参数主要有信噪比(SNR)、信纳比(SIAND)、总谐波失真(THD)、无杂散动态范围(SFDR)和有效位数(ENOB,可由SNR 换算得到)等;动态参数主要由微分非线性(DNL)和积分非线性(INL)表征。

动态参数的测试方法是给ADC 输入高精度的正弦波信号,对ADC 采样转换后的数据进行傅里叶变换,进行频谱分析。理想ADC 模型的噪声趋近于无穷小,但实际中由于ADC 采样位数的限制,在对数据的截位量化中会产生量化噪声[8],表征到频谱的现象是在主频附近的噪底出现裙状的隆起,抬高整个噪底,会降低测得的信噪比,当提高傅里叶变换的点数时,量化噪声的影响会明显降低,因此傅里叶变换的点数越多则计算得到的值越能表征真实的频谱特性[9]。在MATLAB 中建模仿真,70.1 MHz 理想正弦波以100 MHz 采样率采集,以16 位(bit)的精度量化,当进行傅里叶变换的点数达到65 536 时,信号频谱的噪底功率约为-130 dB,量化噪声难以对计算得到动态参数产生影响;因此,本系统测试动态参数时FPGA 会存储ADC 采集的65 536 个16 bit 数据,通过以太网传输给电脑处理。

静态参数传统的测试方法是阶梯波(RAMP)测试法,给ADC 输入高精度的递增阶梯波,对应ADC 的各码字对应的电压值,统计ADC 实际采样值与理想值的误差[10],这种测试方法符合DNL、INL 的定义,测试精度高,但是对信号源精度和测试环境噪声的要求非常严苛,测试结果易受到外部影响,需要专用的测试机台和测试场所[11],通常在实验室环境下的ADC 评估系统不支持静态参数的测试功能。

本系统采用的是正弦波直方图测试法,使用信号源提供略微超出ADC 模拟输入范围(超出范围是为了让ADC 的每个码字都可以采到)的正弦波,用统计每个码字出现的概率与理想正弦波概率密度函数作对比,换算得出ADC 的微分非线性和积分非线性[12]。根据正弦波直方图的统计模型,需要较大的样本数据量以保证每个码字出现的概率,减少随机性对测试准确性带来的干扰。在MATLAB 中建模以100 MS/s 的采样率采集10 kHz的满幅度16 bit 正弦波信号,信噪比设置为100 dB,以16 bit 的精度量化,采集数据量为1 048 576 时,该算法得出的DNL 最大 为0.15,远小 于16 bit ADC 的DNL 典型值;经仿真验证,采集点数减少会导致采集的各个码字样本数量过少,导致计算结果偏大或分布过于随机。为了测试结果的准确性,本系统测试ADC 静态参数时FPGA 至少需要向电脑端吞吐大于1 048 576 个16 位数据的数据量。

3 硬件设计

本文选用亚德诺半导体的ADC 芯片AD9268-105 作为该系统的测试用例,该ADC 可实现模拟信号的16 位采样,在最高采样速率105 MS/s 下可提供78 dB 的信噪比,有效位数达12.6 位;此芯片的采样精度高,数据速率快,各项参数指标对于测试系统要求较高,能够体现评估系统的准确性和高效性。

3.1 FPGA 选型

高速、高精度ADC 的数据接口多,传输速率快,本系统将数据存储功能整合到了FPGA 中,因此需要选用一款有大量接口和存储资源的FPGA。本设计选用Xillinx公司的Kintex7 系列xc7k325tffg900-2 芯片,该型FPGA具备丰富的资源,包括326 080 个逻辑单元,16 020 kb的Block RAM 资 源,10 个IO Bank,有500 个IO 端口可供使用,内部工作时钟最高可通过内置PLL 倍频至1 GHz,经时序约束后可完成高速、高复杂度的内部布线[6],Xillinx 公司在FPGA 设计工具Vivado 中提供大量IP 核和原语供用户在程序开发中使用,可实现不同功能的逻辑设计,实现本系统的需求。

3.2 通信链路选型

本系统对静态参数的测试需要传输较大的数据量,以串口通信115 200 波特率的传输速度会导致整个测试流程时间较长,无法满足高效测试的需求。

以太网的传输速度远高于串口通信协议,其数据速率满足传输高速ADC 数据流的需求[7]。电脑端有多种网络工具(如Wireshark、NetAssist),在开发过程中便于对数据源地址、数据流、数据速率的监控,且以太网芯片价格普遍比较低廉,因此本系统以百兆以太网作为FPGA 和上位机之间的通信方式,选用了REALTEK 公司的RTL8201CP 实现,可支持最高100M 的用户数据报协议(UDP)传输。

4 软件设计

4.1 FPGA 逻辑设计

FPGA 在系统中作为主要底层控制芯片,负责ADC的模式配置、接口控制、数据接收保存、以太网指令接收、工作状态切换、数据组帧等功能。

FPGA 逻辑 在Vivado 2018.4 上开发,基于VHDL 语言,通过内嵌的XSIM 仿真器对各子模块进行逻辑仿真,并可在内嵌的CHIPSCOPE 调速器中在线调试验证;电脑端的上位机开发基于MATLAB 完成图形操作界面和通信运算;FPGA 与电脑端通过网线交连,实现以太网通信。

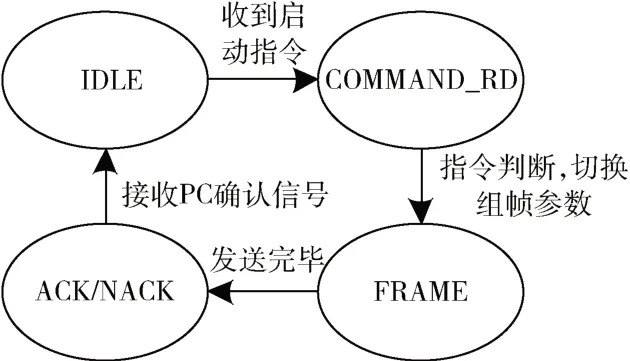

FPGA 顶层逻辑框图如图3 所示。

图3 工作状态转换逻辑

顶层逻辑分为4 个状态机:空闲(IDLE)、指令解码(COMMAND_RD)、组 帧(FRAME)、应 答(ACK/NACK)。由以太网传达电脑端的指令驱动状态机的转换,收到启动指令后,判断程序的工作模式,载入程序中预置的参数进行对应方式的组帧,在发送完毕后通过应答信号判断该次传输是否正确完成。

4.1.1 存储逻辑设计

本设计中的RAM 包括两种存储状态:动态参数存储状态和静态参数存储状态;复用同一个双端口RAM,共计消耗5 个18 KB RAM 资 源和438 个36 KB RAM 资源。FPGA 根据接收解码的指令控制RAM 的存储有效标志和存储深度,接收存储ADC 传输的并行数据,ADC在配置完成后流水地向FPGA 吐出LVDS 格式的数据,经FPGA 解码后得到信号模拟量经ADC 转换后的量化值。

在动态参数存储状态中,FPGA 收到指令后,以ADC的数据随路时钟作为RAM 的写入时钟,在65 536 个时钟周期内连续地向RAM 中写入ADC 吐出的数据,构成一个完整的数据帧。

在静态参数存储状态中,FPGA 收到指令后,产生周期性的帧信号,根据帧信号完成数据的存储与读取,每次帧信号拉高时向RAM 写入65 536 个时钟周期内ADC吐出的数据,覆盖上一帧存储的数据,并通过UDP 发送给上位机,总共分为16 帧发送,总计发送1 048 576 个周期的数据,符合直方图测试法的数据量要求。

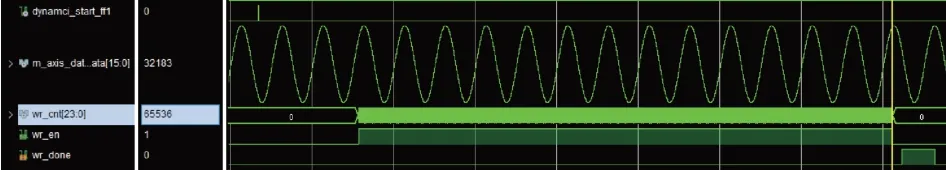

RAM 存储工作时序如图4 所示,在收到指令并解码后,FPGA 产生一个触发信号脉冲dynamic_start_ff1,进入存储状态,wr_cnt 和wr_en 信号控制写入RAM 的地址和有效数据,被存储到RAM 中的即为wr_en=1 时的一段正弦波数字信号,在存储数据量计数器wr_cnt=65 536后,产生一个wr_done 信号触发下一步状态机运行,完成RAM 对一帧数据的存储。

图4 RAM 存储工作时序

在分析动态参数时,如果出现数据点的遗漏或错误,均会导致时域信号的相位不连续,傅里叶变换后频谱发生畸变,影响测试结果,因此动态存储状态下的数据需要在一段时间内连续采集并存储完成;而在分析静态参数时,直方图测试法是对数据点出现的概率进行统计,因此可以允许数据之间存在断点,不要求数据在时域上的连续性,可以允许每帧存储的数据之间没有连续时间关系,此测试方法的关键在于大数据量的存储和传输,虽然xc7k325tffg900-2 的总RAM 资源可以满足本设计的存储量要求,但在资源利用较多时,布线面积大、走线长带来的时序不确定性会限制时序逻辑的工作时钟,并带来实际工作时的时序错误,对FPGA 综合后的逻辑布线和时序约束有较高要求[13],本设计中的ADC、RAM、以太网的工作时钟均为快时钟(>25 MHz),受到时序不确定的影响较大[14]。因此,本系统在静态参数测试模式中采取逐帧存储-读取-覆盖的方式复用RAM,尽可能节约硬件资源,提高逻辑的稳定性,减少逻辑设计难度。

4.1.2 通信协议设计

本设计的以太网通信通过UDP 实现FPGA 到上位机的数据交互,以数据包的形式进行数据的发送与接收,UDP 对单包发送的数据长度有大小限制,相邻数据包的传输之间需要短暂的时间恢复并为下一包数据的接收做准备,在100M 以太网中通常将最大长度限制为1 500 字节,两包之间至少间隔960 ns,过长的数据包和过高的发包频率均会导致丢包、乱码等现象[15],为了避免UDP 传输时的错误对本系统产生影响,将RAM 中储存的数据帧,共65 536×16 bit,拆解成多个数据包,以固定的时间间隔组成以太网数据包发送;在动态模式下只需要发送一个数据帧,在静态模式下需要发送16 个数据帧。

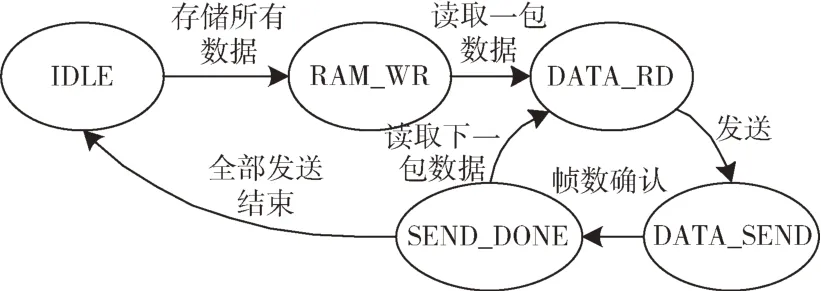

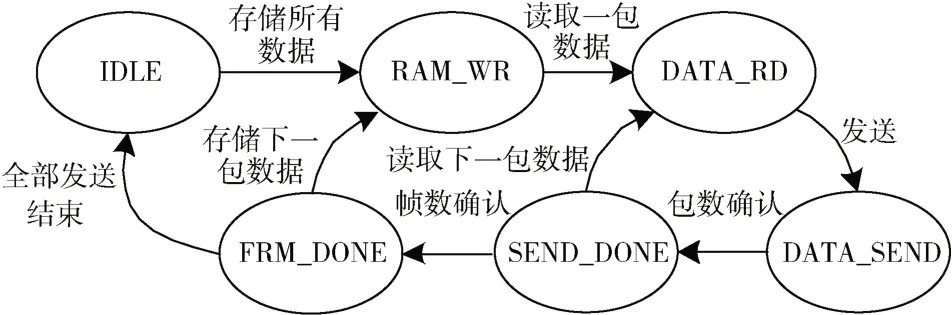

在组帧(FRAME)状态下,FPGA 会根据指令切换进入两种工作模式的状态机,动态参数测试模式下的FRAME 状态转换如图5 所示,静态参数测试模式如图6所示。

图5 动态参数测试模式下状态机转换

图6 静态参数测试模式下状态机转换

在两种工作模式下RAM 中一次性存储的数据均为ADC 在一段时间内连续采样的数据,区别是动态参数模式只需要完成一次数据帧的存储-传输,通过一帧内接收数据包的数量确保数据的连续性,而静态参数模式在每次发送完数据时,确认包数的同时会确认当前帧数,判断是否触发下一次存储-读取-覆盖。由于UDP 是面向事务的不可靠信息传送,无法得知数据包是否完整到达目的地[16],为了保证ADC 采样的数据不发生丢包,本设计在数据包中加入包头信息,指示当前数据包的包号、帧号以及当前数据点的编号,在接收端校验其连续性判断是否发生丢包现象,决定是否触发复位重传;在数据包尾附加校验码,保证在数据包中的数据正确性。UDP 的传输速度较快,在数据包中增加冗余信息以确保数据传输的准确性是可行的。

在FPGA 逻辑中以RAM 的存储完成标识wr_done 信号触发第一个数据包的组包发送(pkg_start),一个完整数据包格式包含前导码、帧头、数据、校验等;其中包含源IP、目的IP、MAC 地址、包号、帧号、数据编号、校验和等信息,发送请求信号tx_req 每次上升沿触发对RAM一个地址数据的读取,如图7 时序所示。

图7 以太网组包工作时序

单包数据读取到RAM 存储最大深度的地址后产生pkg_done 信号,表示当前RAM 中存储的数据已全部读取完成,等待延时后触发下一个数据包的组包发送,图8是多个数据包发送的时序图,当eth_tx_en=1 时,表示正在发送RAM 中的数据,将多个数据包发送的r_bram_rdata 数据拼接后即可恢复出ADC 采样得到的连续的正弦波数据。

图8 多数据包发送时序

4.2 上位机程序设计

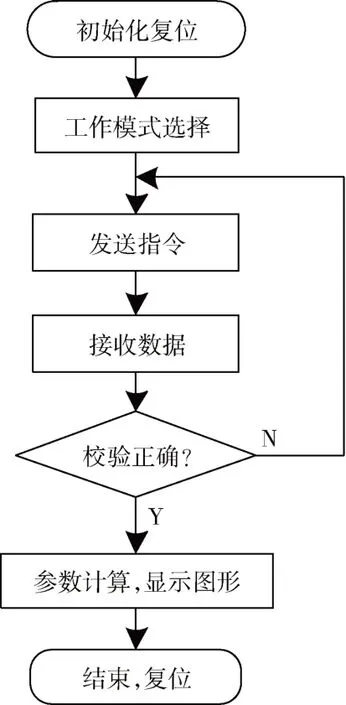

本设计的电脑端上位机主要功能为UDP 指令控制、数据包接收、数据计算分析、结果显示等,基于MatlabR2019b 的Appdesigner 工具设计了用户操作界面,可生成独立的可执行文件,工作流程如图9 所示。

图9 上位机工作流程

程序初始化以后对工作区的变量进行复位,根据当前切换的选项卡选择工作模式,调用对应参数和函数,生成指令通过UDP 发送到FPGA 端,调用MATLAB 提供的udp 回调函数实现多包数据的接收和存储,为了避免udp 协议的不可靠性带来的丢包,函数中对接收到的数据总量和数据包编号进行校验,校验错误重新发送指令触发数据重传。确定数据接收无误后,对参数进行计算,将测试结果和图像显示到用户界面上。

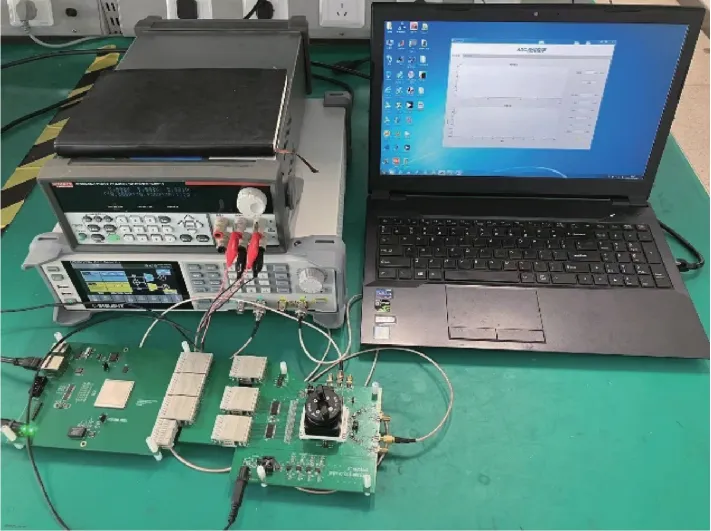

5 实验验证

高速ADC 评估系统的全套实验环境包括ADC 评估板卡以及FPGA 主控板卡套件、直流稳压源、高精度信号源、音频信号发生器和个人笔记本电脑,如图10 所示。

图10 实验平台

测试ADC 动态参数的输入信号为频率2.5 MHz、70.1 MHz、140.1 MHz 和201.1 MHz 的正弦波,功率设定为-3 dBm,由高精度射频信号源提供,采样频率设定为100 MHz,根据奈奎斯特定律采样得到的频率理论值依次为2.5 MHz、29.9 MHz、40.1 MHz、1.1 MHz,接收的数据总量应为262 144 字节,使用网络助手Wireshark 抓取接收到256 个1 024 字节的包,数据包头编号连续,数据未发生丢包。

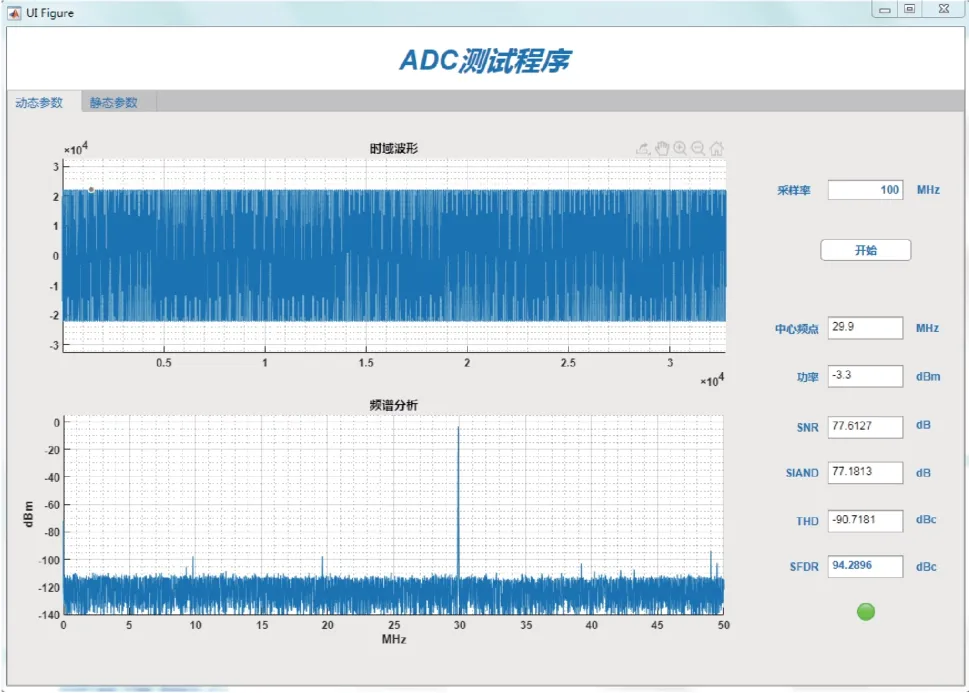

以70.1 MHz 的输入条件为例,时域波形为了美观和清晰截取其中500 个点进行显示,频谱分析显示第一奈奎斯特域。经FFT 处理后计算得到的动态参数显示到参数区域:SNR=77.6 dB,SIAND=77.1 dB,THD=-90.7 dBc,SFDR=94.2 dB,如图11 所示。动态参数测试过程总耗时为0.8 s。

图11 70.1 MHz 动态参数测试结果

对所有频点的测试结果如表1 所示。

表1 动态参数测试结果

测试ADC 静态参数的输入信号为频率10 kHz、功率峰峰值Vpp=2.5 V 的正弦波,由音频信号发生器提供,采样频率设定为100 MHz,用Wireshark 抓取得到4 096 个1 024 字节的包,共计4.2 MB 的数据,数据包头编号连续,在大数据量下未发生丢包。

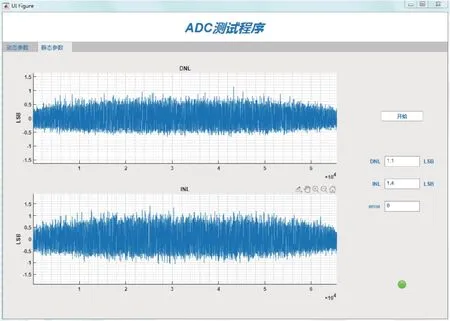

完成数据接收和校对后根据直方图算法得到各个码字点的DNL 和INL 曲线,取最大值显示到参数区域,得到ADC 的静态参数:DNL=1.0 LSB,INL=1.4 LSB,如图12 所示。

图12 静态参数测试结果

静态参数测试过程总计耗时11.2 s,其中数据传输过程耗时3.1 s,数据处理过程耗时8.1 s,优化电脑硬件可以大幅提升数据处理速度。经过对照,测试得到的各项参数指标均与ADC 典型值接近,多次测试结果稳定,系统处理速度快。

6 结论

综上实验结果,高速ADC 评估系统能够实现高速模数转换器的性能参数评估,测试结果中各项指标均满足示例ADC 的典型值,工作稳定,测试效率高,本设计的数据处理与采集存储分别由电脑和FPGA 来实现,底层硬件运行逻辑由FPGA 确定后,电脑端的数据处理算法可以根据实际需求进行升级和修改,软件设计具有很强的可扩展性。