一种适用于SHE 规范的安全加密电路设计

史兴强,刘梦影,王芬芬

(1.中国电子科技集团第五十八研究所,江苏 无锡 214035;2.中科芯集成电路有限公司,江苏 无锡 214072)

0 引言

当今世界随着全球信息化和网络化的高速发展,信息安全问题也与日俱增,信息安全问题在各个领域越来越受到重视[1],汽车行业尤其显著。当前社会对于汽车的需求往往更偏向于功能的提升,因此汽车电子系统日渐复杂且越来越数字化,汽车电子系统不仅需要具备运算更强的控制单元,更高速的数据传输功能[2],更集成了无人驾驶、物联网和5G 等新技术,因此,安全、智能、可靠和低碳环保的网联汽车必然是全球汽车行业共同的发展趋势[3]。汽车电子系统复杂化和数字化导致车载电子系统的数量越来越多,从而使得车辆越来越易受到网络安全攻击。汽车系统不仅存储大量的用户数据(包括车辆行驶记录、车主个人信息和导航数据等),而且具有众多ECU,用户数据的窃取和篡改或者ECU 非法替换等都会造成经济甚至生命的损失,因此对汽车系统进行信息安全防御是非常必要的。

近年来,针对如何加强汽车信息安全,许多研究提出相关方案。王玲[4]提出了一种基于AES 的RKE 单向认证协议改进的双向通信认证协议,采用一个固定密钥和一个动态密钥的AES 加密来保证数据的安全性,并将该协议应用于免钥门禁技术,但是该协议不存在对密钥的管理机制,存在密钥泄露的风险。刘鹏[5]提出了一种适用于短码场景的车联网安全通信方案,采用ECC 和AES 结合的混合加密方案,选用QR 码完成数据检错纠错,实现安全、可靠、高吞吐的数据传输。孙怡琳[2]在XXTEA 异或加密算法和HMAC 认证算法的技术基础上,设计了一种动态加密机制来实现车内网络CAN 总线的安全通信。王龙[3]设计了一个面向汽车的数字身份管理系统,可以对车辆本身和主要电子零部件的数字身份进行有效识别和管理。

本文基于AES 算法,设计了一个适用于SHE 规范的安全加密电路。该电路支持ECB 和CBC 模式下的AES-128 加密解 密、CMAC 生成和验证、Miyaguchi-Preneel 压缩算法等。此外,该安全加密模块符合SHE 规范标准,支持密钥管理、运算隔离等保护措施,具有严格的访问权限,由硬件域控制加密密钥的管理,保护密钥免受软件攻击,提高设备信息安全性能,以获得比软件执行更好的硬件性能和保护。

1 AES 加密算法

AES 算法是2001 年由NIST(美国国家标准技术研究所)为替代数据加密标准(Data Encryption Standard,DES)而发布的新一代数据高级加密标准[6]。该算法是由比利时科学家Joan Daemen 和Vincent Rijmen 提出的,它是一种明文分组长度和秘钥长度均可变的分组密码算法,也是一个对称分组算法。其明文分组长度和秘钥长度都可独立地设定为128、192 或256 比特[7],与秘钥相关的迭代轮数Nr 分别为10、12 或14 轮[8]。在AES高级加密标准规范中限定明文分组长度只能是128 比特,秘钥长度可选择三者中的任意一种。

1.1 AES 加密流程

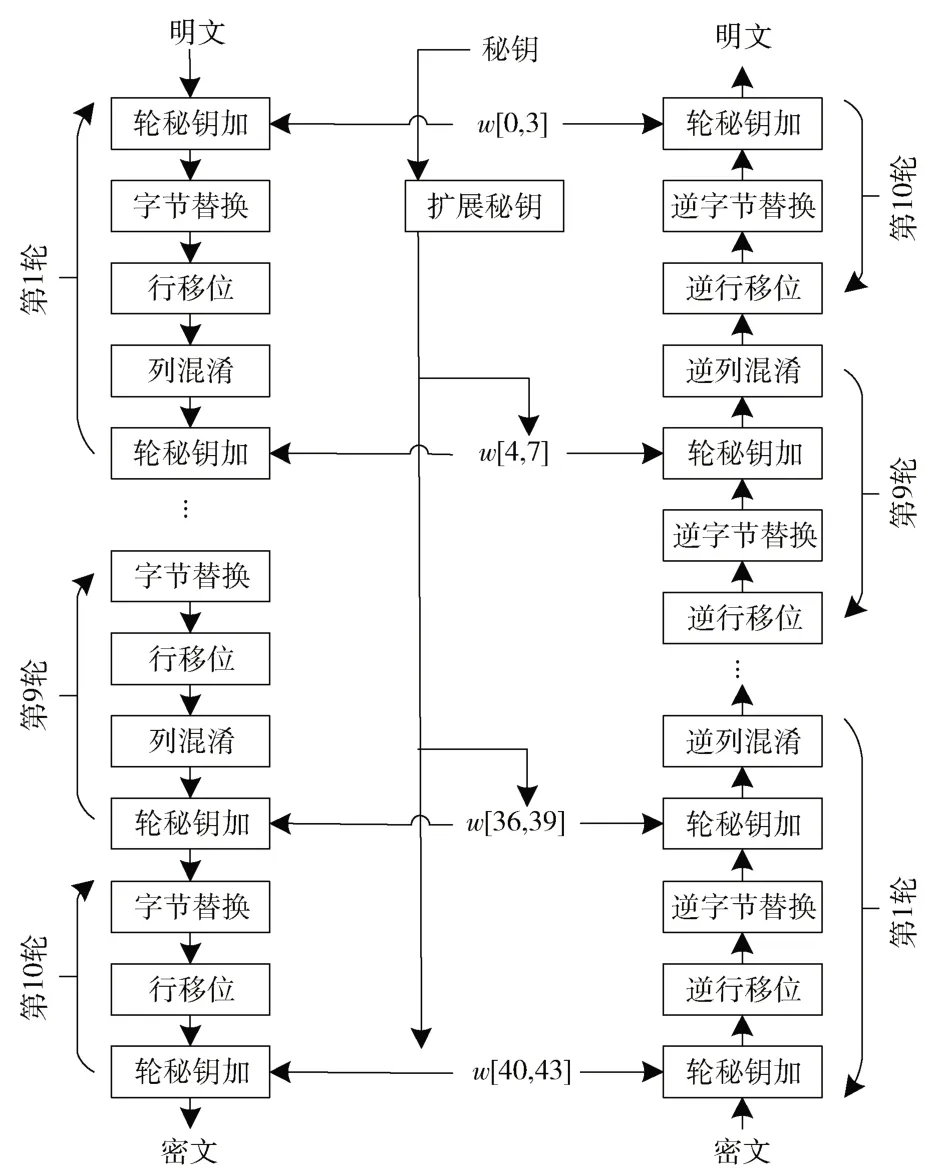

AES 加密算法主要完成明文到密文的转换,包含字节替换、行移位、列混淆和轮秘钥加4 个步骤[9],其算法结构如图 1 所示,共计10 轮变换。

AES 算法以字节为单位进行运算,其中的明文是一个128 比特分组,即16 个字节,被描述为一个4×4 的状态矩阵,其中前4 个字节被复制到第1 列,紧接着的4 个字节被复制到第2 列,依次往下,最后4 个字节被复制到第4 列。例如一个128 比特数据A,其表示为:A=a0,a1,a2,…,a15,则在进行加密运算时,表示为矩阵S,形式如:

字节替换又叫做S 盒替换,用来完成明文分组的字节到字节的替换,它可通过S 盒把输入或中间态s 中的每一个字节{xsys}映射为另一个字节,对每一个字节数据中的每一位都能起到混淆作用。AES 中,只有字节替换是非线性变换,因此在面对已知攻击时字节替换具有极其重要的作用,在秘钥扩展过程中也使用了该运算。S 盒替换运用查找表的形式实现,虽然该方法占用较大的硬件资源,但关键路径短、速度快、结构简单且设计实现难度小,综合考虑硬件资源和速度两个因素,该方法最为合适。

行移位是对状态矩阵S的行进行循环的移位操作,将某个字节从一列移动到另一列,它的线性距离是4 字节的倍数,这个转换能够确保每列中的任意一个字节都移到不同的列中。对于一个4×4 的状态矩阵,秘钥长度为128 比特,第0、1、2、3 行根据密钥长度分别向左移动0、1、2、3 个字节。

列混淆是对行移位后的状态矩阵S进行列的变换,将状态矩阵的每一列看作系数取自有限域GF(28)且次数小于4 的多项式,然后与多项式c(x)相乘并模多项式x4+1。AES 算法给出c(x)={03}x3+{01}x2+{01}x+{02}[10]。

列混淆变换中每列的运算可用如下矩阵表示:

轮密钥加是将数据加密和密钥结合的过程,通过列混淆后的矩阵S与轮密钥矩阵W做相加运算实现,即进行异或操作,配合相对复杂的密钥扩展流程可以保证该步骤的复杂度。其运算过程如下所示:

密钥矩阵W通过密钥扩展获得,由图 1 可知,整个AES 算法加密需要10 轮运算共计11 次轮密钥加,且每一轮相加的子密钥均不同。秘钥扩展是加解密重要的组成部分,通过对初始的128、192、256 位秘钥进行扩展,产生每轮轮变换中需要的秘钥。

当秘钥长度为128 比特时,先将种子秘钥划分为4个字,再通过秘钥扩展运算生成每轮迭代所需的4 个秘钥字,最终完成44 个32 位字的构造。

密钥扩展的基本原则如下[11]:

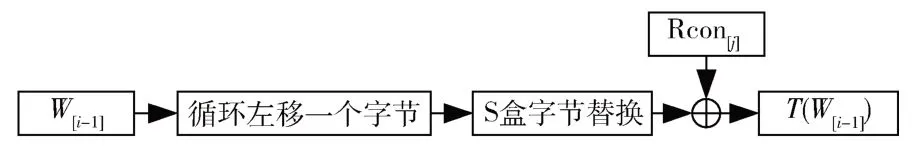

密钥扩展涉及的函数T是在简单的异或运算中进一步混淆密钥生成过程[12],该计算过程如图 2 所示。

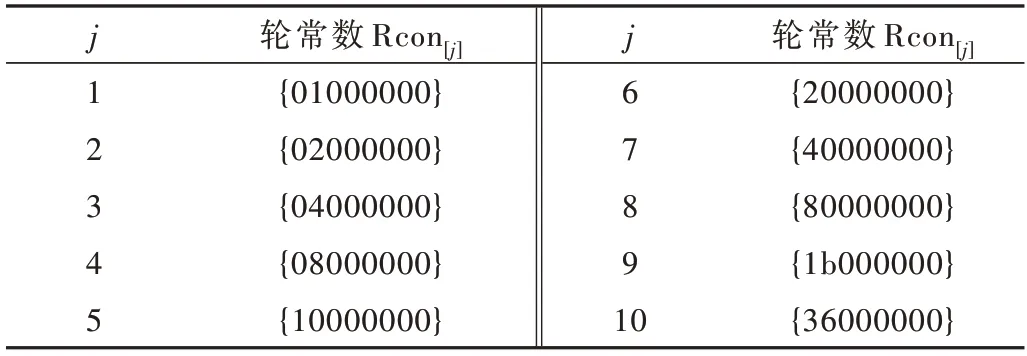

图2 中,Rcon[j]为轮常数,其中j=i/4,Rcon[j]与j的关系在表 1 中列出。

表1 轮常数

1.2 AES 加密模式

NIST 于2000 年3 月为AES 散发公开征集工作模式[13],并于2001 年公开了5 种工作模式,分别为电子密码本(Electronic Code Book,ECB)模式、密文分组链接(Cipher Block Chain,CBC)模 式、密文反 馈(Cipher Feedback,CFB)模式、输出反馈(Output Feedback,OFB)模式、计算器(Counter,CTR)模式[14],SHE 规范涉及其中的ECB 和CBC 两种工作模式。

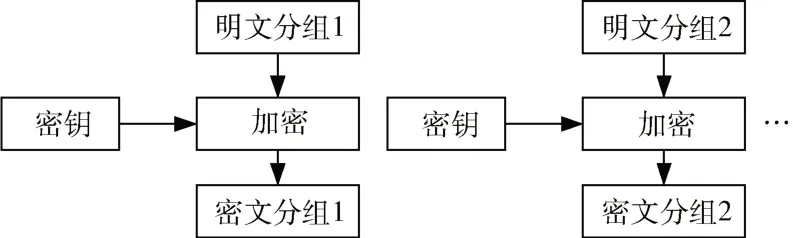

ECB 模式是最早采用和最简单的模式,它将加密的数据分成若干组,每组的大小与加密密钥长度相同,每组使用相同的密钥进行加密。ECB 模式加密过程如图3所示,该模式明文分组与密文分组是一一对应的关系,且加密分块之间不相互影响,可通过密文的规律推测出明文规律,存在一定的风险。

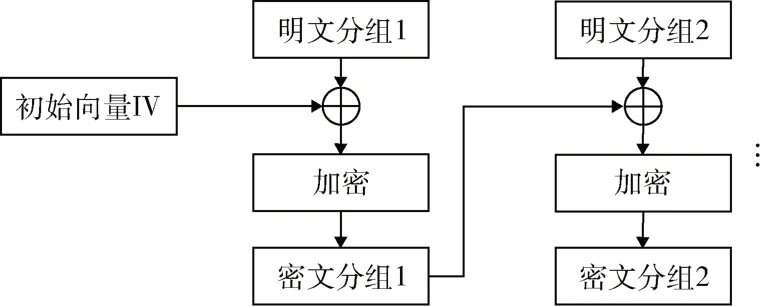

CBC 模式在加密当前明文块时需与前一个密文块进行异或计算后再进行加密操作[15],第一块需要初始向量进行异或运算,然后加密作为第一块密文块,随后每一个明文分块在加密前均需与前一个密文块进行异或运算,随后再进行加密运算。加密过程如图4 所示。因此,每一次加密都需要前一次密文的参与,明文中微小的改变都会使后续所有的密文改变,该模式具有较高的安全性。

2 安全加密电路设计

本文设计了一种安全加密电路,该电路基于AES 加密算法,支持ECB 和CBC 模式下的AES-128 加密解密、CMAC 生成和验证、Miyaguchi-Preneel 压缩算法等。此外,该安全加密模块符合SHE 规范标准,支持密钥管理、运算隔离等保护措施,提高设备信息安全性能,以获得比软件执行更好的硬件性能和保护。

2.1 SHE 规范

SHE 在车联网中,被应用在车端ECU 中负责安全存储和安全计算,是由HIS 制定的标准。它旨在将对加密密钥的控制从软件域移到硬件域,从而保护这些密钥免受软件攻击,设备和数据的安全性仅依赖于算法的强度和密钥的机密性。

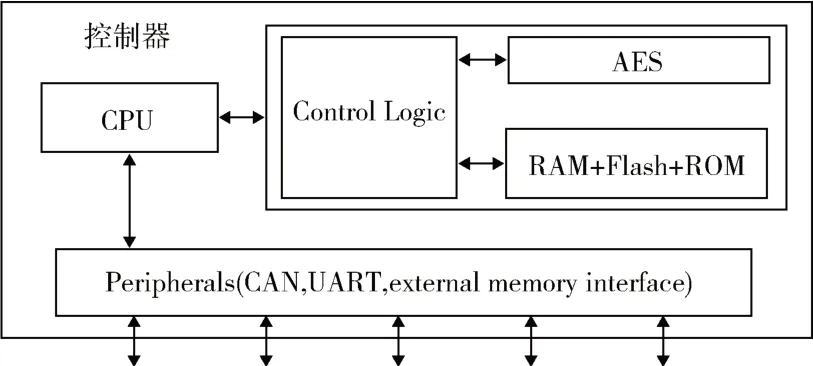

图5 为SHE 逻辑结构图,有一块单独的安全区域,该区域中即为SHE 定义的模块,该模块包括控制逻辑、AES 算法、存储单元、伪随机数生产器,且该模块仅与CPU 通信。同时,SHE 必须被实现为微控制器的片上外围设备,可通过多种方式连接到CPU,如:通过专用接口或内部外围总线,互连必须以其他外设或外部实体不能修改CPU 和SHE 之间传输数据的实现方式。

AES 算法即为AES-128 的加密和解密算法,通过控制逻辑模块控制加载密钥和数据信号,输入数据流等,调用AES 算法模块以实现ECB 和CBC 模式下的AES 加解密、CMAC 生成、压缩函数等算法;存储单元存放密钥数值、密钥属性等相关信息,密钥相关信息仅允许控制逻辑访问,且不能随意读取和修改;执行命令的控制信号、输入数据以及需要输出的数据等,SHE 规范涉及的命令在表 2 中列出,每条命令实现不同的功能,且对应一个FuncID,应用程序将要执行的命令、所需控制字段和输入数据按照一定的格式通过总线写入存储单元,控制逻辑从中读取并解析,完成指令操作。

2.2 算法硬件实现

本文设计的安全加密电路支持AES-128 在ECB 和CBC 模式下的加密和解密、CMAC 的生成和校验、Miyaguchi-Preneel 压缩算法,其中CMAC 的生成和Miyaguchi-Preneel 压缩算法均基于AES 算法实现。

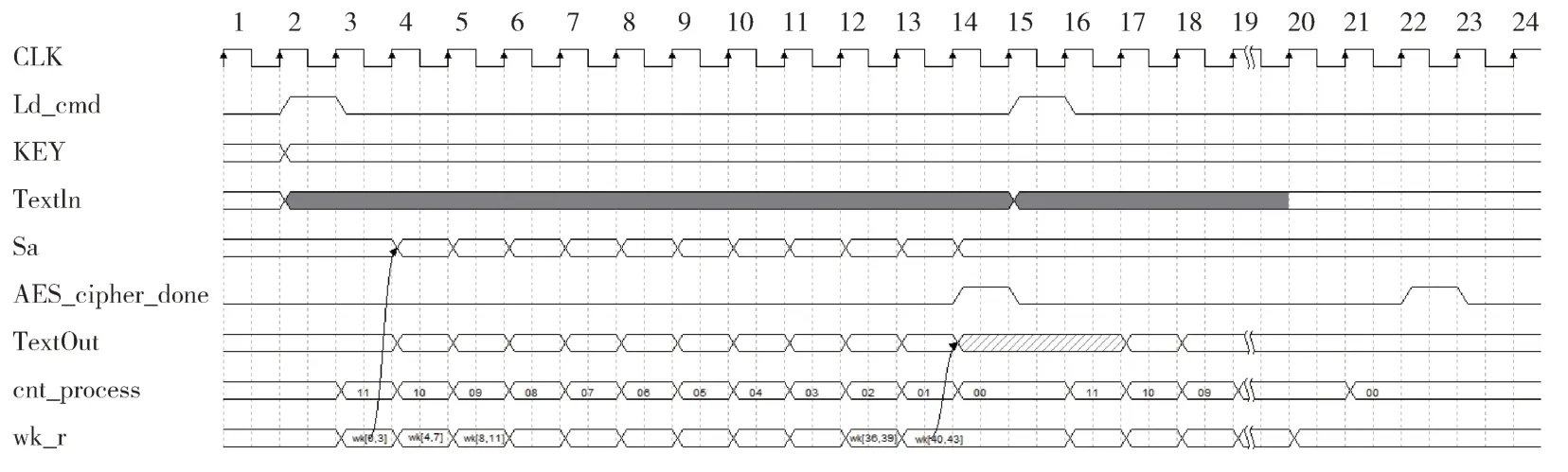

根据2.1 节介绍的AES 加密流程,设计了AES 算法模块。输入信号包括加载密钥或数据控制信号Ld_cmd,128 比特的密钥数值KEY,128 比特明文数据TextIn,输出信号包括当前明文加密完成信号AES_cipher_done,128 比特密文数据TextOut。图6 所示为AES加密时序,T2 时钟周期,Ld_cmd 有效,同时密钥KEY 和密文TextIn 一并输入;下个时钟T3 周期密钥扩展开始进行计算得到第一轮扩展密钥wk[0:3],与明文进行异或计算得到状态矩阵Sa(T3);T4 周期,将状态矩阵Sa(T3)通过S 盒替换,行移位和列混淆等计算,并与下一轮扩展密钥wk[4:7] 进行异或计算得到第一轮状态矩阵Sa(T3),以此类推,在进行最后一轮计算时即T14 时钟周期,Sa(T13)通过S 盒替换和行移位计算后,与扩展密钥wk[40:43]进行异或运算得到最终的密文,此时加密完成信号AES_cipher_done 置为1,TextOut 输出有效密文数据。

该设计采用迭代运算过程和流水线结构,可以复用硬件逻辑循环迭代来进行运算,节约了逻辑资源,虽然需要消耗多个时钟周期才能得到一个密文数据,但其吞吐率能够满足SHE 规范规定的最大2 μs 的等待周期。

图7 为CMAC 计算过程,将信息码分为n个128 比特的信息块,即M=M1||M2||…||Mn-1||Mn*,采用AES-128 CBC 模式,使用密钥K对每块信息码进行加密,对于最后一块信息码,不仅需要根据其位宽补全128 比特,还需根据密钥K计算得到所需K1和K2,如果最后一块信息码Mn*为完整的信息码,则Mn*与K1异或之后作为最后一个信息码进行AES-128 加密计算;如果Mn*为非完整的信息码,则先补齐Mn*,再与K2异或之后作为最后一个信息码进行AES-128 加密计算。取最后一组密文的高有效位Tlen 作为MAC 值OUTn。

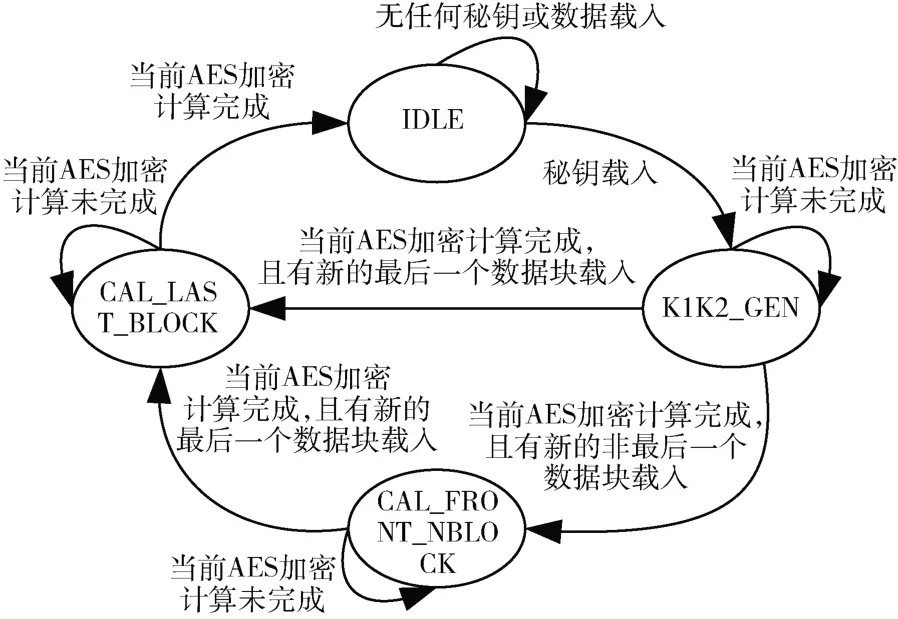

根据CMAC 计算过程,且为便于正确地处理密钥载入和数据载入控制信号,以及输入数据流,本文在实现CMAC 算法硬件电路设计了一个有限状态机,其状态和跳转条件在图 8 中详细标出。该状态默认处于空闲状态(IDLE),当密钥载入控制信号有效,且密钥数值K同时输入,则状态跳转至K1、K2生成状态(K1K2_GEN),此时调用AES-128 的CBC 模式加密算法,使用密钥K对0128进行加密;K1和K2计算完成之后,可载入待计算的数据Mi,如果Mi不为最后一个信息码,状态处于跳至计算前N个信息码状态(CAL_FRONT_NBLOCK),同样调用AES-128 的CBC 模式加密算法,每次当前信息码加密完成之后,再载入新的数据进行AES 加密;当计算最后一个信息码时,状态跳至CAL_LAST_BLOCK,该次加密得到的密文即为CMAC 结果。

Miyaguchi-Preneel 压缩算法是一种单向密码散列函数,由Miyaguchi 和Preneel 于1992 年提出,主要用于数据完整性检查、数字签名等安全应用场景。相较于SHA-1 和 MD5 等传统的密码散列函数,MP 压缩算法不仅可以提供相同的安全保障,而且具有运算速度较快、安全性好、内存占用小等优势。该压缩算法的每一块消息都会作为明文Mi,而前一块明文的压缩结果OUTi-1作为密钥,对Mi进行AES 加密计算,输出之后的密文、Mi和OUTi-1三者进行异或运算,最终得到当前明文的压缩数据OUTi,该算法的表达式如下所示:

其中,OUT0=0128。

2.3 安全加密模块硬件设计

基于AES 算法,本文设计了一种适用于SHE 规范的安全加密模块,设计框图如图9 所示。该电路主要包括4 个 模块:AES 算 法模 块、SHE_ctrl 模 块、PRAM_ctrl 模块以及Flexram_ctrl 模块。AES 算法模块主要实现AES-128 加密和解密功能。SHE_ctrl 模块主要实现SHE 指令解析、控制算法输入信号和指令输入输出数据流等。用户程序可通过总线向CSEc_PRAM 中按照规定的格式和地址写入命令相关信息,包括包含FuncID 的命令头、控制字段和输入数据等,安全加密模块则通过PRAM_ctrl模块从CSEc_PRAM 获取指令相关信息,待SHE_ctrl 模块完成该指令,将需输出的数据和状态信息写入CSEc_PRAM 供用户程序获取。FlexRAM 中存放密钥及其相关信息,规定每个密钥存放在相应的地址,SHE_ctrl模块通过Flexram_ctrl 对相应的密钥区域进行读写操作。由此可知,该安全加密模块严格控制了密钥的访问权限,仅SHE_ctrl 模块可以读取密钥数值等相关信息;且在命令执行过程中,运算过程和数据不被其他模块和应用程序影响和访问。

本文设计的安全加密模块支持表2 列出的所有指令,由于同一时间仅能够执行一条指令,且不同的指令存在访问相同地址区域、调用相同算法等共性操作,因此为节约硬件资源,提高指令完成效率,设计了指令处理状态机(如图 10 所示),该状态机共有17 个状态。

表2 SHE 指令

表3 对于每个状态进行了简要的阐述,根据命令操作的具体流程,合并相同的步骤,整理得到表中列举的状态。例如,Rd_CSEc_Pram_ST1 状态,每条指令都需跳转至该状态,读取命令头,并判断相关信息是否有效,如果命令头判定为无效则状态跳转至ERR_ST,向CSEc_PRAM 中写入该错误对应的ERROR_BIT(具体对应关系在表 4 详细列出),否则根据当前命令跳转至其他状态进行下一步操作。

表3 SHE 命令处状态描述

表4 错误情况状态跳转

表5 AES 数据测试

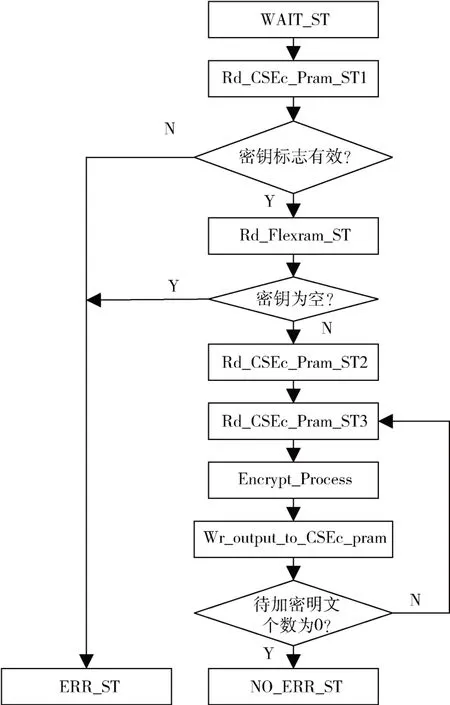

以执行指令ENC 为例,该命令是对所有明文进行ECB 模式的AES-128 加密,该指令的硬件流程如图11 所示。当应用程序通过总线写入该指令执行所需数据信息、控制信号和命令头,则状态机从WAIT_ST 跳转至Rd_CSEc_Pram_ST1,并判断密钥标志和FuncID 是否有效,如果无效则状态跳转至ERR_ST 以向CSEc_PRAM错误状态位写入相应的ERROR_BIT;否则跳转至Rd_Flexram_ST,根据密钥标志从对应的FlexRAM 地址读取该密钥数据及其属性参数,并判断密钥是否为空且密钥属性是否允许该密钥使用,如果密钥为空或密钥属性与当前不匹配,则状态跳转至ERR_ST,否则跳转至Rd_CSEc_Pram_ST2 读取控制参数待加密明文个数;紧接着再从CSEc_PRAM 中读取一个128 比特待加密明文,进入AES-128 加密进程;当加密完成,生成的密文则写入CSEc_PRAM 相应的地址,并判断是否还有待加密明文,如果有则硬件继续从CSEc_PRAM 中读取明文并进行AES 加密计算,并将密文结果写入CSEc_PRAM,如此反复上述操作,直至所有明文信息都完成加密,并输出每个密文结果,此时,状态机跳转至NO_ERR_ST,硬件在CSEc_PRAM 错误状态位写入0x800。至此,ENC_ECB 指令执行完成。

图1 128-AES 算法结构

图2 函数T 的计算过程

图3 ECB 模式加密过程

图4 CBC 模式的加密过程

图5 SHE 逻辑结构图

图6 AES 加密时序图

图7 CMAC 计算过程

图8 CMAC 计算状态机

图9 安全加密模块设计框图

图10 SHE 指令处理状态机

图11 ENC 指令硬件处理流程

3 仿真与分析

本文使用Verilog HDL 语言对所设计的安全加密电路进行设计描述,在功能仿真中搭建测试设备模型,使用Cadence irun 和 Novas Verdi 联合仿真环境。编写testcase 模拟应用程序向系统发出SHE 指令。根据SHE协议提供的测试案例,将仿真结果和案例结果进行对比,同时验证了该安全加密电路的设计是否合理可靠。

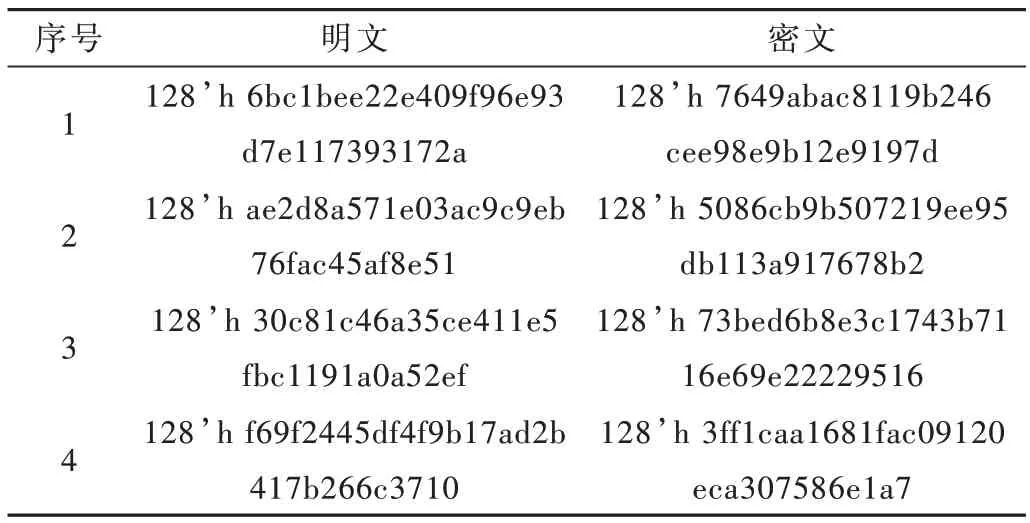

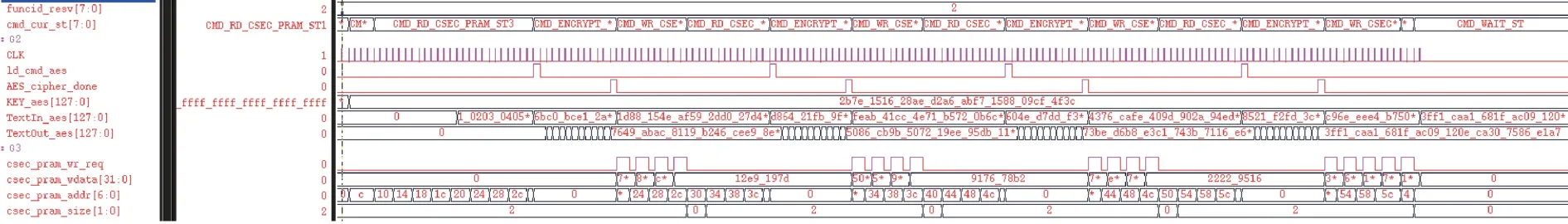

针对ENC_CBC 指令,采用密钥KEY=128’h 2b7e151628aed2a6abf7158809cf4f3c,初始向量IV=128’h 000102030405060708090a0b0c0d0e0f,明文数据和密文在表 5 中列出,该结果与测试案例提供的结果一致。

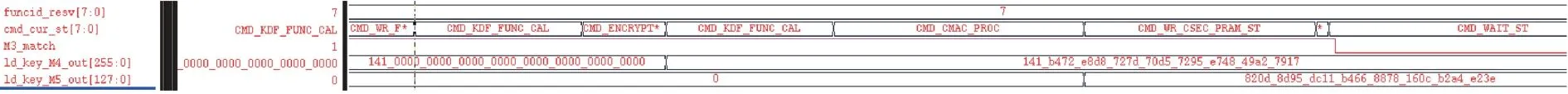

图12为加密模块执行该指令的仿真波形图。cmd_cur_st为当前状态机状态信号,ld_cmd_aes为AES算法模块加载明文控制信号,AES_cipher_done 为AES 加密完成信号,TextIn_aes 为输入数据,TextOut_aes 为输出数据。从仿真图可见,状态机跳转符合图 11 的设计,每次加密完成则将密文信息写入CSEc_PRAM 相应区域,csec_pram_wr_req连续置位4 次,完成1 个128 比特密文的写入。

图12 ENC_CBC 仿真波形

在SHE 众多指令中,执行过程最为繁琐的为LOAD_KEY 指令,也是密钥管理的主要指令,其涉及了AES 加密和解密算法、CMAC 计算、MP 压缩算法等。该命令执行流程可分为两个子流程:密钥加载/更新流程和校验信息生成流程,分别对应图13 和图14。加密模块通过压缩函数算法和CMAC 函数计算得到M3,并与输入参数M3′的值进行对比,当且仅当两参数相同(图13 中黑色标志处),状态机进入CMD_DECRYPT_PROC对相关参数解密得到密钥更新值128′h0f0e0d0c0b0a090 80706050403020100、密钥属性以及计数器值,并将上述信息存入Flex_ram 中。

图13 LOAD_KEY 命令计算M3

图14 LOAD_KEY 命令输出校验信息

加载完新的密钥之后,加密模块需要产生校验信息M4 和M5 并输出,应用程序通过比对该数值与后台计算的结果即可证明密钥更新成功。

4 结论

本文基于AES 加密算法,设计了一款适用于SHE 规范的安全加密电路,其支持AES-128 加密解密、CMAC算法和Miyaguchi-Preneel 压缩算法等。此外,其符合SHE 规范标准,仅允许硬件管理密钥,具有运算隔离等保护措施。较之传统的加密模块,该安全加密电路具有严格的访问权限,由硬件域控制加密密钥的获取和加载更新,保护密钥免受软件攻击,同时,软件不能够干预数据流的加解密过程以及密钥更新等操作,提高了设备和数据的安全性和机密性。