基于新型BIST 的LUT 测试方法研究

林晓会,解维坤,宋国栋

(中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

现场可编程门阵列(Field Programmable Gate Array,FPGA)被广泛应用于汽车电子、人工智能、网络通信等诸多领域,其复杂的可编程特性几乎成为“万能”芯片[1⁃3]。由于FPGA 内部可编程资源复杂,仅仅依靠可测性设计手段难以实现100%资源覆盖测试,因此,还需结合与应用无关的功能测试保证覆盖率[4⁃6]。

查找表(Look Up Table,LUT)作为FPGA 最重要的资源,能够实现极其复杂的存储和逻辑功能。针对LUT的覆盖率测试,文献[7]提出了以划分阵列的方式实现LUT 测试,需要4 次即可完成100%覆盖率测试,但划分和约束过程较为复杂繁琐;文献[8]提出一种基于异或门级联的LUT 测试方法,并通过穷举LUT 的输入完成覆盖率测试,但需要较多配置次数和复杂的穷举输入。文献[9⁃11]巧妙地提出一种基于内建自测试(Built⁃In⁃Self⁃Test,BIST)的资源覆盖测试方法,通过在FPGA 内部构建BIST 电路实现被测模块的覆盖测试,但未深入研究基于BIST 的LUT 测试方法,且其提出的BIST 测试方案有待进一步完善和改进。因此,本文重点研究基于BIST 的LUT 测试方法。

1 BIST 的LUT 测试方案

1.1 典型BIST 结构

典型的BIST[12⁃15]结构由测试图形生成器(Test Pattern Generation,TPG)、被测模块(Block Under Test,BUT)和输出响应分析器(Output Response Analyzer,ORA)三部分组成,如图1 所示。其中:TPG 用于产生测试向量,为BUT 提供测试图形输入,如计数器、线性移位寄存器等均能提供顺序或伪随机的测试图形;ORA用于分析比较BUT 的输出是否正常,如多输入移位寄存器、奇偶校验器等。

图1 典型的BIST 测试结构

1.2 可配置逻辑块中的查找表

以AMD 公司的Ultrascale+系列FPGA XCKU5 PFFVB676I 为例,每个可配置逻辑块(CLB)内包含8 个查找表(LUT),该型号FPGA 全部资源共含有216 960 个LUT,每个LUT 包含6 个输入、2 个输出的逻辑函数发生器,可实现任意1~6 变量输入、1~2 输出的逻辑表达式。基于FPGA 实现的众多功能中,几乎没有不涉及使用LUT 模块的,因此,为保证用户在使用FPGA 内部LUT资源时的高稳定性和高可靠性,针对FPGA 中LUT 的覆盖率测试至关重要。Ultrascale+系列FPGA 内部LUT 结构如图2 所示。

图2 Ultrascale+系列FPGA内部LUT 结构

1.3 新型BIST 结构

本文提出一种新型BIST 结构,用于测试FPGA 内部的LUT 资源覆盖率。该结构主要由测试图形生成器、被测模块、黄金模块(Golden Block,GB)、比较模块(Comparator Block,CB)四个部分组成,测试结构如图3所示。其中,黄金模块与被测模块同结构、同功能,其测试原理为:通过TPG 产生测试向量,同时输出到被测模块和黄金模块,利用比较模块对比BUT 和GB 的输出,如果两者输出一致,则证明被测模块功能正常,反之功能异常。

图3 新型BIST 测试结构

1.4 新型BIST 的LUT 测试方案

新型BIST 的结构在用于LUT 覆盖率测试时,TPG为改进的线性反馈移位寄存器(Linear Feedback Shift Register,LFSR),用于全地址的伪随机测试向量生成,作为BUT 和GB 的输入;BUT 为6 输入、1 输出异或功能的LUT,GB 同样为6 输入、1 输出异或功能的LUT;CB 为2 输入、1 输出的比较器,用于比较BUT 和CB 的LUT 输出,如果两者的异或功能输出结果一致,则判定被测的LUT 模块功能正常,否则功能异常。LUT 测试结构如图4 所示。

图4 新型BIST 的LUT 测试结构

在实际测试时,利用pBlock 功能,将FPGA 内部的LUT 资源分为上下两部分。第一次测试设计时,其中一部分用于TPG、GB 和CB 模块资源的例化,另一部分用于BUT 资源例化;第二次测试设计将两部分位置调换。这样,通过两次测试配置,即可完成所有LUT 的覆盖测试。经pBlock 约束后,一次布局布线后的LUT 测试图形如图5 所示。

图5 布局布线后的LUT 测试图形

2 测试硬件设计

自动测试设备(Automatic Test Equipment,ATE)作为LUT 覆盖率的测试验证平台,具备电源供应、任意波形发生、系统时钟、精密测量单元(包括加压测流、加流测压等)、向量存储等多种功能,因此无需外接其他测试测量设备即可完成验证评价和量产测试。测试硬件的设计主要针对ATE 的测试负载板。

XCKU5PFFVB676I 为一款亿门级FPGA,具有丰富的逻辑资源和各类IP 核,支持多种配置方式,包括但不限于Slave SelectMAP、JTAG 等,同时电源的种类也较多,设计时重点包括测试配置通道和电源供电,如图6所示为测试负载板设计方案。

图6 FPGA 测试负载板设计方案

图中:pogo pin 为ATE 与测试负载板通信连接的桥梁,为被测FPGA提供输入信号和接收输出信号;power B为被测FPGA 的内核电源VCCINT 提供大电流电源,保证FPGA 配置时的瞬态脉冲大电流满足启动要求;power S 为被测FPGA 的其他电源供电。

JTAG 接口主要用于实装测试时的配置比特流下载,通过TDI 一位一位地将比特数据加载到FPGA 的配置存储器中,下载速度较慢。在实际ATE 量产测试中,通过pogo pin,基于Slave SelectMAP 方式完成测试配置,这种方式将待配置的测试向量先存储到ATE 的向量存储模块,测试时直接调用所需的向量名称即可,可同时并行下载32 位比特数据并加载到FPGA 内,配置速率大幅提升,适用于大规模的量产测试需求。

3 仿真与测试验证

3.1 改进的LFSR 与仿真

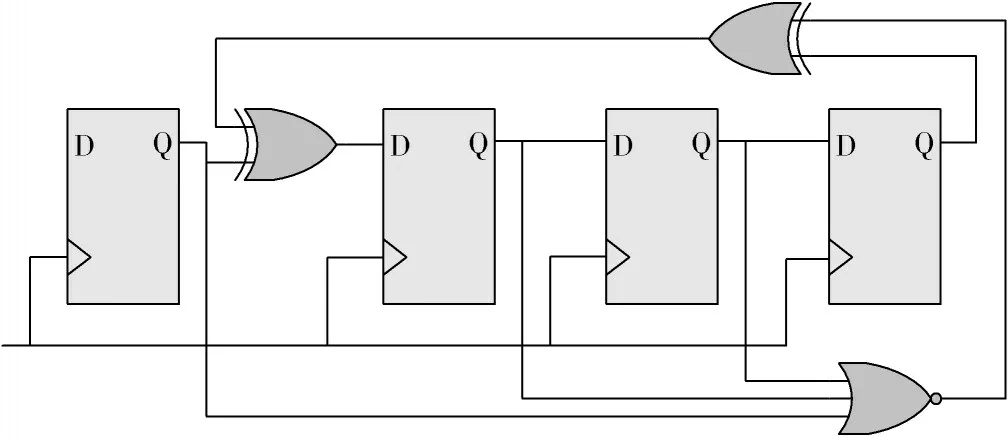

传统的测试向量发生器一般用LFSR 实现,产生的向量具备一定的伪随机性,但无法遍历全0 地址。改进的LFSR 在原有的基础上进行优化,不仅具备伪随机,而且能够覆盖到全0 地址,其结构如图7 所示。

图7 改进的LFSR 结构

经编写Verilog 代码,通过Vivado 2018.3 编译仿真环境得到改进的LFSR 时序仿真结果,如图8 所示。其中:clk 为输入时钟;rst_n 为复位信号;lfsr_dout 为产生的全地址向量。

图8 改进的LSFR 仿真结果

3.2 新型BIST 的LUT 测试仿真

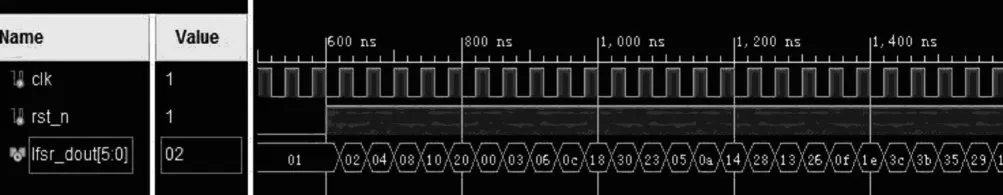

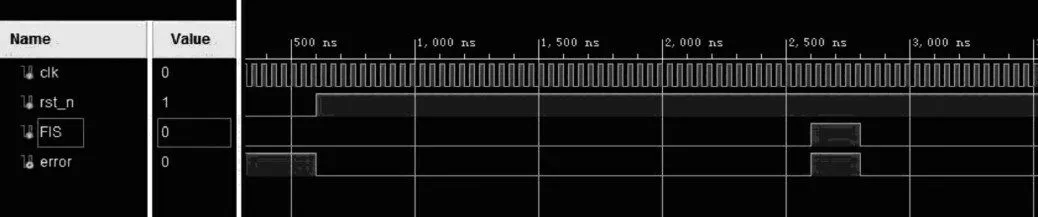

在BIST 电路结构中,改进的LFSR 产生全地址的伪随机测试向量,同时输出到被测模块LUT 和黄金模块LUT,通过比较两者输出否是一致,判断被测LUT 是否存在故障。其中,LUT 是基于Xilinx 原理实现6 输入、1 输出的异或门。测试仿真结果如图9 所示。图中,error 为输出判断结果,除复位状态时error 输出为高电平外,其他状态若输出高电平,则判定被测LUT 存在故障;反之说明被测LUT 功能正常,无故障。

图9 新型BIST 的LUT 测试仿真结果

3.3 测试配置与验证

经过Vivado 软件编译综合生成比特流,利用Slave SelectMAP 模式,基于ATE 将比特流配置向量下载到FPGA 内,并施加相应的响应测试激励,完成FPGA 内LUT 资源覆盖率测试。配置通信原理如图10 所示[16]。

图10 基于Slave SelectMAP 配置原理

图中:M[2:0]为模式选择输入,M[2:0]=3’b110 表示选择Slave SelectMAP 模式;DATA[31:00]为比特流数据,配置的比特文件通过该端口下载至FPGA;CCLK 为专用配置时钟;PROGRAM_B 为专用配置信号,拉低时表示清除配置和初始化;RDWR_B 和CSI_B 均为专用配置信号,RDWR_B 拉低表示测试系统向FPGA 写数据,CSI_B 拉低表示激活Slave SelectMAP 模式;INIT_B 为配置过程指示信号,当PROGRAM_B 拉低清除配置时,INIT_B 输出为低,配置数据开始到结束,INIT_B 一直输出为高;DONE 为配置完成指示信号,当配置数据全部加载完毕,等待几个时钟周期后,DONE 输出高即表示配置完成。此时,测试系统与FPGA 完成握手通信,FPGA 被配置成特定功能的ASIC。

测试系统中,LUT 测试的比特流配置向量和功能向量如图11 和图12 所示。图中,CCLK 和clk 信号为归零码格式,一直发送时钟信号,其他信号均为非归零码格式。比特流配置向量是将FPGA 配置成特定功能,功能向量是完成特定功能验证,测试中rst_n 只有在复位状态时,error 才输出高电平。如图13 所示,实际测试结果与仿真结果完全一致。

图11 比特流配置向量

图12 功能向量

图13 基于BIST 的LUT 测试验证结果

3.4 LUT 的故障注入与诊断

为了进一步验证测试方案的准确性和可靠性,设计一种模拟单粒子翻转的故障注入电路[17⁃18],其结构如图14 所示。

图14 LUT 的故障注入电路

图中的LFSR[5:1]为线性反馈移位寄存器的输出,FIS 为故障注入使能。故障注入的原理为:通过在LUT的任意输入,如I0 端口增加一个故障注入电路,如果使能FIS,则I0 的输入为LFSR[0]输出值取反,实现故障注入;如果不使能FIS,则I0 的输入即为LFSR[0]正常输出值。利用这种方式可以有效地控制故障注入的执行与否,最后基于BIST 测试电路,验证测试方法的准确性。

仿真及验证结果如图15、图16 所示。图中:起始阶段rst_n 复位时,error 输出高;rst_n 拉高后,生成的伪随机测试向量输出到被测LUT 和黄金模块的LUT 中。从图中可以明显看出,当FIS=0 时,被测LUT 未注入故障,功能与黄金模块功能一致,error 输出为低;当FIS=1 时,被测LUT 故障注入成功,功能与黄金模块功能不一致,error 输出为高。同样,经ATE 的测试验证,测试结果与仿真结果一致。

图15 LUT 故障注入及诊断仿真结果

图16 LUT 故障注入及诊断验证结果

综上所述,从仿真到验证,证明了所设计的新型BIST 测试电路对LUT 功能检测的实用性和准确性。

4 结论

本文应用新型BIST 电路完成了FPGA 内部LUT 资源的可测性设计,通过2 次配置设计就能实现LUT 的100%覆盖测试,并基于Xilinx 的一款亿门级FPGA 完成了测试验证。结果表明新型BIST 电路具有良好的测试效益。本文创造性地提出了黄金模块比对思想,只需构造出与被测模块等同的电路,对两者输出进行比较判断即可。此外,优化改进的LFSR 电路结构能够输出全地址的伪随机测试向量,保证了被测LUT 测试图形的全覆盖。相较于其他文献的BIST 可测性设计思路,本文提出的测试方法具有更好的移植性和操作性,可推广应用于FPGA 其他资源的覆盖率测试。