基于FPGA的TANGRAM分组密码算法实现

王建新 许弘可 郑玉崝 肖超恩 张磊 洪睿鹏

摘 要:TANGRAM系列分组密码算法是一种采用比特切片方法,适合多种软硬件平台的系列分组密码算法。针对TANGRAM-128/128算法,使用Verilog HDL对该算法进行FPGA实现并提出设计方案。首先,介绍了TANGRAM密码算法的特点和流程,提出了针对TANGRAM密码算法进行44轮加/解密迭代计算的方案,该方案采取有限状态机的方法有效降低了资源消耗;其次,基于国产高云云源平台,完成了基于高云FPGA的算法工程实现,以及功能仿真和数据的正确性验证,同时在Quartus Ⅱ 13.1.0平台上也进行了相关测试,用以比较。测试结果表明,TANGRAM系列分组密码算法基于Altera公司的Cyclone Ⅳ E系列EP4CE40F29C6芯片进行工程实现,最大时钟频率为138.64 MHz,加/解密速率为403.30 Mbps;基于高云半导体GW2A-55系列芯片的最大时钟频率为96.537 MHz,加/解密速率为280.80 Mbps。

关键词:TANGRAM;分组密码算法;Verilog HDL;有限状态机

中图分类号:TP309.7 文献标志码:A 文章編号:1001-3695(2024)01-041-0260-06

doi:10.19734/j.issn.1001-3695.2023.04.0190

Implementation of TANGRAM block cipher algorithm based on FPGA

Abstract:TANGRAM block cipher algorithm employs a bit-slice approach and is compatible with multiple software and hardware platforms.In response to TANGRAM-128/128 algorithm,this paper proposed a design plan which used Verilog HDL for FPGA implementation.This paper firstly provided an introduction to the characteristics and processed of TANGRAM algorithm and presented a scheme for reducing resource consumption using a finite-state machine for 44 rounds of encryption and decryption computation.Secondly,the engineering implementation of the FPGA algorithm was completed by the domestic Gaoyun platform and subjected to functional simulation and data correctness validation.Furthermore,relevant tests were performed on Quartus Ⅱ 13.1.0 platform for comparison.Test results show that,based on Cyclone IV E EP4CE40F29C6 chip from Altera,TANGRAM block cipher algorithm has a maximum clock frequency of 138.64 MHz and an encryption/decryption speed of 403.30 Mbps.While based on the GW2A-55 chip from Gaoyun,the maximum clock frequency is 96.537 MHz and the encryption/decryption speed is 280.80 Mbps.

Key words:TANGRAM;block cipher algorithm;Verilog HDL;finite-state machine

0 引言

近年来,随着网络信息技术的飞速发展,涉及信息安全的相关问题层出不穷,例如个人隐私信息泄漏,以及重要信息被监听或窜改等。这些问题不仅影响社会秩序,甚至严重威胁国家安全。为解决这些问题,密码已被广泛应用。密码算法可以分为对称密码算法和非对称密码算法两种。分组密码作为现代密码学中的一个重要分支,具有高效和易于实现的特点。目前,代表性的分组密码算法采用三种主要的整体结构,分别为:a)Feistel结构,如数据加密算法DES[1]、Camellia[2]、Blowfish[3]、FEAL[4]等;b)SPN结构,如高级加密标准AES[5]、轻量级分组密码算法SKINNY[6]、韩国加密标准ARIA[7]等;c)Lai-Massey结构,如国际数据加密算法IDEA[8]。

为了推动密码算法的设计和实现技术进步,繁荣我国密码理论和应用研究,促进密码人才成长,中国密码学会于2019年举办了全国密码算法设计竞赛。TANGRAM[9]采用比特切片方法设计出多个软硬件平台可用的系列分组密码。TANGRAM算法结构像七巧板一样,能够适用于多种不同的应用场景,这是其得名的原因。在全国密码算法设计竞赛中,该算法荣获二等奖。为了满足高吞吐量的应用场景需求,本文以TANGRAM-128/128版本为例,基于现场可编程门阵列(field programmable gate array,FPGA),使用硬件描述语言Verilog HDL设计实现。同时,提出一种设计方案,可在Quartus Ⅱ 15.0.1中完成代码的仿真,确保代码的正确性并计算资源占用和吞吐量等性能指标。最终,对其性能进行了测试和对比分析。

1 TANGRAM系列分组密码算法原理

TANGRAM系列分组密码算法共有三个版本,每个版本中的明文分组长度为n bit,密钥长度为m bit,记为TANGRAM-n/m。具体而言,该算法的三个版本分别为TANGRAM-128/128、TANGRAM-128/256、TANGRAM-256/256。表1展示了该算法的具体参数。

在TANGRAM系列分组密码算法中采用了固定的密码函数。加密算法与解密算法的轮密钥使用顺序相反,解密轮密钥即为加密轮密钥的逆序。本文使用的部分符号如表2所示。

1.1 密钥扩展算法

TANGRAM系列分组密码算法的密钥扩展算法按分组长度与密钥长度分为TANGRAM-n/n和TANGRAM-n/2n两种。本文所设计TANGRAM-128/128分组密码算法44轮的轮密钥生成结构如图1所示。

上一轮轮子密钥Ki-1被导入密钥扩展模块以生成下一轮轮子密钥Ki。密钥扩展模块的每一轮轮密钥Ki生成结构分为S盒、4分支广义Feistel变换和轮常数RC[i]异或三部分。

将128 bit的轮子密钥用一个4×32的矩形比特陣列表示:

令Rowi=ki,31…ki,1ki,0表示第i行,i=(0,1,2,3),Rowi可以看作一个32 bit的字。在第r=(0,1,…,43)轮,先提取一个由128 bit组成的轮子密钥Kr=Row3‖Row2‖Row1‖Row0,然后对128 bit的轮子密钥状态进行以下更新:

a)对轮子密钥状态进行S盒操作,即

k′3,j‖k′2,j‖k′1,j‖k′0,j:=

S(k3,j‖k2,j‖k1,j‖k0,j)

j=0,1,…,31(1)

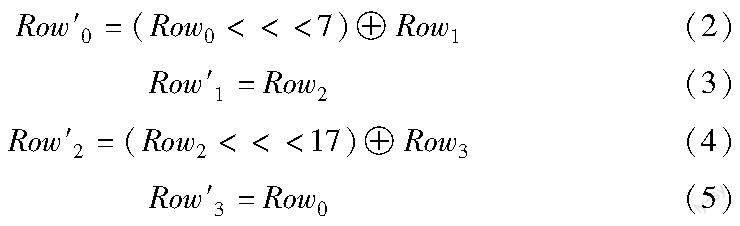

b)进行一轮4分支广义Feistel变换,如下所示:

c)对密钥状态的第一行的6个比特(k0,5 k0,4k0,3k0,2 k0,1k0,0)与每一轮的6 bit轮常数RC[i](i=0,1,…,43)进行异或。

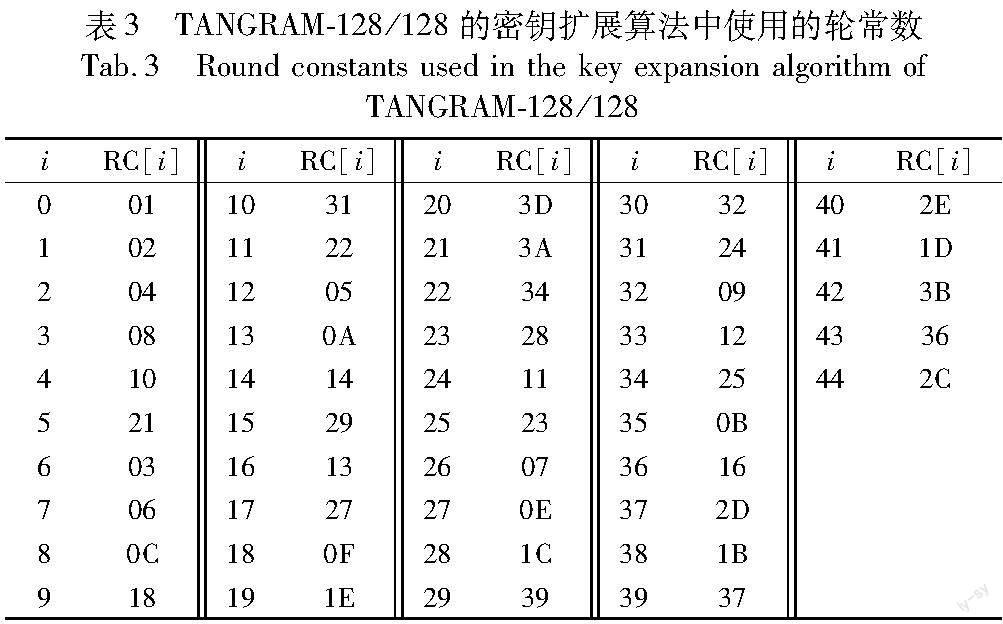

将以上三个步骤的复合变换记为UpadteRC[i][X],其中X为128 bit。在进行了43轮的密钥状态更新后,将更新后的密钥状态的值赋给第44轮的轮子密钥K44。轮常数RC[i](i=0,1,…,43)的具体数值详见表3。

轮常数RC[i]是通过6位线性反馈寄存器生成的。使用rs5、rs4、rs3、rs2、rs1、rs0表示反馈寄存器的状态。在每一轮更新时,将状态左移1位,并将rs0更新为rs5异或rs4的结果,初始值为RC[0]=0x01。

1.2 加/解密算法

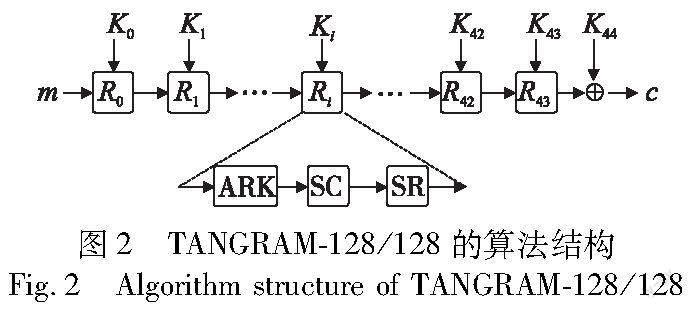

TANGRAM系列分组密码算法采用SP网络结构,总共包含44轮轮加密,每个加密结构算法的最后增加一个子密钥异或操作,无须采用S盒。每一轮变换包含轮密钥加addRoundKey(ARK)、列替换subColumn(SC)和行移位shiftRow(SR)三个步骤。该算法的三个版本均采用相同的轮函数结构。

以TANGRAM-128/128为例,用Ri表示在轮子密钥Ki作用下的轮函数变换的输出数据,m、c分别表示明文和密文,TANGRAM-128/128的算法结构如图2所示。

1.2.1 加密算法

本文主要设计实现TANGRAM-128/128分组密码算法。该算法采用128 bit数据分组长度和128 bit主密钥长度,需要执行44轮(轮函数)迭代运算,加密轮函数结构如图3所示。

加密轮函数的前43轮(轮函数)迭代运算过程中,用4×32的矩阵比特阵列表示每轮输入的128 bit待处理的数据为

针对每一轮128 bit的矩形比特阵列Ri-1进行轮密钥加(addRoundKey)、列替换(subColumn)、行移位(shiftRow),得到该轮轮函数的128 bit输出数据Ri,i表示当前轮次数。在最后一轮,即第44轮(轮函数)迭代运算时,输出的R43与轮密钥K44异或后得到密文c。

a)轮密钥加(addRoundKey)。将128 bit的轮密钥逐比特与128 bit的密码状态异或,如式(6)~(9)所示。设轮密钥为SK3‖SK2‖SK1‖SK0,轮函数输入为I3‖I2‖I1‖I0,两者异或得到的结果记为A3‖A2‖A1‖A0。

b)列替换(subColumn)。对每一列的4 bit进行S盒替换,如式(10)(11)所示。

TANGRAM的S盒是一个4 bit到4 bit的双射S:F42→F42,具体描述如表4所示(用十六进制表示)。

c)行移位(shiftRow)。TANGRAM-128/128对每一行的32 bit做左循环的二次移位。第0行保持固定不动,第1行左循环移动1 bit,第2行左循环移动8 bit,第3行左循环移动11 bit,如式(12)~(15)所示,其中<< 1.2.2 解密算法 TANGRAM系列分组密码算法的解密过程是加密过程的逆过程。解密轮函数包括轮密钥加(addRoundKey)、列替换的逆变换(inverseSubColumn)和行移位的逆变换(inverseShiftRow)三个步骤,具体如图4所示。 由图2可知,TANGRAM-128/128分组密码算法的解密过程与加密过程类似,省略了最后一个线性置换操作。TANGRAM-128/128分组密码算法的解密算法包括以下三个步骤: a)轮密钥加(addRoundKey)。与加密算法中addRoundKey相同。 b)列替换的逆变换(inverseSubColumn)。对每一列的4 bit进行S盒逆变换,过程与加密算法中列替换相同,S盒真值表如表5所示。 c)行移位的逆变换(inverseShiftRow)。对密码状态每一行的32 bit做右循环移位。第0行保持不动,第1行右循环移动1位,第2行右循环移动8位,第3行右循环移动11位。 2 TANGRAM密碼算法硬件设计 FPGA可编程逻辑阵列属于专用集成电路(application specific integrated circuit,ASIC)领域中的一种半定制电路,主要由可编程输入/输出单元、数字时钟管理模块、可配置逻辑块、嵌入式块随机存取存储器(random access memory,RAM)等组成。FPGA具有设计灵活、使用便捷、并行计算、高兼容性等特点。与CPU相比,FPGA并行计算能力可提升运算速率并降低时延;与GPU相比,FPGA在功耗和灵活性等方面具备优势;与ASIC芯片相比,FPGA在项目初期具备短周期、高性价比的优势。FPGA在灵活性、性能、功耗、成本之间具有较好的平衡性,是硬件设计的理想选择。因此,本文采取FPGA实现TANGRAM-128/128分组密码算法。 根据TANGRAM系列分组密码算法原理,本文设计了TANGRAM-128/128分组密码算法的硬件结构[10~12],其包括输入接口模块、控制单元模块、加/解密运算模块、密钥扩展模块以及输出接口模块,如图5所示。主密钥、明文和控制信号通过输入接口模块由外部输入,由控制单元模块选择进行密钥扩展或加/解密运算操作,在进行44轮加/解密运算中使用。最终运算结果由输出接口模块输出。 利用FPGA实现TANGRAM系列分组密码算法的难点在于:a)算法复杂度高,TANGRAM密码算法的加密和解密过程都涉及到多次矩阵运算和非线性变换,因此算法的复杂度比较高;b)存储资源限制,TANGRAM算法需要存储多个S盒、P盒和密钥矩阵等数据结构,本文在使用FPGA实现该算法时考虑在有限的硬件资源下高效地实现TANGRAM分组密码算法是一个难点,本文对算法进行了优化,尽可能地减少硬件资源的使用,以提高硬件效率;c)时序优化,FPGA的时序设计是实现高性能的关键,对于TANGRAM系列分组密码算法,需要优化时序设计以实现更高的运算速度。本文提出了一种有限状态机设计,提高了算法的运行效率。 2.1 有限状态机设计 有限状态机(finite state machine,FSM)是一种由寄存器和组合逻辑构成的硬件时序电路,由一系列数量有限的状态组成的循环机制。相较于纯硬件数字系统顺序方式控制,FSM克服了其不灵活的缺点,根据控制信号预先设定的状态顺序执行。 本文针对TANGRAM-128/128分组密码算法采用有限状态机[13]设计方案,在状态转移图中定义了idle、getReady、getKeyD0、getEnc、getDec、getResult 6个状态。其中idle为空闲状态,getReady为就绪状态。getKeyD0为密钥扩展模块,对输入的种子密钥进行44轮迭代运算,从而产生44个轮子密钥用于加密。具体而言,系统首先进入空闲状态idle,当reset置1时等待数据输入;当接收到数据输入后,只有当start信号置1时系统才会跳转至下一个状态。在就绪状态getReady中,系统对输入端口的数据进行变量赋值。在所有的变量赋值完成之后,当op=00时,系统进入密钥扩展状态getKeyD0,在该状态下系统会对所输入的种子密钥进行44轮密钥扩展,产生44个轮子密钥。在这个状态中,每轮变换都有赋值和计数的操作。产生的密钥存入一个位宽为128 bit的寄存器数组中。当计数标志位over值置1时开始计数,以轮数44作为状态切换标志,待所有的轮次加/解密完成后,切换至下一个状态进行输出。当op值不为00时,进入加密(getEnc)/解密(getDec)状态,此状态进行44轮的加密或解密。在每轮加/解密中,系统调用负责加/解密的函数,并将每轮的输出作为下一轮的输入,同时也进行计数操作。当计数标志位over置1时开始计数,以轮数44作为状态切换标志,待所有的轮次加/解密完成后切换至下一状态进行输出。在44轮加密完成后,系统进行一步异或操作,将最后一个轮密钥K44作为异或对象,该轮密钥由K43按照相同的密钥扩展方式产生;而在解密算法中,44轮解密完成之后也要进行一步额外的异或操作,将初始密钥K0作为异或对象。状态转换图如图6所示。 根据TANGRAM系列分组密码算法的基本原理可知,每当进行一轮加/解密运算,都需要扩展密钥以生成下一轮所需的轮密钥,并将其输出至对应轮数的加/解密运算中,以生成下一轮的轮数据。通过不断循环迭代该过程,最终输出密文/明文。本文TANGRAM-128/128有限状态机方案则优先利用密钥扩展模块生成全部的轮密钥,将44个轮密钥分别存储在对应的寄存器Ki中。在进行加/解密运算时,根据当前迭代的轮数i调用相应寄存器Ki完成迭代运算并输出密文/明文。该设计方案节省了生成每轮轮密钥所需的密钥扩展时间,大大提高了算法的运行效率。 2.2 密钥扩展模块设计 本文提出的TANGRAM-128/128有限状态机密钥扩展模块如图7所示,将128 bit的初始密钥K0输入进行第1轮密钥生成操作,将第1轮产生的128 bit轮密钥输出到下一轮进行下一轮的轮密钥操作。每轮产生的新128 bit轮密钥数据被存储在寄存器Ki中,以供下一轮运算调用。该密钥扩展过程共计进行44轮循环迭代运算。 2.3 输入/输出端口模块设计 本文TANGRAM-128/128有限状态机方案使用了389个接口。输入输出接口模块的结构[13~16]如图8所示。 设计方案的输入/输出接口模块包括一个1 bit时钟输入(clock)端口、三个1 bit判断位输入(reset、start、op)端口、一个128 bit密钥输入(kin)端口、一个128 bit明文/密文输入(datain)端口、一个128 bit密/明文输出(encout)端口以及一个1 bit判断位输出(over)端口,外部端口信号说明如表6所示。 3 仿真验证与性能分析 本文选用ModelSim 13.1.0作为TANGRAM-128/128有限状态机设计方案的功能仿真验证工具,并采用Altera公司的Quartus Ⅱ 13.1.0作为开发平台,使用Cyclone Ⅳ E系列的EP4CE40F29C6芯片进行综合测试。 3.1 功能仿真验证 算法由多个模块组成,各模块功能的正确性对系统输出结果至关重要。本文选取了两个模块进行仿真验证,并对整个算法进行仿真验证。 1)循环移位模块 针对循环左移11位模块进行仿真验证,结果如图9所示。 由图可知,输入前11位全1后21位全0数据,得到结果为前11位全0,11~21位全1,22~33位全0数据,由此可验证此模块结果正确。 2)S盒模块 将32 bit的测试数据输入S盒模块进行验证,结果如图10所示。 由图可知,S盒置换结果与表4中的值一致,由此可以验证此模块结果正确。 3.2 加/解密仿真 对于TANGRAM-128/128有限状态机的设计方案进行了功能仿真验证。在Quartus Ⅱ 15.0.1平台选用Cyclone Ⅳ E系列的EP4CE40F29C6芯片进行仿真,并使用了多组测试向量进行了验证,其中一组测试向量在加/解密的过程中得到的结果如图11、12所示。 由仿真结果可知,op置01表示加密状态,reset置0表示算法程序正常工作,从使能端start接收到置为1的信号开始,标志位over开始置为1,这个过程为密钥扩展过程,共264 ns,时钟约束为6 ns,故而总计44个时钟,从标志位over置01开始到其置10,此过程为加密过程,从264~528 ns,时钟约束为6 ns,故总计44个时钟,具体输入和输出如下所示。 明文:00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 密钥:00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 密文:DF C4 4F 95 98 0B 05 94 E4 88 98 1A CB F7 70 6B 由仿真结果可知,时钟频率为3 ns,op置10表示解密状态,reset置0表示算法程序正常工作,从使能端start接收到置为1的信號开始,密钥扩展过程总共需要44个时钟,解密过程总共需要44个时钟,具体输入和输出如下所示。 密文:DF C4 4F 95 98 0B 05 94 E4 88 98 1A CB F7 70 6B 密钥:00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 明文:00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 3.3 算法性能分析 在Altera公司的Quartus Ⅱ 15.0.1软件环境下,选择使用Cyclone Ⅳ E系列EP4CE40F29C6芯片进行综合测试。TANGRAM-128/128有限状态机方案的主要逻辑资源的消耗情况如表7所示。 在完成Quartus Ⅱ 13.1.0综合编译时序分析后,在Timing Analyer报告中得出TANGRAM-128/128有限状态机方案的最大工作频率为138.24 MHz,如图13所示。 在高云云源环境下选用GW2A-55系列芯片进行验证,其资源占用数和时钟频率的值如图14、15所示。 根据上述数据可以推断出,高云半导体的GW2A-55系列芯片性能与Cyclone ⅣE系列芯片差距不大。但是,高云开发的芯片仍以中低端FPGA为主,其性能与国外高端系列芯片相比仍有较大差距。上表还列出了Intel公司两款Stratix系列芯片Stratix Ⅲ(EP3SE50F780C2)和Stratix Ⅴ的仿真结果和性能指标。图16~19分别为Stratix Ⅲ、Stratix Ⅴ两款芯片的资源占用情况和最大时钟频率。 根据所得到的最大时钟频率,结合时钟数以及分组长度,可以计算出各自的吞吐率,具体性能指标如表8所示。 由以上数据可得,在资源占用相近的情况下,Cyclone Ⅳ E、Stratix Ⅲ以及Stratix V这三款芯片的吞吐量分别为403.32 Mbps、660.10 Mbps、870.20 Mbps,而国产高云GW2A-55系列芯片的吞吐量仅有280.84 Mbps。因此可以得出结论,国产高云GW2A-55系列芯片吞吐速度远低于其他三款芯片,而Stratix系列芯片已经研发至Stratix Ⅹ。由此可见,国产FPGA在高端芯片领域发展仍较为滞后,尚需大力研发,进一步优化和改进其性能。 4 结束语 本文研究了TANGRAM系列分组密码算法的FPGA设计与实现方法。对于TANGRAM-128/128版本,采用有限状态机的设计方案,从算法层面降低了硬件逻辑资源的占用,同时提高了算法的运行效率。实验结果显示,在Altera公司的Quartus Ⅱ 15.0.1软件环境下,采用Cyclone ⅣE系列的EP4CE40F29C6芯片进行综合测试,TANGRAM-128/128有限状态机方案最大工作频率可达138.24 MHz,吞吐率为0.38 Gbps。在高云云源环境下,选用GW2A-55系列芯片进行验证,其最大工作频率提高至96.54 MHz,吞吐率达到280.84 Mbps。 张文涛等人[9]提出了ASIC硬件实现TANGRAM算法的方案,该方案使用了UMC 130 nm和Nangate 45 nm两个常见的工艺库来评估ASIC硬件实现。该方案针对ECB模式准备了三个版本的硬件实现,并采用多种优化方式实现TANGRAM的ECB模式。最后,针对不同应用场景,该方案对硬件实现进行优化,包括低面积实现、高吞吐量和低延迟的相关应用。实验结果表明,TANGRAM算法是一个高度灵活的、硬件实现友好型的分组密码。文献[9]是ASIC设计,本文是基于FPGA设计,无法进行方案对比。 在对多款FPGA芯片进行性能分析得出,国产高云芯片的性能仍有待提高,相较于美国芯片还存在差距,因此需要继续努力从综合、布局布线、制造工艺等方面提高性能。未来工作可以进一步优化TANGRAM-128/128有限状态机方案,提高其最大工作频率,尝试降低逻辑资源的占用,最终在工作频率与资源占用之间找出最优方案。 参考文献: [1]National Institute of Standards and Technology.Data encryption stan-dard,FIPS 46-3[S].[S.l.]:Federal Information Processing Stan-dards Publication,1999. [2]Aoki K,Ichikawa T,Kanda M,et al.Camellia:a 128-bit block cipher suitable for multiple platforms-design and analysis[C]//Proc of the 7th Annual International Workshop on Selected Areas in Cryptography.Berlin:Springer-Verlag,2000:39-56. [3]Karthigai K P,Baskaran K.An ASIC implementation of low power and high throughput blowfish crypto algorithm[J].Microelectronics Journal,2010,41(6):347-355. [4]Shimizu A,Miyaguchi S.Fast data encipherment algorithm FEAL[C]//Proc of the 6th Annual International Conference on Theory and Application of Cryptographic Techniques.Berlin:Springer-Verlag,1987:267-278. [5]Heron S.Encryption:advanced encryption standard(AES)[J].Network Security,2009,2009(12):8-12. [6]Beierle C,Jean J,Klbl S,et al.The SKINNY family of block ciphers and its low-latency variant MANTI[M]//Robshaw M,Katz J.Advances in Cryptology.Berlin:Springer,2016:123-153. [7]Kwon D,Kim J,Park S,et al.New block cipher:ARIA[M]// Lim J I,Lee D H.Information Security and Cryptology.Berlin:Springer,2003:432-445. [8]Lai Xuejia,Massey J L.A proposal for a new block encryption stan-dard[M]//Damgard I B.Advances in Cryptology.Berlin:Springer,1991:389-404. [9]張文涛,季福磊,丁天佑,等.TANGRAM:一个基于比特切片的适合多平台的分组密码[J].密码学报,2019,6(6):727-747.(Zhang Wentao,Ji Fulei,Ding Tianyou,et al.TANGRAM:a bit-slicing-based packet cipher for multiple platform[J].Journal of Cryptology,2019,6(6):727-747.) [10]何诗洋,李晖,李凤华.SM4算法的FPGA优化实现方法[J].西安电子科技大学学报,2021,48(3):155-162.(He Shiyang,Li Hui,Li Fenghua.FPGA optimization of SM4 algorithm implementation method[J].Journal of Xian University of Electronic Science and Technology,2021,48(3):155-162.) [11]刘金峒,梁科,王锦,等.SM4加密算法可裁剪式结构设计与硬件实现[J].南开大学学报:自然科学版,2019,52(4):41-45.(Liu Jindong,Liang Ke,Wang Jin,et al.SM4 encryption algorithm cuttable structure design and hardware implementation[J].Journal of Nankai University:Natural Science Edition,2019,52(4):41-45.) [12]王晨光,乔树山,黑勇.分组密码算法SM4的低复杂度实现[J].计算机工程,2013,39(7):177-180.(Wang Chenguang,Qiao Shushan,Hei Yong.Low-complexity implementation of the grouped cipher algorithm SM4[J].Computer Engineering,2013,39(7):177-180.) [13]王建新,周世强,肖超恩,等.基于FPGA的FESH分组密码算法高速实现[J].信息网络安全,2021,21(1):57-64.(Wang Jian-xin,Zhou Shiqiang,Xiao Chaoen,et al.High-speed implementation of FPGA-based FESH packet cipher algorithm[J].Information Network Security,2021,21(1):57-64.) [14]孟祥兴,曹欣.NBC分组密码算法的FPGA高速实现[J].南京工程学院学报:自然科学版,2021,19(3):75-79.(Meng Xiangxing,Cao Xin.High-speed FPGA implementation of NBC packet cipher algorithm[J].Journal of Nanjing Engineering College:Natural Science Edition,2021,19(3):75-79.) [15]张利华,吴松,蒋腾飞,等.基于FPGA的SMS4算法实现及在线验证[J].华东交通大学学报,2018,35(5):111-116.(Zhang Lihua,Wu Song,Jiang Tengfei,et al.FPGA-based SMS4 algorithm implementation and online verification[J].Journal of East China Jiaotong University,2018,35(5):111-116.) [16]王建新,刘芮安,肖超恩,等.ANT系列分组密码算法的FPGA高速实现[J].电子技术应用,2021,47(4):132-136,144.(Wang Jianxin,Liu Ruian,Xiao Chaoen,et al.High-speed FPGA implementation of ANT series packet cipher algorithm[J].Electronic Technology Applications,2021,47(4):132-136,144.)