SiGe电光调制器研究进展

王 迪,冯 松,陈梦林,刘 勇,胡祥建,冯露露

(西安工程大学 理学院,陕西 西安 710048)

硅光子学具有低成本、低功耗以及与CMOS(Complementary Metal Oxide Semiconductor)兼容等优点[1-2]。在光互连系统中,光调制是较重要的环节,可以实现较高的调制速率[3-4]。

电吸收是一种调制光的技术,通常具有较低的驱动电压。其采用弗朗兹-凯尔迪什(Franz Keldysh,FK)效应或量子限制斯塔克效应(Quantum Confinement Stack Effect,QCSE)调节带隙能量[5],进而调节吸收系数,并采用III-V族直接带隙半导体,被广泛应用于长途和中距离电信网络。对于传统硅材料制成的调制器,由于硅材料没有一阶电光效应,且高阶电光效应微弱,导致其调制速率不佳,因此采用硅材料制成的调制器都是基于等离子色散效应[6]。等离子色散效应指在外加电场的作用下,使有源区的自由载流子浓度发生改变,进而改变输出光波的相位和幅值,从而实现电光调制[7]。由于受到载流子本身寿命的限制,调制器的速度并不高,因此,采用其他材料或结构制成调制器的研究具有重要意义。增大外加偏置电压以达到提高调制区载流子浓度的方法导致调制器具有额外功耗,不利于光电集成。为了减小功耗,可利用SiGe电光调制器作为一个关键构建模块。本文基于SiGe材料对硅基光子调制器的研究现状进行了讨论,并对相关调制器的调制速率、损耗等参数进行了对比和分析,为研发高速率、低损耗的光子调制器提供了思路。

1 基于PIN结构的调制器

目前,采用传统硅材料制成的调制器的调制速率已达到50 Gbit·s-1,但较难进一步提高调制速率。与Si材料相比,SiGe材料具有更高的载流子迁移率,且材料本身具有较强的电吸收(Electro Absorp-tion,EA)效应,利用FK效应或QCSE效应制备的SiGe调制器可工作在吸收边界波长处具有调制带宽大、调制效率高、消光比高以及插入损耗低等优点,是一种制作高速率器件的理想材料。

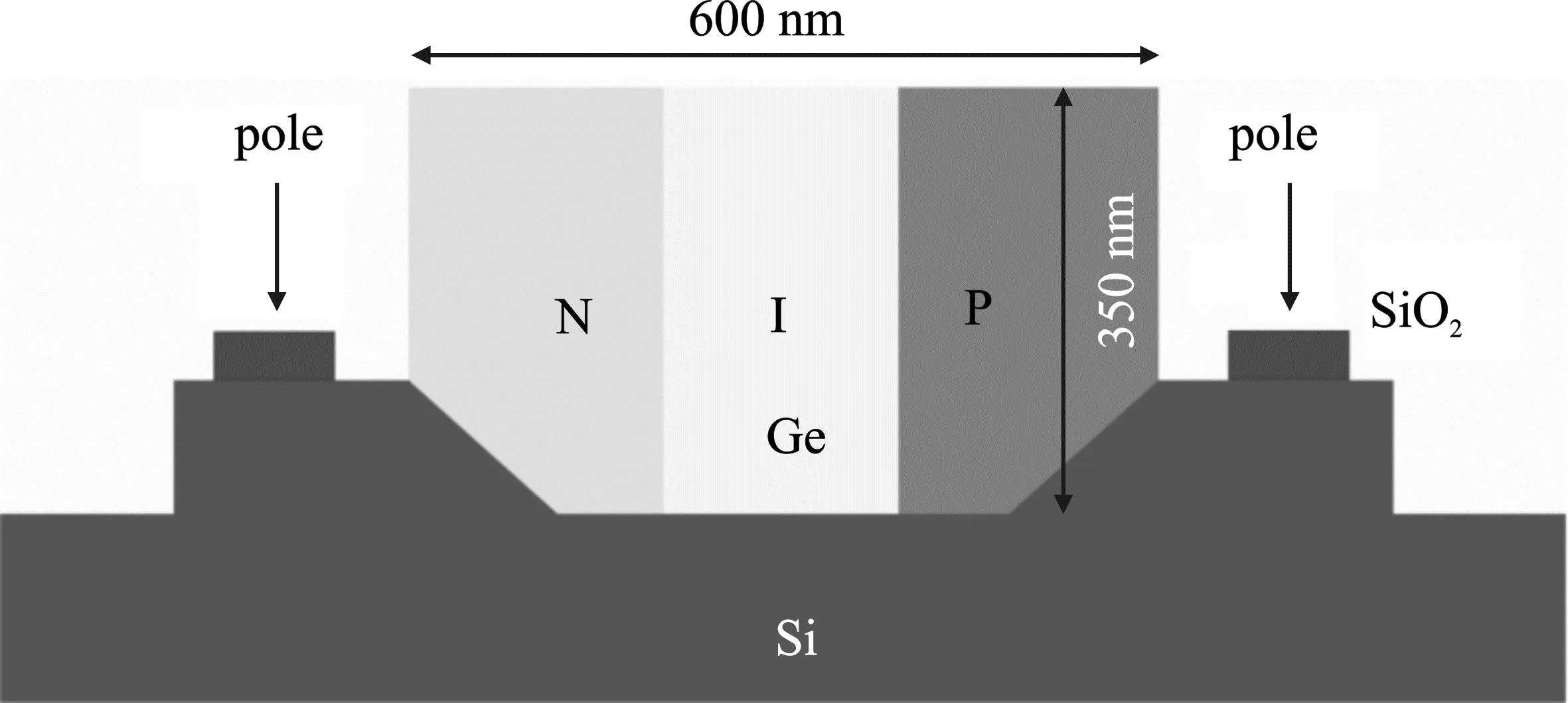

文献[8]演示了一种具有水平PIN结构的SiGe电吸收调制器。该器件在波长为1 550 nm处的消光比为6 dB,具有5 dB的插入损耗。其主要损耗是SiGe材料对载流子的吸收损耗以及Si波导和SiGe波导之间的模式失配损耗。SiGe FK调制器的横截面如图1所示。当光从脊SOI波导传播到FK调制器区域时,光被有源SiGe区域吸收,吸收的量取决于在PIN结上施加的电压。横向PIN结构使SiGe区域较狭窄,减少了实现高消光比所需的电压。通过降低SiGe波导宽度和优化侧壁掺杂轮廓,SiGe FK调制器可以在小于2 V驱动电压下工作。

图1 SiGe EA调制器截面Figure 1. SiGe EA modulator section

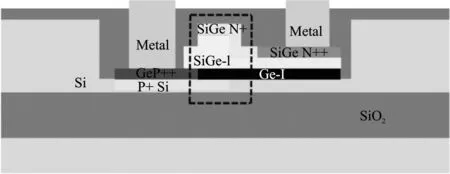

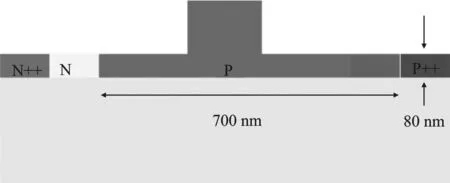

文献[9]演示了一种基于FK效应的Ge/SiGe调制器。该调制器采用水平PIN结构,并集成在具有3 μm厚的SOI平台上,该调制器结构截面如图2所示。通过实验验证该调制器的3 dB带宽为38 GHz,尺寸为0.8 μm×50 μm。该调制器具有尺寸小、性能高等优点,为高速通信应用提供了低成本、低功耗的解决方案。

图2 SiGe FK 调制器截面Figure 2. SiGe FK modulator section

文献[10]演示了低温表面钝化对载流子注入SiGe电光调制器的影响。由于硅和钝化层之间存在界面陷阱,表面复合降低了PIN调制器的调制效率。对于横向PIN SiGe调制器,可以通过引入应变SiGe层来增强等离子体色散效应。调制器的截面如图3所示,当载流子在正向偏置电压下从P区和N区注入到波导区时,注入的载流子被界面陷阱捕获,并在Si表面复合,降低了波导区的载流子浓度[11]。热生长二氧化硅层是钝化硅表面的最佳解决方案之一,但需要900 ℃以上的高温氧化过程,从而导致应变SiGe的应变弛豫。与化学气相沉积(Chemical Vapor Deposition,PECVD)二氧化硅钝化相比,原子层沉积(Atomic Layer Deposition,ALD)在200 ℃下形成的氧化铝钝化可以有效减少低温下Si表面的界面陷阱。氧化铝钝化Si表面的界面密度小于2×1011cm-2eV-2,比化学气相沉积SiO2钝化表面低一个数量级。通过在SiO2沉积前引入氧化铝钝化层可以提高调制器的调制效率,当调制器具有20 dB的衰减时,注入载流子浓度提高了约40%,这与热生长的SiO2钝化器件相同。因此,在原子层沉积下Al2O3可能在低温下对应变SiGe调制器进行钝化。

图3 SiGe 电光调制器截面Figure 3. SiGe electro-optic modulator section

文献[12]提出采用与Ge波导电吸收调制器类似的横向PIN二极管设计,演示了一种调制速率为50 Gbit·s-1的SiGe波导电吸收调制器[13],其截面如图4所示。该调制器宽0.6 μm,长40 μm,集成在220 nm的SOI波导上。仿真结果表明,在2 V的驱动电压下,直流消光比为4.2±0.3 dB,插入损耗为4.4±0.6 dB,功率损耗为8.5 dB。3 dB带宽大于50 GHz,在-1 V偏置电压下,结电容为13.8 fF,SiGe 电吸收调制器在室温下的最佳工作波长为1 560 nm。在调制速率为50 Gbit·s-1时,在1 560 nm、2 V条件下,该调制器的动态消光比为3.0 dB。

图4 Ge波导电吸收调制器截面Figure 4. Section of Ge wave conductive absorption modulator

文献[14]提出了一种Si/SiGe/Si双异质结的PIN电学调制结构。在波导区采用了SiGe材料,形成双异质结PIN结构。波导结构参数为:波导宽度W为450 nm,内脊高H为220 nm,平板高h为50 nm,有源区N+、P+掺杂浓度为1e×1019cm-3,I区掺杂浓度为1e×1015cm-3,Ge含量为0.2。其结构如图5所示,通过SOI以及SOI SiGe-OI两种结构对比,通过仿真分析电压和注入载流子浓度的关系,Si/SiGe/Si双异质结PIN调制器可以在更小的调制电压下获得更高的载流子注入效率,进一步降低了调制功耗。

图5 Si/SiGe/Si双异质结调制器截面Figure 5. Si/SiGe/Si double heterojunction modulator section

文献[15]提出了一种具有低功耗的Si/SiGe异质结电吸收调制器。调制器采用了一种环绕式PIN结构,其结构如图6所示。在一个1.5 μm宽的脊波导上集成了一个二极管,P掺杂为一个100 nm厚的硅层,包括底部的Ge层和SiGe区域,其中N掺杂(厚度为100 nm)为沿着脊波导顶部的部分。该结构通过环绕式二极管结构,能更好地控制结的宽度,降低与波导宽度间的相互约束。SiGe波导和Si波导之间的耦合方案实现了两种材料之间波导的自对准,简化了制造过程。在56.2 Gbit·s-1的调制速率下测量得到器件的动态消光比为5.2 dB,调制功率为44 fJ·bit-1。采用该结构,电场强度不会受到波导宽度的限制,还可以根据需要进行调整以改善光偏振和光传播。

图6 Si/SiGe异质结电吸收调制器Figure 6. Si/SiGe/Si heterojunction electro absorption modulator

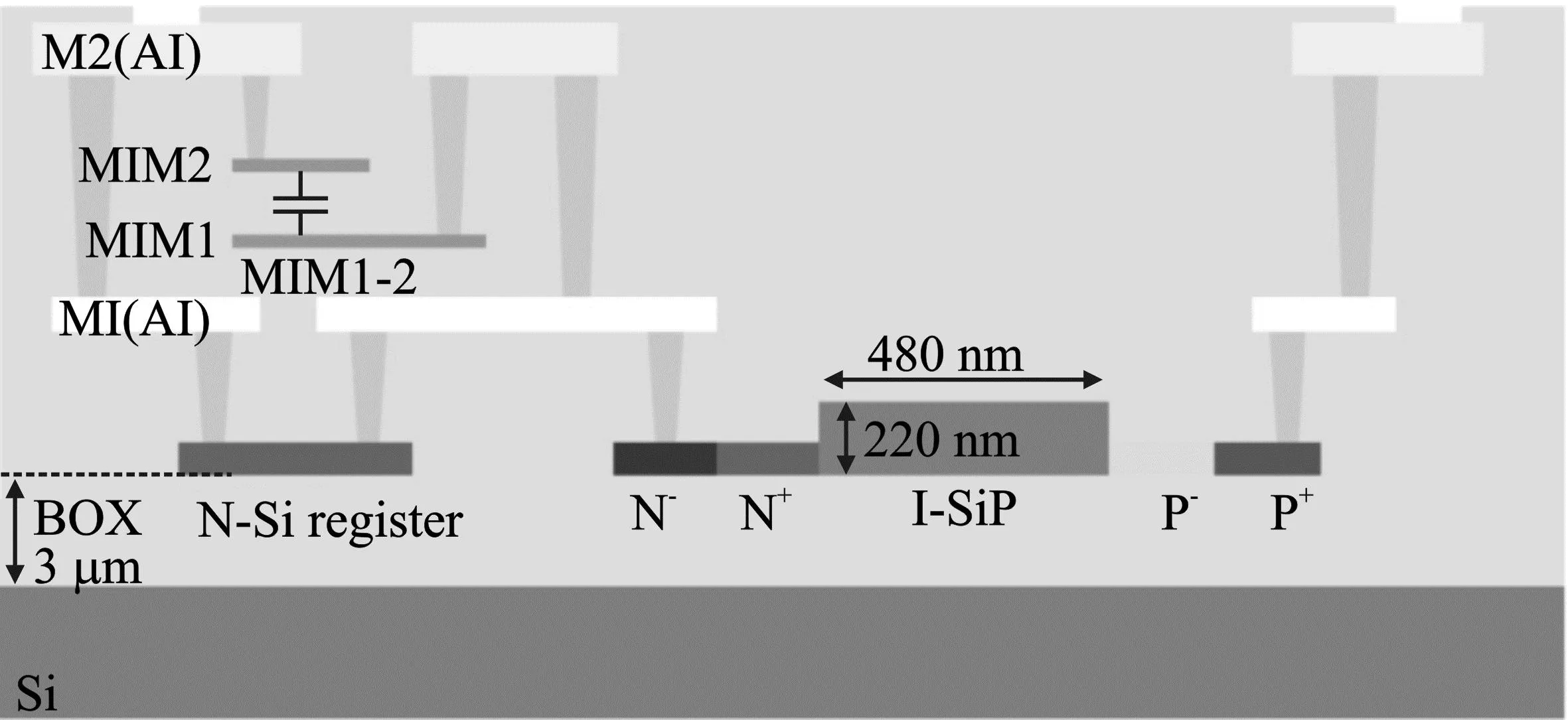

文献[16]提出了一种基于带无源RC均衡器(PIN-RC)的正向偏置PIN结构的Si MZ调制器。通过将无源RC均衡器与PIN移相器集成,可以在保持高调制效率的同时提高调制器带宽。图7为Si MZ调制器截面。非对称的掺杂脊波导Si MZ调制器由220 nm厚的Si层和3 μm厚的埋氧层组成,正向偏置的PIN移相器在480 nm×220 nm的波导芯层内具有一个未掺杂的本征区。研究表明,由于输出阻抗(Rdrv=50 Ω)限制,调制器的3 dB带宽为35.0~37.5 GHz,调制效率为2 V·cm。在CMOS逆变器与PIN-RC调制器结合的情况下,由于CMOS逆变器的输出阻抗较小,可以显著提高器件的调制效率。

图7 Si MZ调制器截面Figure 7. Si MZ modulator section

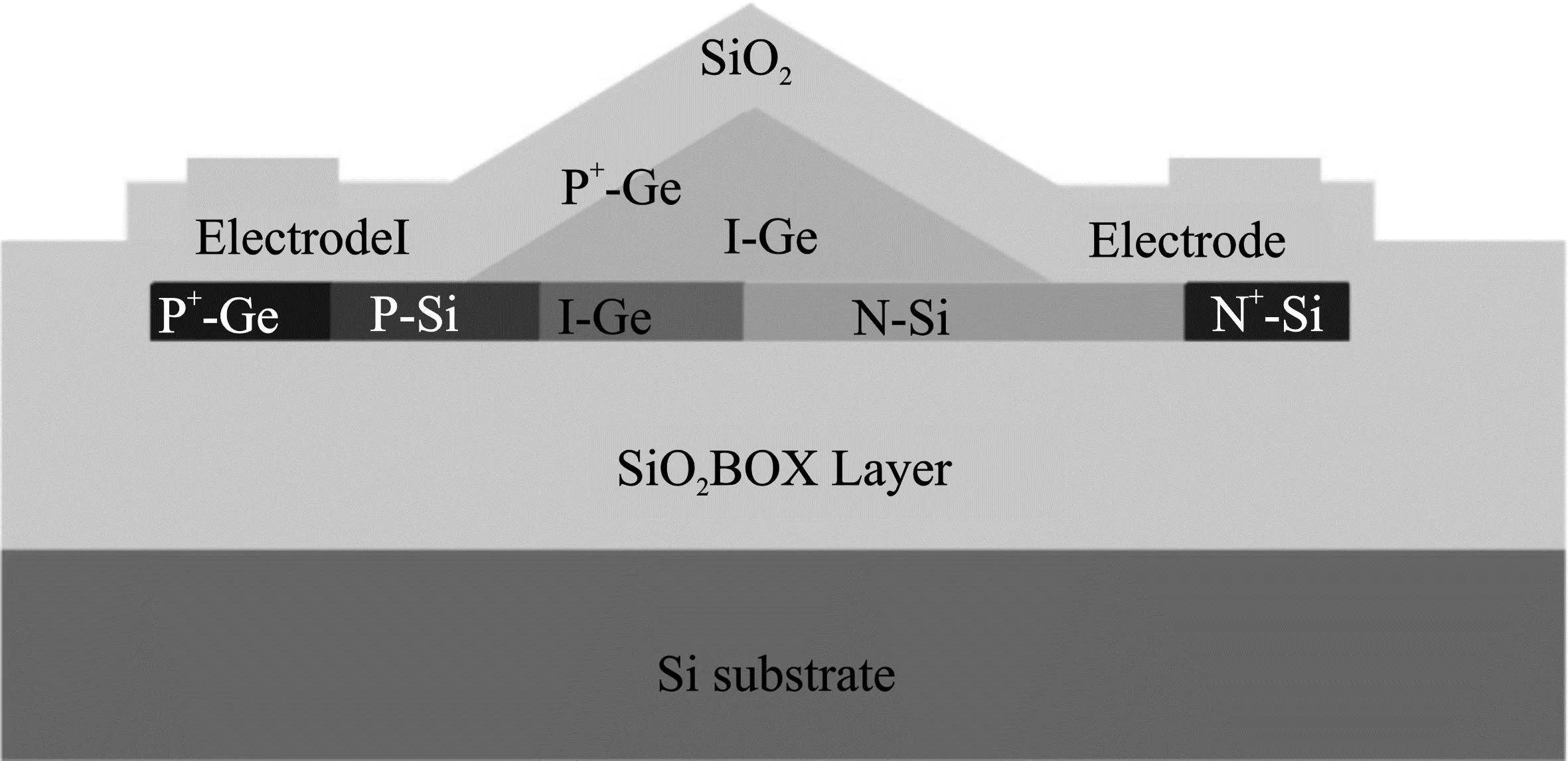

文献[17]提出了一种新型高效耦合Ge波导EA调制器。当光输入到Si平板区时,通过三维Ge波导迅速耦合进/出EA调制器,该结构也可用于制备锗光电探测器[18]。图8显示了Ge EA调制器的横截面形状和掺杂。P-Si、P-Si、I-Si、N-Si和N-Si被定义在SOI的顶部Si层中。锗的一侧与P-Si接触,锗的另一侧在N-Si上。顶部的Ge采用P型掺杂,与P-Si相邻,非对称PIN结由P-Ge、I-Ge和N-Si构成。基于FK效应,Ge/SiGe电吸收调制器在硅上选择性地生长了Ge波导,采用非对称的PIN结来改变Ge波导的电场强度。在1 610 nm波长处,当驱动电压为3 V时,插入损耗和直流消光比分别为6.2 dB和3.6 dB,当电压为-1 V时,3 dB带宽约为36 GHz,当调制速率为56 Gbit·s-1时,动态消光比为2.7 dB。

图8 Ge波电吸收调制器截面Figure 8. Ge section of wave electric absorption modulator

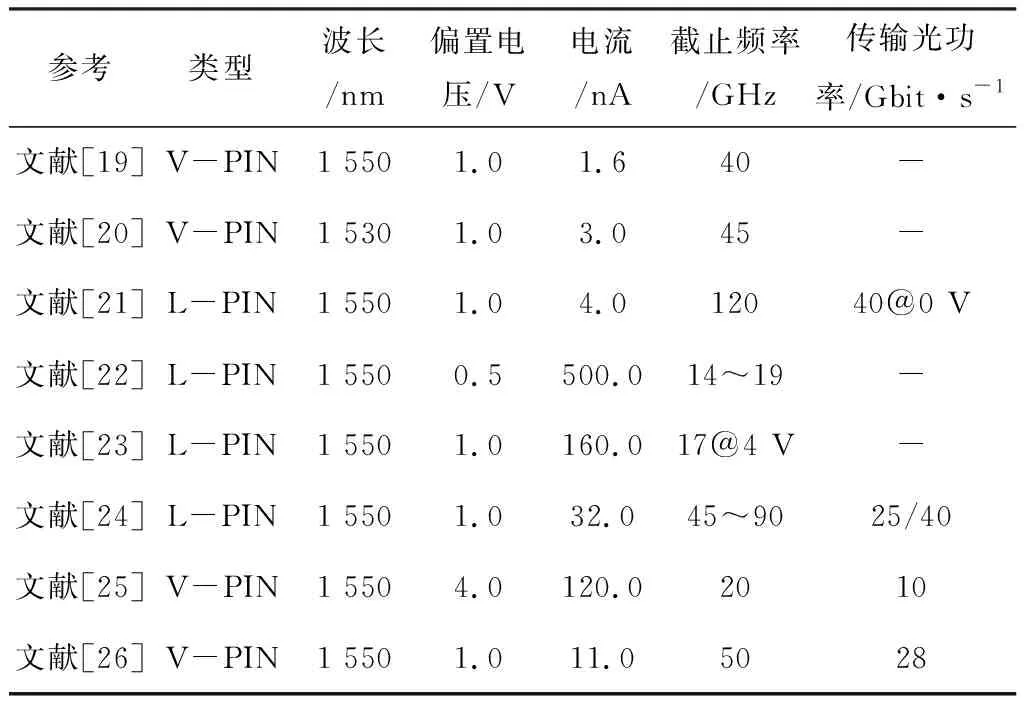

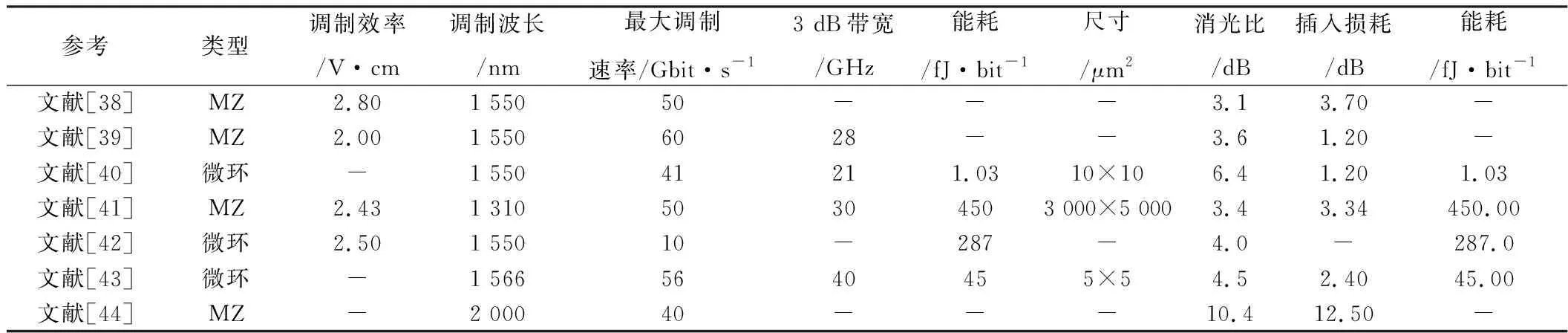

为了对SOI材料调制器进行对比,表1列出了基于不同调制结构的SOI光子调制器的性能参数。由表1可知,工作在1 550 nm波长下的水平PIN和垂直PIN结构在相同偏置电压下,垂直PIN结构的电流相比水平PIN结构电流较小。在1 530 nm波长下的垂直PIN结构截止频率较高。在1 550 nm波长下,电压越高,截止频率越低,传输光功率越低。

表1 工作在通信波长下锗硅PIN电光调制器Table 1. SiGe PIN electro-optic modulator operating at communication waveleng

本文所提PIN结构包括水平PIN和垂直PIN结构,通过控制变量法改变P区和N区的掺杂浓度、外加电压、波导宽度以及波导材料等。例如I区采用应变SiGe材料,通过控制掺杂Ge的含量,分析对比Ge含量对调制器的影响。图2~图5以及图7和图8采用水平PIN结构。文献[14]通过ISE-TCAD进行仿真得到Ge含量为0.2,此时调制器性能最佳。文献[15]采用环绕式二极管结构,能够更好地控制结的宽度,降低与波导宽度之间的相互约束。文献[14]采用PIN结构的调制器,利用FK效应或QCSE效应可以使其工作在吸收边界波长处,具有调制带宽大、调制效率高、消光比高以及插入损耗低等优点。

2 基于PN结构的调制器

文献[27]演示了一种高速调制器,该器件在130 nm厚的SOI 晶片上制备。该器件采用微环结构,微环半径为7.5 μm。图9为环形波导的横截面,其中波导宽度为380 nm,刻蚀深度为220 nm,Si平板厚为80 nm,以此实现单模单偏传输[28]。除了环型波导的尺寸外,另一个重要的设计是PN结的掺杂。理想的光波导掺杂垂直均匀,同时远离PN结的位置,其目标是实现小电容、小电阻、低光损耗,同时实现更好的相位调制。实验证明该调制器具有25 Gbit·s-1的调制速率,消光比大于5 dB,在驱动电压为1 V时,调制功率为7 fJ·bit-1。

图9 Si微环调制器截面Figure 9. Micro ring modulator section

文献[29]演示了一种基于交错PN结高速硅微环调制器。图10为交PN结调制器的截面图,掺杂轮廓和光学结构设计并与标准0.18 μm CMOS工艺兼容,具有较高的调制效率。由于级联交错PN结,导致载流子耗尽区与光模场的重叠面积增大,提高了器件的调制效率。当掺杂浓度为2×1017cm-3时,器件的调制效率为1.24 V·cm,损耗为12.6 dB·cm-1,3 dB带宽为11.8 GHz。所设计的器件具有较大公差,在±150 nm的误差下,调制效率仅降低了12.4%。实验证明,当调制器在2 V、20 V和25 Gbit·s-1的PRBS数据驱动条件下,可以实现6.2 dB和4.5 dB的消光比。通过在MZ或微环调制器中使用交错PN结构可实现超过40 Gbit·s-1的调制速率。

图10 交错PN结调制器截面Figure 10. Staggered PN junction modulator section

文献[30]提出了基于反偏PN结中的载流子损耗机制,设计了一种调制速率为40 Gbit·s-1的硅微环调制器,并对工作波长进行了优化,以此缓解由于光子寿命引起的带宽限制。图11为调制器截面,具有锯齿形PN结构,调制效率为1.7 V·cm,3 dB截止带宽为51 GHz。当外加电压为3 V时,可以实现20 Gbit·s-1和44 Gbit·s-1的高速调制,消光比分别为3.45 dB和3.01 dB。实验结果证明,所设计的调制器在光互连技术中具有较大的应用潜力。

图11 波状PN结调制器截面Figure 11. Corrugated PN junction modulator section

文献[31]演示了一种硅马赫-曾德尔(MZ)光调制器。实验证明,该调制器具有50.1 Gbit·s-1的调制速率和5.56 dB的动态消光比。图12为MZ硅光调制器原理,移相器由4 mm长的反向偏置PN结组成,在Vbias=-6.0 V下,光传输损耗为1.0 dB·mm-1,调制效率为26.7 V·mm。文献[32]提出了一种集成在SOI平台上的PN结硅行波MZ调制器,该器件具有50 Gbit·s-1的调制速率。在2 V驱动电压下,器件实现了800 fJ·bit-1调制功率。通过补偿掺杂和行波电极两种方法可以进一步优化反向PN结MZ硅光调制器的损耗和开关速度。

图12 Si MZI调制器截面Figure 12. Si MZI modulator section

文献[33]在脊型PN结的顶部加入应变SiGe层,设计了一个最优的Si调制器。图13为Si调制器的横截,其中波导高度为220 nm,波导宽度为0.4 μm,波导区顶部P型Si60Ge40的厚度为20 nm。实验证明,当波长为1.3 μm时,在-0.5 V和-2 V反偏电压下,器件的调制效率分别为0.67 V·cm和0.81 V·cm。

图13 具有应变SiGe层Si调制器Figure 13. Si modulator with strained SiGe layer

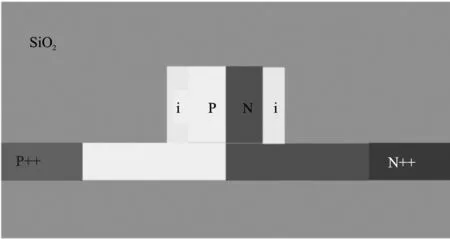

文献[34~35]提出一种低压双驱动硅MZI调制器,由级联PN和PIN结组成。图14为移相器的横截面,波导宽度425 nm,平板高度90 nm,P区和N区的掺杂浓度分别为5e×1017cm-3和3e×1017cm-3。重掺杂区域P++和N++区域放置在距离脊波导边缘700 nm处,以达到减少光吸收损耗的目的,提高响应频率。在合成46 Gbit·s-1PAM4时,功耗约为611 fJ·bit-1,3 dB带宽高达27 GHz。对于20 Gbit·s-1和40 Gbit·s-1的PAM4信号,在38 km SSMF传输后,功率损失可忽略不计。

图14 MZI调制器截面Figure 14. MZI modulator section

由表2可知,在1 550 nm的工作波长下,调制器调制效率最大可达2 V·cm,调制器的插入损耗较低,为1.2 dB,调制速率可以达到60 Gbit·s-1,3 dB带宽高达40 GHz,最小能耗为1.03 fJ·bit-1。此外,与工作在1 550 nm波长之外的光子调制器相比,在工作波长为1 566 nm时得到较大的3 dB带宽,2 000 nm时光子调制器的插入损耗较高达到12.5 dB,1 310 nm时光子调制器的能耗则达到450 fJ·bit-1。

表2 工作在通信波长下锗硅PN电光调制器Table 2. SiGe PN electro-optic modulator operating at communication wavelength

通过对不同结构的PN结,改变掺杂浓度、波导区宽度以及Ge含量等参数进行仿真。上述新型锯齿形PN结,通过增大PN结接触面积提高波导区载流子浓度。图9、图12和图14采用对称PN结结构,通过改变波导宽度、波导区到有源区宽度和重掺杂的位置,通过仿真得到最佳数据参数。图13通过在波导区顶部添加P型应变SiGe层,改变Ge含量,通过ISE-TCAD进行仿真,在Ge含量为40%时,可以显著提高调制器的调制性能。

3 基于量子阱的调制器

Ge/SiGe MQWs中的量子限制斯塔克效应(QCSE)被认为是获得IV族光调制器的有效机制之一。由于在量子限制斯塔克效应下Ge/SiGe量子阱直接间隙变强,因此对Ge/SiGe量子阱进行了广泛研究[36]。

文献[36]提出了对Ge/Si0.15Ge0.85多量子阱进行了光电流和透射光谱测量,使用TM和TE偏振光从其重空穴带(HH)和轻空穴带(LH)相关跃迁进行了比较研究。结果表明,Ge量子阱的直接跃迁与III-V族量子阱都表现出较强的依赖性。

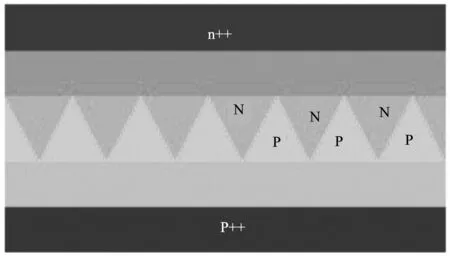

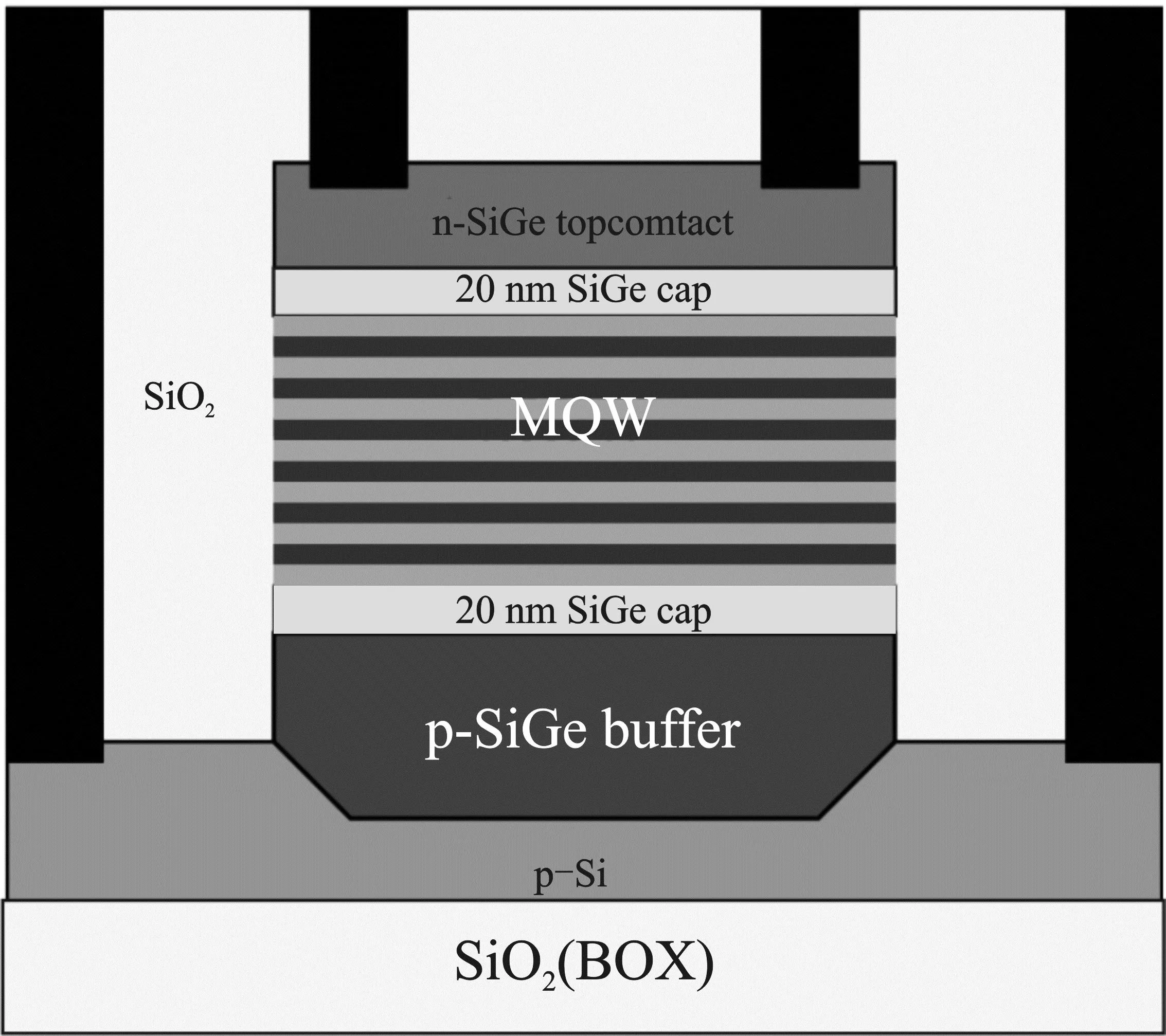

文献[37]演示了一种基于量子限制斯塔克效应的电吸收调制器,该调制器集成在厚度为220 nm的硅光子平台上。图15为调制器的截面,器件采用垂直PIN结构,SiGe多量子阱生长在150 nm厚的应变SiGe缓冲层,器件在1 335~1 365 nm的波长范围下工作。实验表明,在1 350 nm波长下,当驱动电压为1 V时,该器件的消光比为8 dB。

图15 Si量子阱调制器Figure 15. Si quantum well modulator

文献[45]演示了Ge/SiGe的标准阱和对称耦合量子阱结构。通过对平面波导的光传输测量,对硅生长的标准Ge/SiGe量子阱和耦合Ge/SiGe量子阱结构的电折射进行分析。实验结果显示,与标准量子阱结构相比,耦合量子阱结构中电折射效应明显增强,在强电场情况下有效折射率变化大于2×10-3。

文献[46]提出了一种工作在1 310 nm波长下的氮化硅集成Ge/SiGe多量子阱光调制器。通过对氮化硅波导与Ge/SiGe多量子阱波导的模拟分析,当氮化硅波导与Ge/SiGe多量子阱波导中光模场强度最大位置相同时,耦合效率最佳,耦合损耗为1.25 dB。当氮化硅波导垂直位置偏差在±10 nm范围内时,Ge/Si0.35Ge0.65量子阱性能未变化。当垂直位置的偏差在±25 nm范围内时,耦合值远低于1.5 dB。

文献[47]演示了一种不对称的Ge/SiGe耦合量子阱调制器。器件的截面如图16所示,该调制器的有源区由两个不对称量子阱组成,通过控制耦合波函数来增强器件的光学性能。在1 V反向偏压下,器件在1 446 nm波长处具有5 dB的消光比,3 dB带宽为27 GHz。在2 V的反向偏压下,器件在1 457 nm波长处的消光比为7.8 dB,3 dB带宽为32 GHz。实验表明,当波长为1 530 nm时,在1 V和2 V反偏电压条件下,该结构的调制器分别实现1.4×10-3和3.2×10-3的电折射率变化,对应的调制效率分别为0.055 V·cm和0.024 V·cm。研究表明,通过优化Ge/SiGe耦合量子阱宽度以及增加量子阱数量可以进一步提高调制器的性能。

图16 Ge/SiGe耦合量子阱调制器Figure 16. Ge/SiGe coupled quantum well modulator

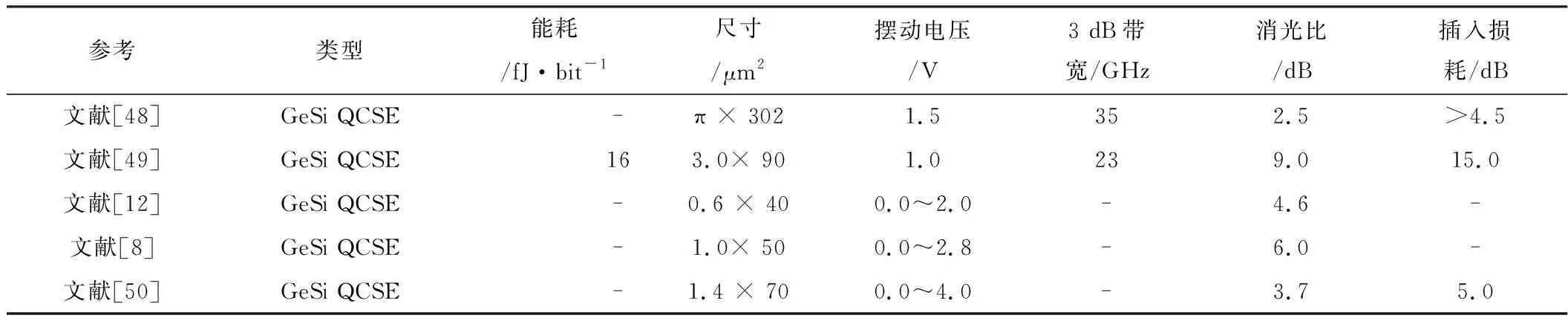

由表3可知,SiGe量子阱电吸收调制器的能耗较低可达16 fJ·bit-1,消光比高达9 dB,插入损耗为15 dB,通过对比调制器尺寸可知,在尺寸最大为π×302 μm2时,调制器的插入损耗最低为4.5 dB。在相同尺寸情况下,根据摆动电压变化得到消光比均为6 dB。基于QCSE效应的调制器的实验结果表明,在低电压下调制器性能具有的较大潜力。

表3 工作在通信波长下基于量子阱的电光调制器Table 3. Electro-optic modulator based on quantum well working at communication wavelength

4 结束语

硅光子学作为一个重要的光电集成平台,近年来取得了较大研究进展,展示了其低功耗、低成本、互补金属-氧化物-半导体(CMOS)兼容性的优势。在不同硅光子学器件中,硅电光调制器是实现电信号转换为光信号的关键有源组件,但在有机电光材料的高速调制器商业化之前,需要进行更多的研究与发展。

本文基于SiGe电光调制器对近年来调制器件的研究成果进行了综述,主要对SiGe调制行了研究与分析,对比了采用不同结构调制器的性能,讨论了PIN、PN结等电学调制结构。近年来,国内外进行了基于Ge材料、SiGe材料研究,可实现器件的高速调制以及获得更低的插入损耗,为发展高速率、低损耗的光子调制器提供了思路,也为其它光子器件的研发提供了技术参考。光子调制器作为光纤通信系统的核心器件,实现其高调制速率、低驱动电压以及低插入损耗是目前需要解决的问题。由于硅光子技术的发展,涌现出了较多高性能的调制器,而采用传统硅材料的调制器已经不能满足日益快速发展的光通信技术以及光互连技术,基于其它材料和结构的调制器将不断出现,同时,现有器件与制造工艺的兼容性也将不断提高。